Изобретение относится к вычислительной технике и может быть использовано при построении оперативных запоминающих устройств с тестовым самоконтролем.

Целью изобретения является повышение бытродействия устройства при самоконтроле.

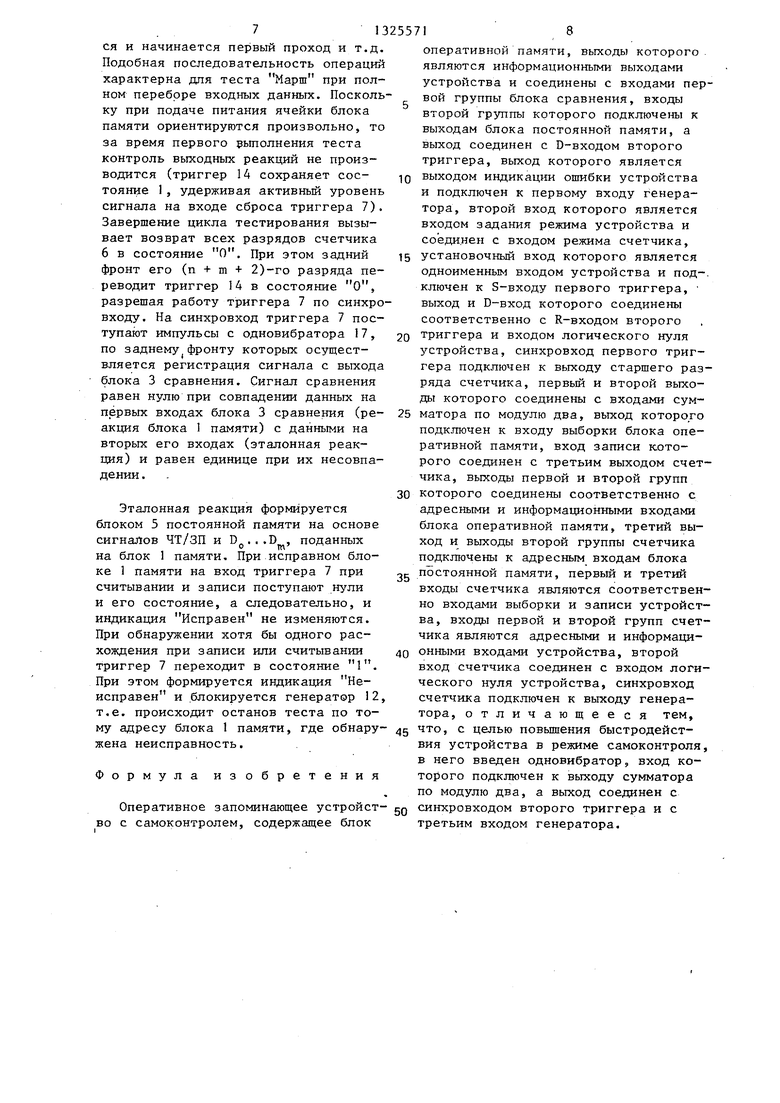

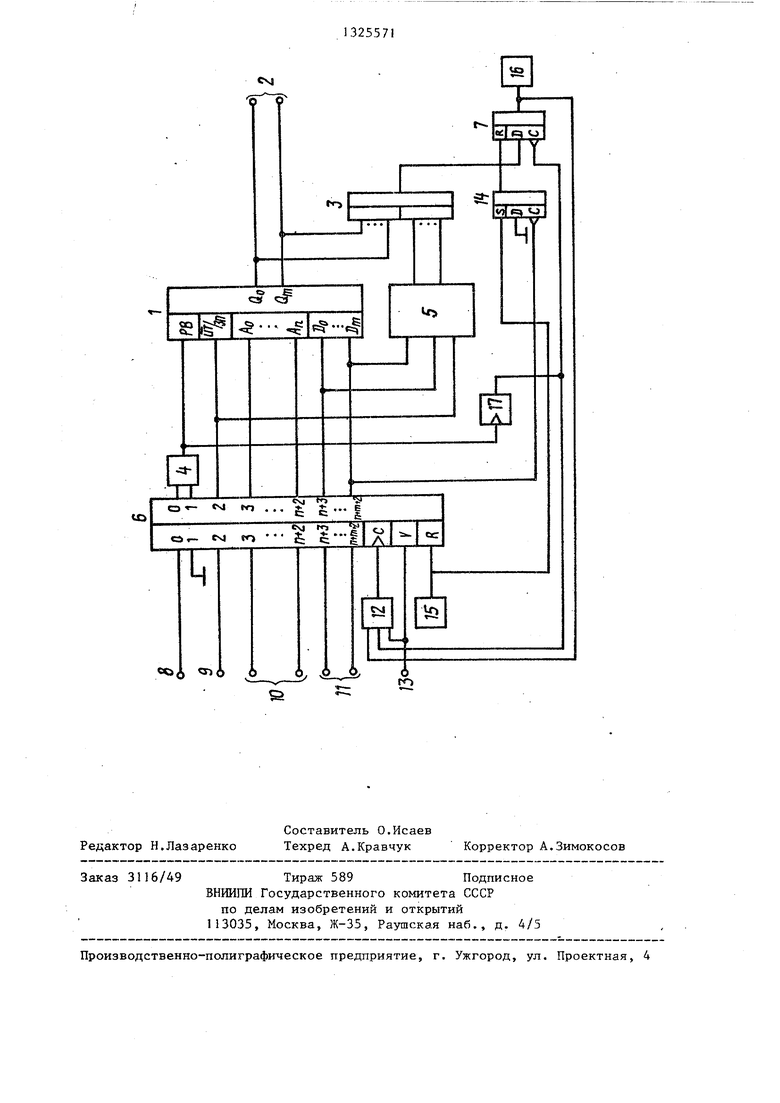

Ыа чертеже представлена схема one- IQ ных на блок 1 памяти в режиме саморативного запоминающего устройства с самоконтролем.

Устройство содержит блок 1 оперативной памяти, выходы 2 данных, блок 3 сравнения, сумматор 4 по модулю два, блок 5 постоянной памяти, счетчик 6, второй триггер 7, вход выборки 8, вход 9 записи, адресные входы 10, входь 11 данных, генератор 12, вход 13 режима, первьй триггер 14, блок 15 сброса, элемент 16 индикации одновибратор 17.

Блок 1 оперативной памяти является основным узлом устройства и обес30

печивает вьшолнение его главной функ- 25 Чтение О, Запись 1. Поскольку ции - работу в качестве оперативного запоминающего устройства.

Блок 1 памяти построен на БИС ОЗУ и имеет организацию N х М, где N - Число адресов; М - разрядность слова

данных. Выходы данных Q...Q (т М-1) блока 1 памяти являются выходами 2 данных устройства и соединены с первыми входами даных блока сравнения 3. Вход Разрешерше выборки (РВ) блока 1 памяти соединен с выходом cy tмaтopa 4 по модулю два, (Термин РВ употребляется по аналогии с соответствующим сигналом БИС ОЗУ). Зтот вход блока .памяти использует- .ся для обеспечения работы устройства в системе.

Как правило, блок оперативной памяти содержит несколько БИС ОЗУ, дая из которых управляется индивидуальным сигналом РВ, формируемым на основе дешифрации старших разрядов адреса. Вход Чтение/Запись (ЧТ/ЗП) блока 1 памяти соединен с выходом 2- го разряда счетчика 6 и управляющим входом элемента 5 постоянной памяти.

40

выходная реакция ОЗУ при операциях Разрешение записи и Запрет записи определена ее таблицей истинности, а входные сигналы данных в течение как первого, так и второго прохо дов адресного пространства поддерживаются неизменными (О и 1 соответст- вен.но) для обеспечения требуемых опе раций записи О и 1, то на основе сигналов РВ, ЧТ/ЗП и D в любой момент времени можно указать выходной сигнал исправного ОЗУ. Например, при РВ 1, ЧТ/ЗП О и Dj 1 имеет мес то выполнение операции разрешения (РВ 1) чтения (ЧТ/ЗП 0) нуля (Dg. 1), и, следовательно, выходной сигнал исправного ОЗУ должен быть О (прямой выход). При многоразрядном слове данных (М 7 1) и стимуляции входов данных при проверке последова тельными разрядами счетчика тест состоит из 22М проходов адресов, причем картина здесь аналогична, за исключенршм того, что для разрядов

50 данных D . . .D., имеет.место избыточность, заключающаяся в дополнительных операциях Чтение О, Запись О и Чтение 1, Запись 1 во всех не первых проходах адресного

45

Входы данных D...D блока 1 памяти соединены с выходами (п+3)-го - (п+ )-го разрядов счетчика бис адресными входами блока 5 постоянной памяти. Блок 3 сравнения служит для сравнения в режиме КОНТРОЛЬ выходных реакций блока памяти I и эталонных сигналов, сформированных блоком постоянной памяти 5. Вторые входы дан- нъгх: блока сравнения 3 соединены с выходами блока постоянной памяти 5. Выход блока сравнения 3 соединен с входом данных второго триггера 7. Сумматор по модулю два 4 обеспечивает разнесение во времени изменения сигнала РВ и других сигналов, поданконтроля. Входы сумматора 4 по модулю два соединены с выходами 0-го и 1-го разрядов счетчика 6. Блок 5 постоянной памяти служит для формирования эталонных выходных сигналов

блока 1 памяти в режиме проверки на основе его входных сигналов ЧТ/ЗП и .Dp . . .D. .Как известно, алгоритм теста Марш ;у1я ОЗУ с организацией

N X 1 заюхючается в двух проходах адресного пространства ОЗУ. При этом при первом проходе по каждому адресу выполняются операции Чтение 1, Запись О, а при втором проходе 0

5 Чтение О, Запись 1. Поскольку

0

выходная реакция ОЗУ при операциях Разрешение записи и Запрет записи определена ее таблицей истинности, а входные сигналы данных в течение как первого, так и второго проходов адресного пространства поддерживаются неизменными (О и 1 соответст- вен.но) для обеспечения требуемых операций записи О и 1, то на основе сигналов РВ, ЧТ/ЗП и D в любой момент времени можно указать выходной сигнал исправного ОЗУ. Например, при РВ 1, ЧТ/ЗП О и Dj 1 имеет место выполнение операции разрешения (РВ 1) чтения (ЧТ/ЗП 0) нуля (Dg. 1), и, следовательно, выходной сигнал исправного ОЗУ должен быть О (прямой выход). При многоразрядном слове данных (М 7 1) и стимуляции входов данных при проверке последовательными разрядами счетчика тест состоит из 22М проходов адресов, причем картина здесь аналогична, за исключенршм того, что для разрядов

0 данных D . . .D., имеет.место избыточность, заключающаяся в дополнительных операциях Чтение О, Запись О и Чтение 1, Запись 1 во всех не первых проходах адресного

5 пространства после смены входных данных на разряде. Поскольку на основе входных данных всегда можно определить, первый ли проход-адресного пространства выполняется после смены

5

информации на данном разряде, то и эталонная выходная реакция ОЗУ также может быть определена. Например, информация 010...1 на входах D ...D свидетельствует, что для разрядов D и D выполняется первый проход после смены на них данных, а для разрядов D ... не первый. Таким образом, для разрядов D и D ожидаемые операции будут Чтение 1, Запись О и Чтение О, Запись 1 соответственно, а для разрядов Dp и D - Чтение О, Запись О и Чтение 1, Запись 1 соответственно. В принципе,входные и выходные сигналы исправного ОЗУ при контроле связывает однозначная комбинационная функция. Использование элемента постоянной памяти позволяет сформировать эталонные сигналы независимо от таблицы истинности, реализуемой блоком 1 памяти (прямой или инверсный выход состояние выхода при операции Запись и т.п.), поскольку ПЗУ можно запрограммировать с ее учетом.

Вместе с тем, для обнаружения неисправностей блока 1 памяти, связанных с неверным функционированием БИС ОЗУ, составляющих блок 1 памяти при отсутствии сигнала Разрешение выборки, достаточно производить контроль выходных реакций блока 1 памяти лишь при активном уровне сигнала РВ (РВ 1).

При этом неизбежно выявятся неисправности, связанные с некоррективным функционированием хотя бы одной из БИС ОЗУ при отсутствии ее индиви- дуального сигнала Разрешение выборки. Например, неисправность БИС ОЗУ, обусловленная записью в нее информации при отсутствии ее индивидуального сигнала Разрешение выборки, приводит к искажению информации в какой- либо из ее ячеек при записи в параллельную БИС ОЗУ, что обязательно обнаружено при считывании информации из этой ячейки, исходя из реализуемого алгоритма теста Марш. При неисправности БИС ОЗУ, определяющейся наличием какой-либо информации на ее выходе при отсутствии ее индивидуального сигнала Разрешение выборки, она также регистрируется, так как это приводит к искажению выходных реакций параллельной БИС ОЗУ, выбранной в данный момент.

Так как контроль выходных реакций устройства производится лить при наличии сигнала Разрешение выборки, то характер информации на выходах блока 5 постоянной памяти при отсутствии сигнала Разрешение выборки значения не имеет. Поэтому блок 5 постоянной памяти формирует эталон0 Hbie реакции лишь на основе сигнала ЗП/СЧ и второй группы выходов счетчика 6. Счетчик 6 используется в двух режимах. В режиме асинхронной ус гановки по входам данных (режим

5 Работа) счетчик 6 - буфер магистральных сигналов системы и блока 1 памяти. Если последний построен на БИС ОЗУ с малыми входными токами, счетчик 6 заменяет буферные усилите-:

0 ли. При необходимости сигналы со

счетчика 6 подаются на блок 1 памяти через усилители.

В режиме счета (режим Контроль) счетчик 6 - генератор тестовых воз5 действий для блока 1 памяти. Первый вход счетчика 6 является входом (8) РВ устройства. Второй вход соединен с шиной нулевого потенциала. Третий вход счётчика 6 является входом (9)

0 Чтение/Запись устройства, а первая группа входов (3-го...п+2-го разрядов) счетчика 6 - адресными входами (10) устройства, вторая группа входов (n+3-ro...n + m + 2-го разрядов) счетчика 6 - входами (11) данных устройства. Синхровход счетчика 6 соединен с выходом генератора 12. Управляющий вход (Счет/Установка) счетчика 6 соединен с первым входом гене0 ратора 12 и является входом (13) Контроль/Работа устройства. Вход сброса счетчика 6 соединен S-входом установки первого триггера 14 и выходом блока 15 сброса. Выход старшего

5 разряда счетчика соединен с синхро- входом первого триггера 14. D-вход второго триггера 7 соединен с выходом блока 3 сравнения.

Одновибратор 17 своим входом соеQ динен с выходом сумматора А по модулю два, а выходом - с третьим входом генератора 12 и синхровходом второго триггера 7. Одновибратор 17 осуществляет торможение генератора 12 на

g время, необходимое для выборки блока 1 памяти. Это сделано потому, что частота генератора 12 намеренно выбрана повьштенной, при которой дпи- тельность такта переключения генера5

тора 12 определяется только временем полного переключения разрядов счетчика 6, при этом время между ближайшими сигналами Разрешение выборки сводится к минимуму. Подача сигнала с выхода одновибратора 17 на синхро- вход второго триггера 7 обеспечивает регистрацию выходных реакций блока памяти только в такте появления активного уровня сигнала Разрешение выборки, (в остальньпс тактах регист- рагдия выходных реакций устройства не производится). Выход второго триггера 7 соединен с входом элемента 15 индикации и вторым входом генератора 12, что обеспечивает в случае регистрации неисправности останов генератора 12 и формирование индикации. R- вход второго триггера 7 соединен с выходом первого триггера 14.

Генератор 12 формирует синхроимпульсы для Счетчика 6 при самоконтроле. Первый триггер 14 служит для блокировки работы второго триггера 7.

fO

нератор 12 и определяет работу счетчика 6 в режиме асинхронной установки по входам данных. Таким образом, сигналы РВ, ЧТ/ЗП, адреса и данные поступают с входов счетчика 6 на соответствующие его входы, что обеспечивает работу блока 1 памяти в обычном режиме, (Поскольку на входы сумматора 4 по модулю два поступают сигналы РВ и логический О, то его выход повторяет сигнал РВ). Так как генератор 12 заблокирован, то состояние триггера 7 и индикации остается неизменным. В режиме Контроль J5 логический О на входе 13 разрешает работу генератора и определяет работу счетчика. 6 в режиме непрерывного пересчета (генератор 12 работает в автоколебательном режиме). При этом состояние счетчика 6 изменяется независимо от сигналов на его входах данных. Поскольку стимуляция адресных входов блока 1 памяти осзпцествляется разрядами счетчика 6, начиная с 3-го,

20

при первом вьтолнении теста. Это свя- 25 то длительность обращения к каждому зано с тем, что при подаче питания адресу составляет 8 тактов синхросиг- оперативная память ориентируется про- нала генератора 12 (состояние счетчи- извольно и, независимо от начапьной ка изменяется по переднег у фронту установки счетчика 6, может иметь на асинхроимпульса). В течение первых выходе неверную реакцию. После перво 30 четырех тактов осуществляется опера- го,- выполнения теста все ячейки памяти ция Чтение, а в течение вторых устанавливаются в однозначное состояние. Вход данных триггера 14 соединен с общей шиной устройства, а его ° синхровход ,- с выходом последнего разряда 6, Блок 15 сброса (напримерj RC-цепь) обеспечивает сигналы начапьной установки для счетчика 6 и триггера 4 при подаче питания. Элемент 16 индикации (например, светодиод) служит для визуального отображения результатов самоконтроля. Следует отметить, что при необходимости согласования активных уровней на линиях РВ и ЧТ/ЗП могут дополнительно использоваться инверторы (возможно уп-- равляемые).

Устройство работает следующим образом.

При подаче питания импульс с блока 15 сброса устанавливает счетчик 6 в нуль и первый триггер 14 в единицу. Последнее вызывает сброс второго триггера 7 и формирование индикации Исправно. Дальнейшая работа определяется сигналом на входе 13 Контроль/Работа. В релшме Работа логическая I на входе 13 блокирует ге

нератор 12 и определяет работу счетчика 6 в режиме асинхронной установки по входам данных. Таким образом, сигналы РВ, ЧТ/ЗП, адреса и данные поступают с входов счетчика 6 на соответствующие его входы, что обеспечивает работу блока 1 памяти в обычном режиме, (Поскольку на входы сумматора 4 по модулю два поступают сигналы РВ и логический О, то его выход повторяет сигнал РВ). Так как генератор 12 заблокирован, то состояние триггера 7 и индикации остается неизменным. В режиме Контроль 5 логический О на входе 13 разрешает работу генератора и определяет работу счетчика. 6 в режиме непрерывного пересчета (генератор 12 работает в автоколебательном режиме). При этом состояние счетчика 6 изменяется независимо от сигналов на его входах данных. Поскольку стимуляция адресных входов блока 1 памяти осзпцествляется разрядами счетчика 6, начиная с 3-го,

0

Запись. Внутрь каждой четырехтактной операции вложен двухтактный сигнал РВ (обеспечивается сумматором 4

35 по модулю два), который принимает активный уровень при неизменных ocTajibiibix сигналах, поданных на блок 1 памяти (тем самым достигается корректная временная диаграмма). При

40 появлении активного уровня сигнала РВ одновибратор 17 вырабатывает импульс, в течение которого осуществляется блокировка генератора 12, а следовательно, и счетчика 6, т.е.

45 происходит увеличение .длительности данного такта генератора 12 - второго из четырех, отведенных на вьтол- нение операций Чтение или Запись на время импульса одновибратора 17,

50 которое выбирается не менее времени выборки оперативной памяти. Увеличение длительности остальных трех тактов генератора 12 при отработке четырехтактных операций Запись и,пи

55 Чтение не происходит.

Проход адресного пространства осуществляется при неизменных входных данных, после чего они изменяются и начинается первый проход и т.д. Подобная последовательность операций характерна дпя теста Марш при полном переборе входных данных. Поскольку при подаче питания ячейки блока памяти ориентируются произвольно, то за время первого рьтолнения теста контроль выходных реакций не производится (триггер 14 сохраняет состояние 1, удерживая активный уровень сигнала на входе сброса триггера 7). Завершение цикла тестирования вызывает возврат всех разрядов счетчика 6 в состояние О. При этом задний фронт его (п + m + 2)-го разряда переводит триггер 14 в состояние О, разрешая работу триггера 7 по синхро- входу. На синхровход триггера 7 поступают импульсы с одновибратора 17, по заднему фронту которых осуществляется регистрация сигнала с выхода блока 3 сравнения. Сигнал сравнения равен нулю при совпадении данных на первых входах блока 3 сравнения (реакция блока 1 памяти) с данными на вторых его входах (эталонная реакция) и равен единице при их несовпадении .

Эталонная реакция формируется блоком 5 постоянной памяти на основе сигналов ЧТ/ЗП и D.-.D, поданных на блок 1 памяти. При исправном блоке 1 памяти на вход триггера 7 при считывании и записи поступают нули и его состояние, а следовательно, и индикация Исправен не изменяются. При обнаружении хотя бы одного расхождения при записи или считывании триггер 7 переходит в состояние 1. При этом формируется индикация Неисправен и блокируется генератор 12, т.е. происходит останов теста по тому адресу блока 1 памяти, где обнаружена неисправность.

Формула изобретения

Оперативное запоминающее устройство с самоконтролем, содержащее блок

оперативной памяти, выходы которого, являются информационными выходами устройства и соединены с входами первой группы блока сравнения, входы второй группы которого подключены к выходам блока постоянной памяти, а выход соединен с D-входом второго триггера, выход которого является

Q выходом индикации ошибки устройства и подключен к первому входу генератора, второй вход которого является входом задания режима устройства и соединен с входом режима счетчика,

5 установочный вход которого является одноименным входом устройства и под-. ключен к S-входу первого триггера, выход и D-вход которого соединены соответственно с R-входом второго

0 триггера и входом логического нуля устройства, синхровход первого триггера подключен к выходу старшего разряда счетчика, первьй и второй выходы которого соединены с входами сум5 матора по модулю два, выход которого подключен к входу выборки блока оперативной памяти, вход записи которого соединен с третьим выходом счетчика, выходы первой и второй групп

0 которого соединены соответственно с адресными и информационными входами блока оперативной памяти, третий выход и выходы второй группы счетчика подключены к адресным входам блока

С постоянной памяти, первый и третий входы счетчика являются соответственно входами выборки и записи устройства, входы первой и второй групп счетчика являются адресными и информаци0 онными входами устройства, второй

вход счетчика соединен с входом логического нуля устройства, синхровход счетчика подключен к выходу генератора, отличающееся тем,

5 что, с целью повышения быстродействия устройства в режиме самоконтроля, в него введен одновибратор, вход которого подключен к выходу сумматора по модулю два, а выход соединен с

Q синхровходом второго триггера и с третьим входом генератора.

Редактор Н.Лазаренко

Составитель О.Исаев Техред А.Кравчук

Заказ 3116/49Тираж 589Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор А.Зимокосов

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1413676A1 |

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1406640A1 |

| Оперативное запоминающее устройство с самоконтролем | 1984 |

|

SU1229826A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

| Оперативное запоминающее устройство с самоконтролем | 1988 |

|

SU1647655A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1988 |

|

SU1529236A1 |

| Блок буферной памяти для терминального устройства | 1989 |

|

SU1633454A1 |

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении оперативных запоминающих устройств с тестовым самоконтролем. Целью изобретения является повышение быстродействия устройства при самоконтроле. Устройство содержит блоки оперативной и постоянной памяти, счетчик, блок сравнения, генератор, одновибратор, сумматор по модулю два, первый и второй триггеры. Увеличение быстродействия устройства в режиме самоконтроля достигается за счет управления длительностью тактов генератора в зависимости от состоя- .ния сигнала разрежения выборки в каждом такте. 1 ил. с (Л ел

| Электронная техника | |||

| Сер.З Микроэлектроника, 1983, вып | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Счетная таблица | 1919 |

|

SU104A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Оперативное запоминающее устройство с самоконтролем | 1984 |

|

SU1229826A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-07-23—Публикация

1986-03-10—Подача