Изобретение относится к автоматике и вычислительной технике и может быть использовано для функционального контроля больших интегральных схем оперативной памяти.

Цель изобретения - упрощение устройства.

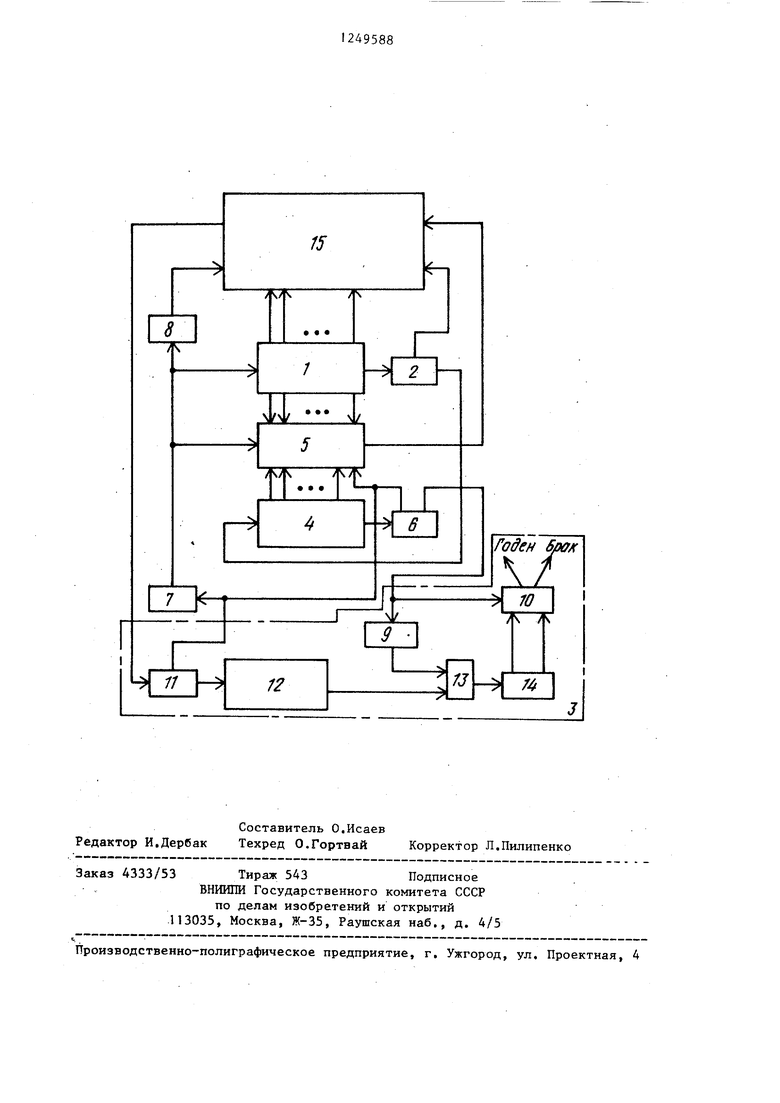

На чертеже представлена схема устройства для контроля интегральных микросхем оперативной памяти.

Устройство содержит счетчик 1 адреса, триггер 2 записи-чтения, блок

3контроля, счетчик 4 кадров, блок

5 сравнения, триггер 6 останова, генератор 7 и формирователь 8 сигналов выборки.

Блок 3 контроля содержит одновиб- ратор 9, блок 10 индикации, управляемый инвертор 11, счетчик 12 результата, элемент И 13 и триггер 14 ин- дикации. Также показано подключение проверяемой микросхемьт 15 к устройству.

Устройство для контроля интегральных микросхем оперативной памяти работает следующим образом.

Блок 5 сравнения осуществляет поразрядное сравнение состояния счетчика 1 адреса и счетчика 4 кадров. Результат сравнения записывается в проверяемую микросхему 15 по адресу, определяемому счетчиком 1 адреса.

Импульс с генератора 7 передним фронтом стробирует блок 5 сравнения, единица на счетчик 1 адреса добавляется по его заднему фронту, вследствие чего сначала происходит сравнение состояния счетчика 1 адреса и счетчика 4 кадров, а затем появляетс

новый адрес. I

В начале работы оба счетчика 1 и

4обнулены. Б результате сравнения их состояния блок 5 сравнения выдает логическую единицу, которая записывается в испытуемую микросхему 15 по нулевому адресу, В дальнейшем, по мере поступления импульсов с генератора 7, постоянно имеет место несравнение и по всем адресам в проверяемую микросхему 15 записываются нули. Импульс переполнения счетчика 1 адреса опрокидьгаает триггер 2 записи- чтения, состояние которого определяет режим работы микросхемы 15 памяти Далее происходит считьшание информации по всем адресам. Единственная е;а;иница, записанная в проверяемую микросхему 15 в результате данного кад

ра, заносится через управляемый инвертор 11 в счетчик 12 результата, В первом цикле информация проходит через управляемый инвертор 11, не меняя своего вида. В момент окончания чтения в результате обратного опрокидывания триггера 2 записи-чтения 2 в счетчик кадров 4 записывается единица. При повторной записи информация отличается от записанной в предыдущем кадре. Так как в счетчик 4 кадров занесена единица, момент сравнения происходит не при нулевом адресе, а при первом.

Таким образом, при каждом новом кадре записи информации адрес записываемой единицы последовательно увеличивается до 2 -1. После последнего кадра записи-считьтания импульсов переполнения счетчика 4 кадров опрокидывается триггер 6 останова.

Под воздействием сигнала с триггера 6 останова блок 5 сравнения выдает информацию, инверсную по отно- шению к той,.которая выдается в первом цикле и которая записана в проверяемую микросхему 15,

При каждом кадре работы устройства, при записи информации по 2 адресам в микросхему 15 записывается одна единица и нулей, В процессе проверки микросхемы по первому циклу считывается информация в 7. кадров и, следовательно, в счетчик 12 результата в случае проверки исправной микросхемы поступает точно 2 единиц. Во втором цикле работы сигнал с выхода триггера 6 остано7 ва переводит управляемый инвертор 8 в режим инвертирования. Вследствие этого информация, поступающая на счетчик 12 результата, точно такая же, как и в первом цикле. Счетчик 12 результата должен иметь п+1 разряд. В этом случае при прохождении двух циклов работы в случае контроля исправной микросхемы 15 па вход счетчика 12 результата поступает 2 импульсов, он обнуляется и выдает сигнал переполнения.

В устройстве индикация Годен загорается лишь в случае, если к моменту окончания второго цикла работы на счетчик 12 результата поступает точно 2 Импульсов. Если к этому моменту на счетчик 12 результата поступает импульсов больше или меньше, чем 2 то загорается индикация

Брак. Это достигается тем, что в момент окончания второго цикла триггер 6 останова опрокидывается в начальное состояние, что приводит к остановке генератора 7 и запуску од- новибратора 9,

На элемент И 13 поступает импульс переполнения с выхода, счетчика 12 результата, который оказывается внутри временного интервала, занимаемым импульсом с одновибратора 9 (случай проверки исправной микросхемы). Поступая.на вход Установка в 1 триггера 14 индикации, импульс с выхода элемента И 13 опрокидывает его в состояние Годен, которое тут же индицируется блоком 10 индикации.

Если проводится контроль дефектной микросхемы 15 и число импульсов за время отработки полного цикла ,

n-f4

проверки окажется меньше, чем 2 , то к тому времени, когда появится импульс с одновибратора 9, импульс с выхода счетчика 12 результата от- сутствует, триггер 14 индикации остается в начальном состоянии, которое по сигналу с триггера 6 останова индицируется, как Брак,

Если дефектная микросхема по какой-либо причине выдает за время полного цикла проверки больше импульсов чем 2 то импульс переполнения счетчика 12 результата появляется раньше, чем импульс с одновибратора 9, триггер индикации 14 не опрокидывается и индицируется состояние

Брак.

Формула изобретения

Устройство дпя контроля интегральных микросхем оперативной памяти, содержащее блок контроля, первый вход которого является информационным входом устройства, генератор, вход которого соединен с одним выходом триггера останова, а выход подключен к входу формирователя сигналов выборки, выход которого является первым управлякядим выходом устройства, триггер записи-чтения, один выход которого является вторым управляющим выходом устройства, счетчик адреса, выходы которого являются адресными выходами устройства, а выходы группы соединены с входами первой группы блока сравнения, входы второй группы KOTopord подключены к выходам группы счетчика кадра, о т- личающееся тем, что, с целью его упрощения, вход счетчика адреса и первый вход блока сравнения подключены к выходу генератора, выход счетчика адреса соединен с входом триггера записи-чтения, другой выход которого подключен к входу счетчика кадров, выход которого соеди- нен с входом триггера останова, один выход которого подключен к второму входу блока сравнения и к второму входу блока контроля, а другой выход соединен с третьим входом блока контроля, выход блока контроля является информационным выходом устройства.

Составитель О.Исаев Редактор И.Дербак Техред О.Гортвай Корректор Л.Пилипенко

Заказ 4333/53 Тираж 543Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий .113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков памяти | 1985 |

|

SU1251187A1 |

| Устройство для контроля одноразрядных блоков памяти | 1988 |

|

SU1640743A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Устройство для формирования теста оперативной памяти | 1986 |

|

SU1425789A1 |

| Устройство для контроля оперативной памяти | 1991 |

|

SU1833919A1 |

| Устройство для контроля полупроводниковой оперативной памяти | 1982 |

|

SU1051586A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство для контроля записи информации в программируемые блоки памяти | 1983 |

|

SU1104589A1 |

| Устройство для контроля интегральных микросхем памяти | 1983 |

|

SU1144154A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для функционального контроля больших интегральных схем оперативной памяти. Цепью изобретения является упрощение устройства. Устройство содержит счетчик адреса, триггер записи-чтения, блок контроля, счетчик кадров, блок сравнения, триггер останова, генератор и формирователь сигналов выборки. Выходы счетчика адреса и счетчика кадров соединены cJвxoдaми блока срав- нения, выход которого является информационным выходом устройства, В устройстве обеспечивается проверка правильности чтения единицы (нуля) на фоне всех нулей (единиц) для каждой ячейки проверяемой интегральной микросхемы памяти. 1 ил. О)

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Разработка полупроводниковых оперативных запоминающих устройств и пульта для их контроля и наладки | |||

| Отчет МЭИ | |||

| / Руководитель работы Ю.Н.Шанаев | |||

| № гос | |||

| Способ обработки боковых поверхностей шпал различного радиуса кривизны | 1947 |

|

SU87254A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Говорящий кинематограф | 1920 |

|

SU111A1 |

Авторы

Даты

1986-08-07—Публикация

1984-05-30—Подача