ИзЪбретение относится к измерительной технике и может быть использовано для уменьшения погрешности преобразователей с квантованием преобразуемого сигнала.

Целью изобретения является умень- щение погрешности преобразования.

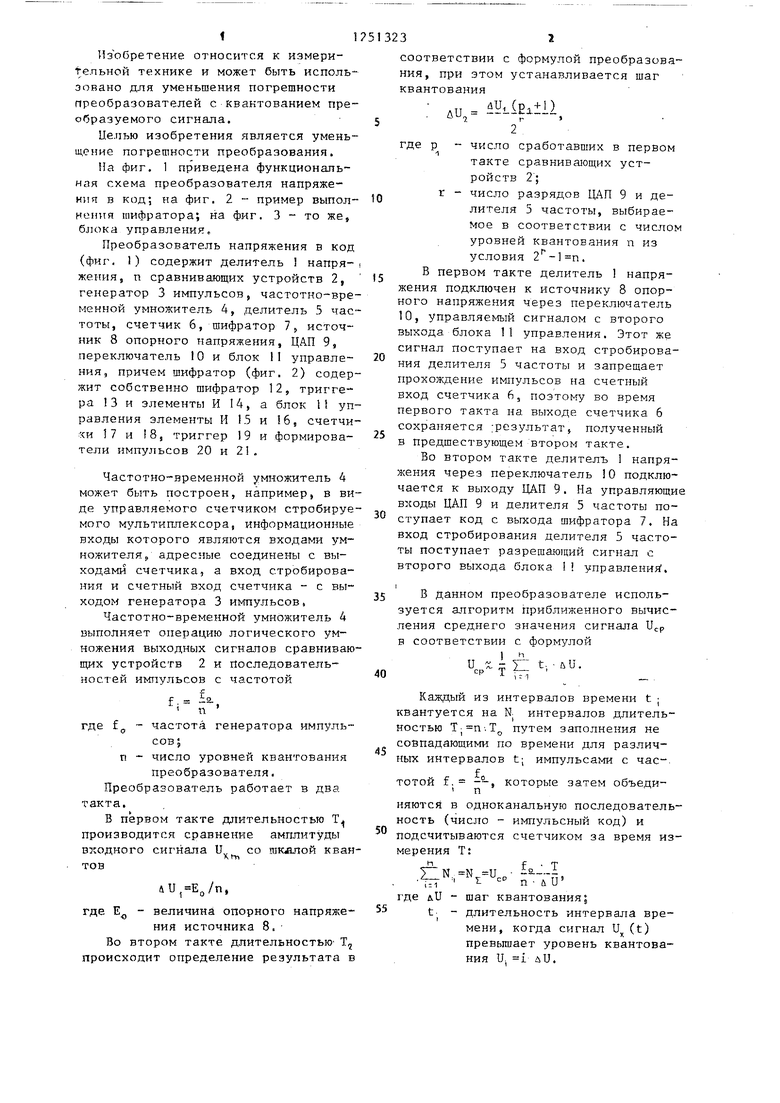

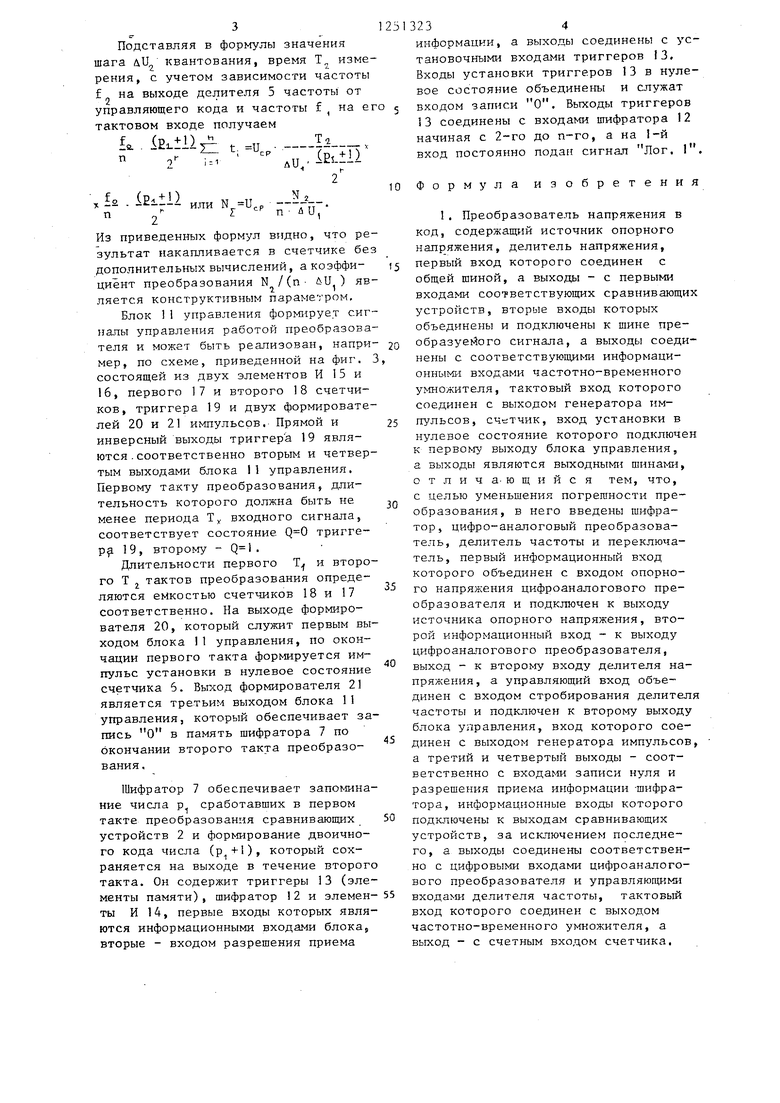

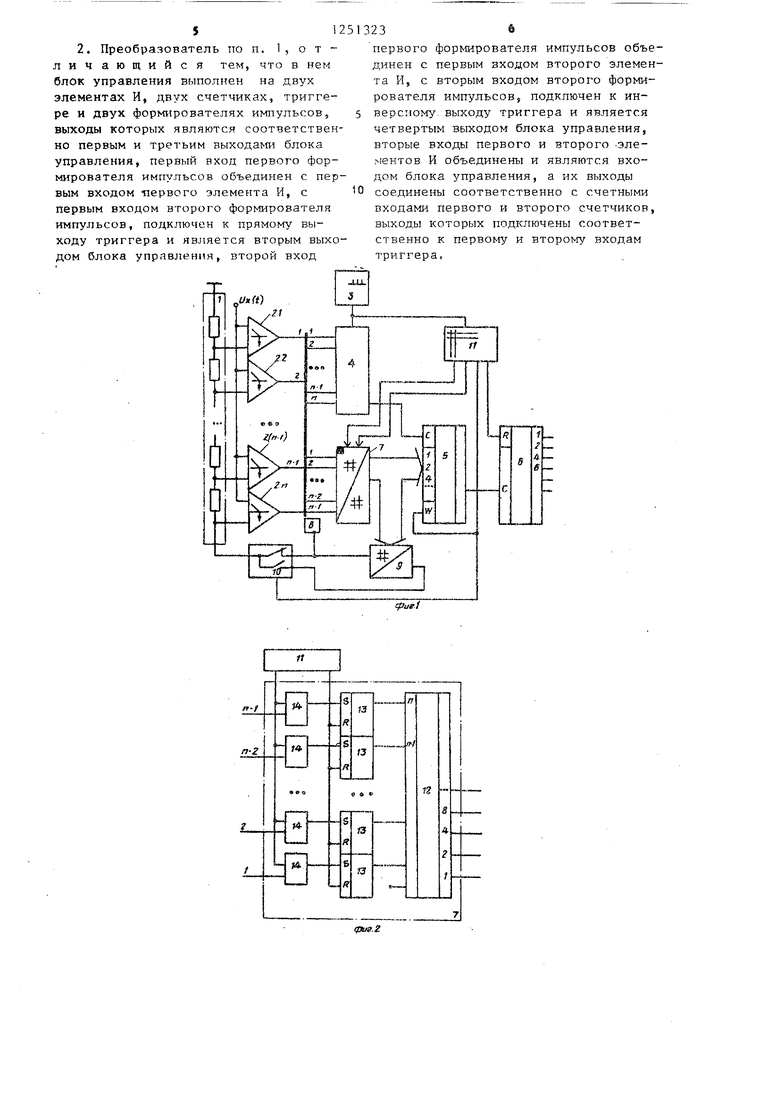

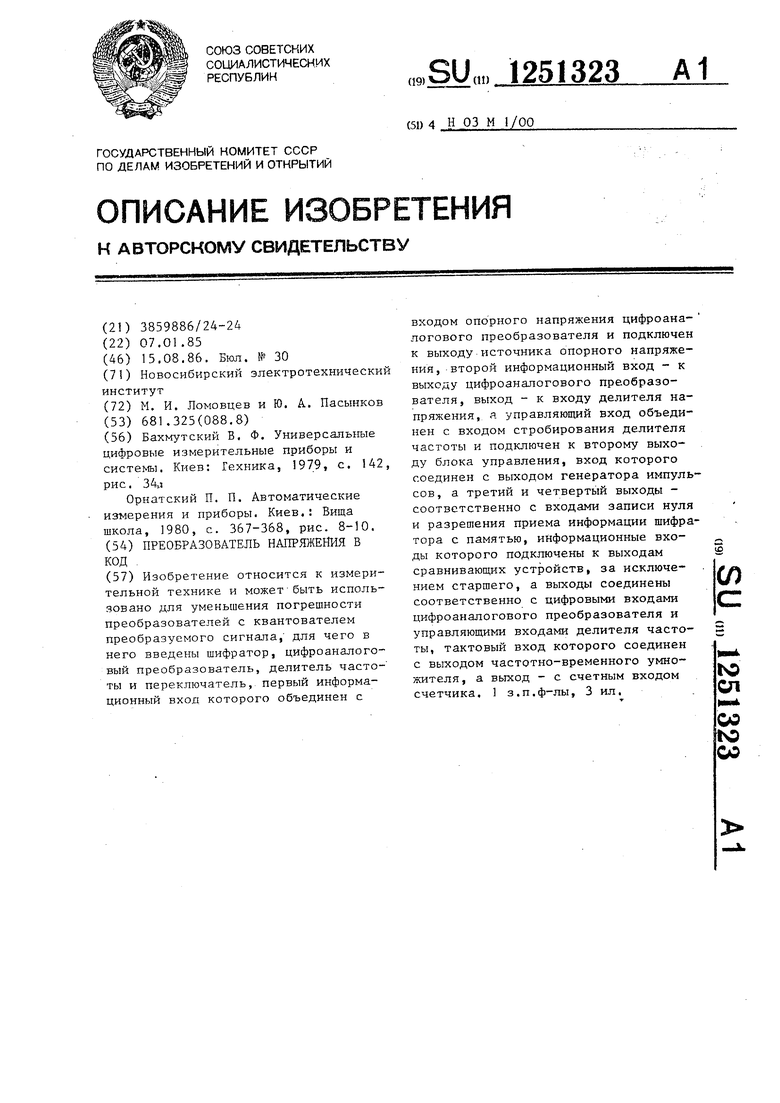

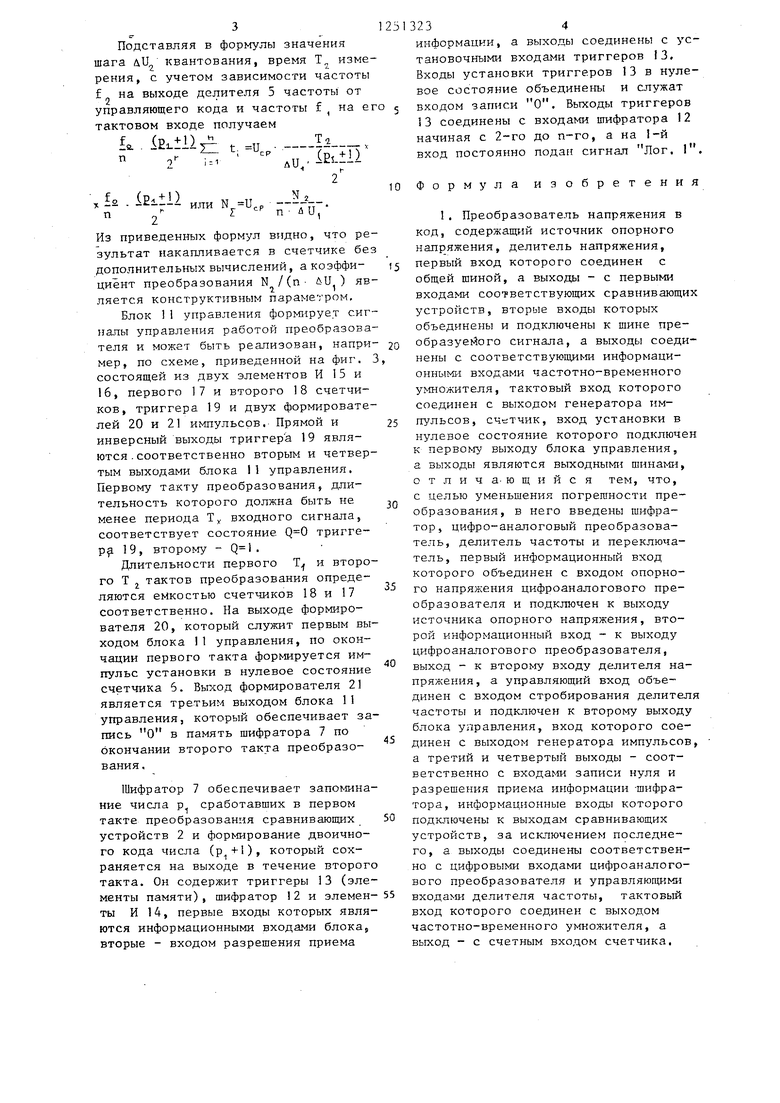

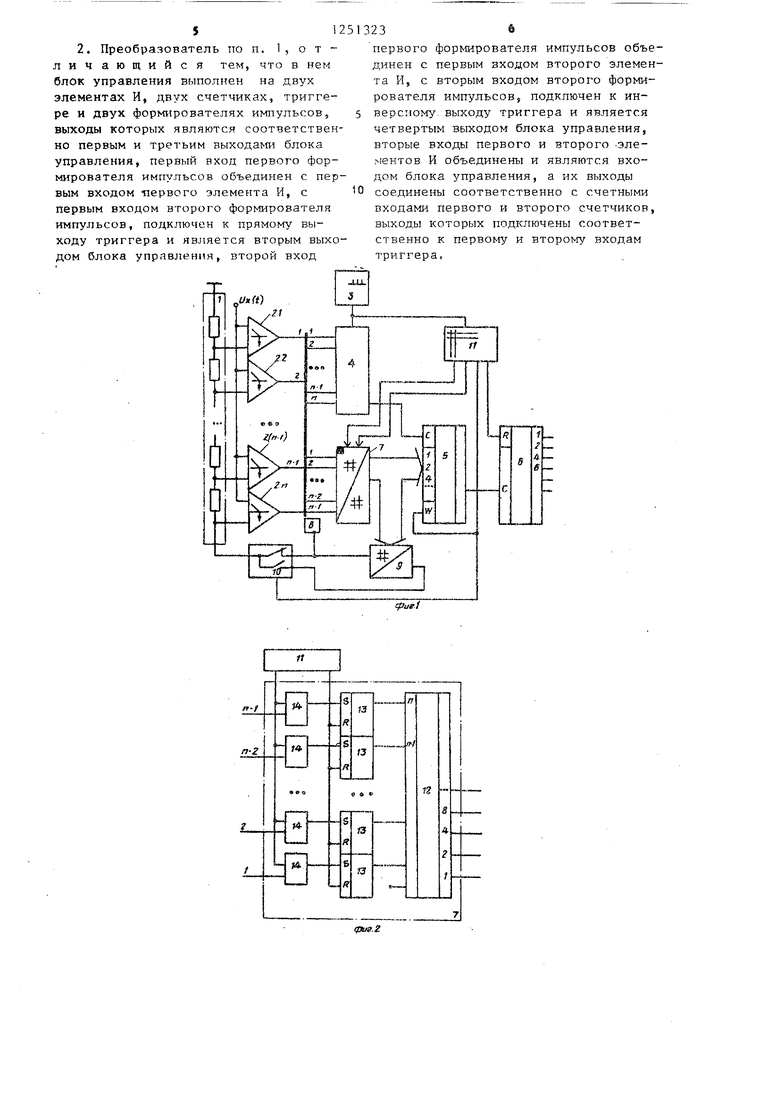

На фиг. 1 приведена функциональная схема преобразователя напряжения в код; на фиг. 2 - пример выпол- немття шифратора; на фиг. 3 - то же, блока управления.

Преобразователь напряжения в код (фиг. 1) содержит делитель 1 напряжения, п сравнивающих устройств 2, генератор 3 импульсов, частотно-временной умножитель 4, делитель 5 частоты, счетчик 6, шифратор 7, источник 8 опорного напряжения, ЦАП 9, переключатель 10 и блок 11 управле- ния, причем шифратор (фиг. 2) содержит собственно шифратор 12, триггера 1 3 и элементы И 14, а блок 11 управления элементы И 15 и 6, счетчики 17 и 8, триггер 19 и формирова- тели импульсов 20 и 2,

Частотно-временной умножитель 4 может быть построен, например, в виде управляемого счетчиком стробируе- мого мультиплексора, информационные входы которого являются входами умножителя р адресные соединены с выходами счетчика, а вход стробирова- ния и счетный вход счетчика - с выходом генератора 3 импульсов,

Частотно-временной умножитель 4 выполняет операцию логического умножения выходных сигналов сравнивающих устройств 2 и последовательностей импульсов с частотой

f ia. п

где

fa

частота генератора импульсов;п - число уровней квантования

преобразователя. Преобразователь работает в два такта.

В первом такте длительностью Т производится сравнение амплитуды входного сигнала U со гаклопой кванX tTi

ТОН

ли E,/n,

где Е - величина опорного напряжения источника 8. Во втором такте длительностью Т происходит определение результата в

0 5

0

5

0

5

0

55

ди.

соответствии с формулой преобразования, при этом устанавливается шаг квантования

UL CEi.il)

г

2

где р - число сработавших в первом такте сравнивающих устройств 2;

г - число разрядов ЦАП 9 и делителя 5 частоты, выбираемое в соответствии с числом уровней квантования п из условия .

В первом такте делитель 1 напряжения подключен к источнику 8 опорного напряжения через переключатель 10J управляемый сигналом с второго выхода блока П управления. Этот же сигнал поступает на вход стробирова- ния делителя 5 частоты и запрещает прохождение импульсов на счетный вход счетчика 6, поэтому во время первого такта на выходе счетчика 6 сохраняется :результат, полученный в предшествующем втором такте.

Во втором такте делитель 1 напряжения через переключатель 10 подключается к выходу ЦАП 9. На управляющие входы ЦАП 9 и делителя 5 частоты поступает код с выхода шифратора 7. На вход стробирования делителя 5 частоты поступает разрешающий сигнал с второго выхода блока 1 управления .

В Данном преобразователе используется алгоритм приближенного вычисления среднего значения сигнала в соответствии с формулой

1 т

и X ;; Ц t; uU. ср Т fr:f

Каждый из интервалов времени t j квантуется на N интервалов длительностью . Т путем заполнения не совпадающими по времени для различных интервалов t; импульсами с частотой f, - --, которые затем объеди- п

няются в одноканальную последовательность (число - импульсный код) и подсчитываются счетчиком за время измерения Т:

.,

f т

о.i

j,i - - n uU где iU - шаг квантования;

t - длительность интервала времени, когда сигнал U (t) превьппает уровень квантования U; i uU.

Подставляя в формулы значения шага ли квантования, время Т„ измерения, с учетом зависимости частоты f на выходе делителя 5 частоты от управляющего кода и частоты f на ег тактовом входе получаем

()

П л - :k

t. u,

Та

- (EZii) 2

,f. .() „,™ „ -Ь,,-.

п ли,

2 .. - , Из приведенных формул видно, что результат накапливается в счетчике бе дополнительных вычислений, акоэффи- циёнт преобразования N /(п- U ) является конструктивным параметром.

Блок 11 управления формирует сиг палы управления работой преобразователя и может быть реализован, напри мер, по схеме, приведенной на фиг, состоящей из двух элементов И 15 и 16, первого 17 и второго 18 счетчиков, триггера 19 и двух формирователей 20 и 21 импульсов. Прямой и инверсный выходы триггер а 19 являются .соответственно вторым и четвертым выходами блока 11 управления. Первому такту преобразования, длительность которого должна быть не менее периода Т. входного сигнала, соответствует состояние триггеру 19, второму - ,

Длительности первого Т и второго Т , тактов преобразования определяются емкостью счетчиков 18 и 17 соответственно. На выходе формирователя 20, который служит первым выходом блока 11 управления, по окон- чадии первого такта формируется импульс установки в нулевое состояние счетчика 5. Выход формирователя 21 является третьим выходом блока 11 управления, который обеспечивает запись О в память шифратора 7 по окончании второго такта преобразования.

Шифратор 7 обеспечивает запоминание числа р сработавших в первом такте преобразования сравниваюш11х устройств 2 и формирование двоичного кода числа (р +1), который сохраняется на выходе в течение второго такта. Он содержит триггеры 13 (элементы памяти), шифратор 12 и элемен- ты И 14, первые входы которых являются информационными входами блока, вторые - входом разрешения приема

3234

информации, a выходы соединены с установочными входами триггеров 13, Входы установки триггеров I3 в нулевое состояние объединены и служат входом записи О. Выходы триггеров 3 соединены с входами шифратора 12 начиная с до п-го, а на 1-й вход постоянно подан сигнал Лог, 1.

Формула изобретения

15

20 25 Q

0

5

0

1, Преобразователь напряжения в код, содержащий источник опорного напр яжения, делитель напряжения, первый вход которого соединен с общей шиной, а выходы - с первыми входами соответствующих сравнивающих устройств, вторые входы которых объединены и подключены к шине пре- образуейого сигнала, а выходы соединены с соответствующими информационными входами частотно-временного у шожителя, тактовый вход которого соединен с выходом генератора импульсов, счетчик, вход установки в нулевое состояние которого подключен к первому выходу блока управления, а выходы являются выходными шинами, о т л и ч а- ю щ и и с я тем, что, с целью уменьшения погрешности преобразования, в него введены шифратор, цифро-аналоговый преобразователь, делитель частоты и переключатель, первый информационный вход которого объединен с входом опорного напряжения цифроаналогового преобразователя и подключен к выходу источника опорного напряжения, второй информационный вход - к выходу цифроаналогового преобразователя, выход - к второму входу делителя напряжения, а управляющий вход объединен с входом стробирования делителя частоты и подключен к второму выходу блока управления, вход которого соединен с выходом генератора импульсов, а третий и четвертый выходы - соответственно с входами записи нуля и разрешения приема информации -шифратора, информационные входы которого подключены к выходам сравнивающих устройств, за исключением последнего, а выходы соединены соответственно с цифровыми входами цифроаналогового преобразователя и управляющими входами делителя частоты, тактовый вход которого соединен с выходом частотно-временного умножителя, а выход - с счетным входом счетчика.

2. Преобразователь по п. 1, о т - личающийся тем, что в нем блок управления выполнен на двух элементах И, двух счетчиках, триггере и двух формирователях импульсов, выходы которых являются соответственно первым и третьим выходами блока управления, первый вход первого формирователя импульсов объединен с первым входом -первого элемента И, с первым входом второго формирователя импульсов, подключен к прямому выходу триггера и является вторым выходом блока управления, второй вход

первого формирователя импульсов объединен с первым входом второго элемента И, с вторым входом второго формирователя импульсов, подключен к инверсному, выходу триггера и является четвертым выходом блока управления, вторые входы первого и второго -элементов И объединены и являются входом блока управления, а их выходы соединены соответственно с счетными входами первого и второго счетчиков, выходы которых подключены соответственно к первому и второму входам триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1562971A1 |

| Цифровой электромагнитный толщиномер | 1988 |

|

SU1839228A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1339890A1 |

| Дельта-кодер | 1989 |

|

SU1612375A1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

| Устройство для измерения параметров радиоимпульсов | 1980 |

|

SU938206A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1730722A2 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ ПОМЕХ | 1990 |

|

RU2074516C1 |

Изобретение относится к измерительной технике и может быть использовано для уменьшения погрешности преобразователей с квантователем преобразуемого сигнала, для чего в него введены шифратор, цифроаналого- вый преобразователь, делитель часто- ты и переключатель, первый информационный вход которого объединен с входом опорного напряжения цифроана- логового преобразователя и подключен к выходу источника опорного напряжения, второй информационный вход - к выходу цифроаналогового преобразователя, выход - к входу делителя напряжения, а управляющий вход объединен с входом стробирования делителя частоты и подключен к второму выходу блока управления, вход которого соединен с выходом генератора импульсов, а третий и четвертый выходы - соответственно с входами записи нуля и разрешения приема информации шифратора с памятью, информационные входы которого подключены к выходам сравнивающих устройств, за исключением старшего, а выходы соединены соответственно с цифровыми входами цифроаналогового преобразователя и управляющими входами делителя частоты, тактовый вход которого соединен с выходом частотно-временного умножителя, а выход - с счетным входом счетчика, 1 з.п.ф-лы, 3 ил. сл Ю ел со tsD СО

Редактор Н. Слободяник

Заказ 4426/58Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

1роизводственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Составитель В. Махнанов

Техред Л.Сердюкова КорректорЕ. Сирохман

| Бахмутский В | |||

| Ф | |||

| Универсальные цифровые измерительные приборы и системы | |||

| Киев: Техника, 1979, с | |||

| Рогульчатое веретено | 1922 |

|

SU142A1 |

| Нивелир для отсчетов без перемещения наблюдателя при нивелировании из средины | 1921 |

|

SU34A1 |

| П | |||

| Автоматические измерения и нрнборы | |||

| Киев.: Вища школа, 1980, с | |||

| Способ отковки в штампах заготовок для спиральных сверл | 1921 |

|

SU367A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1986-08-15—Публикация

1985-01-07—Подача