Изобретение относится к аптоматике и вычислительной технике и может быть использовано для контроля выходных уровней цифровых блогсов, модулей и микросхем.

Цель изобретения расширение функциональных возможностей устройства за счет обеспечения возможности выявления отрицательных уровней и уров- HEv, превышающих уровень логической единицы на выходах цифровых объектов и за счет обеспечения автоматического контроля выходных уровней сравнением с эталонными уровнями.

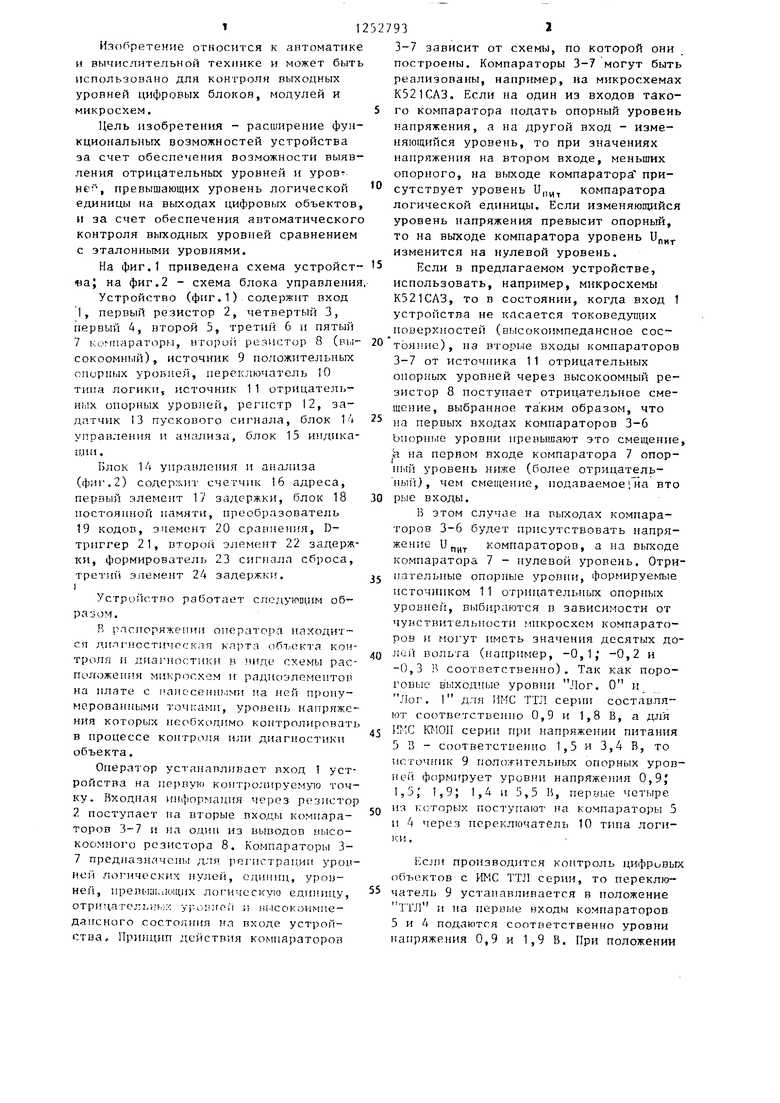

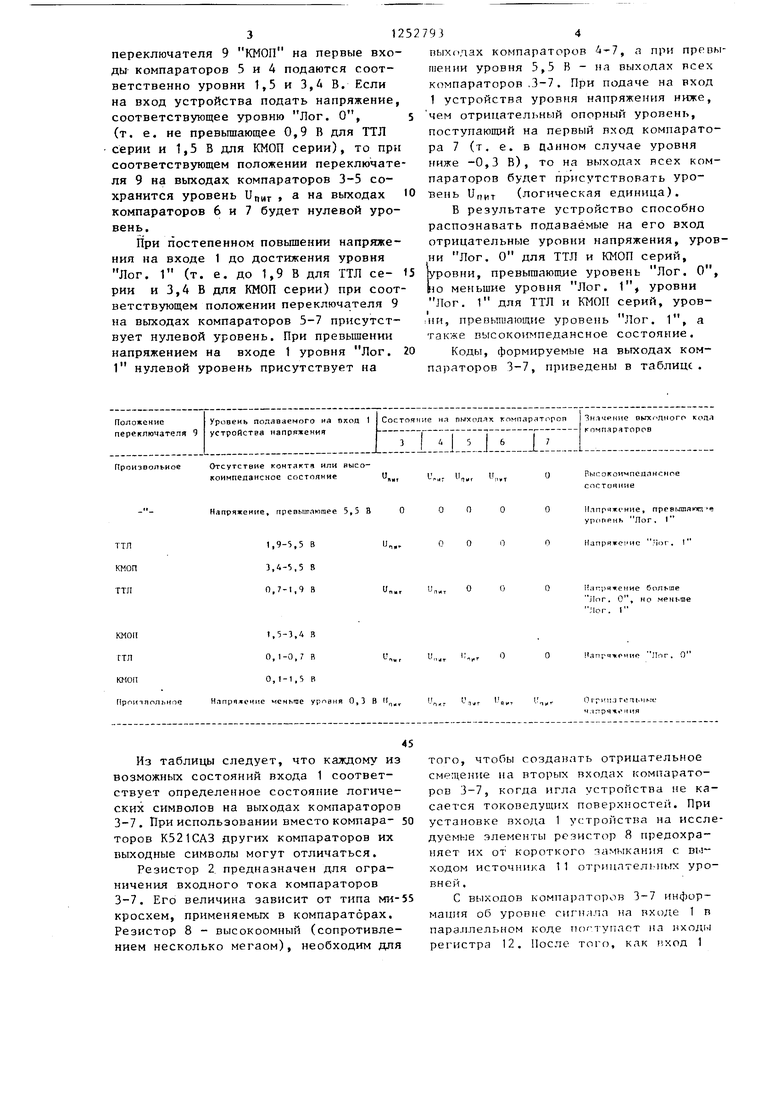

На фиг.1 приведена схема устройст- «а; на фиг.2 - схема блока управления

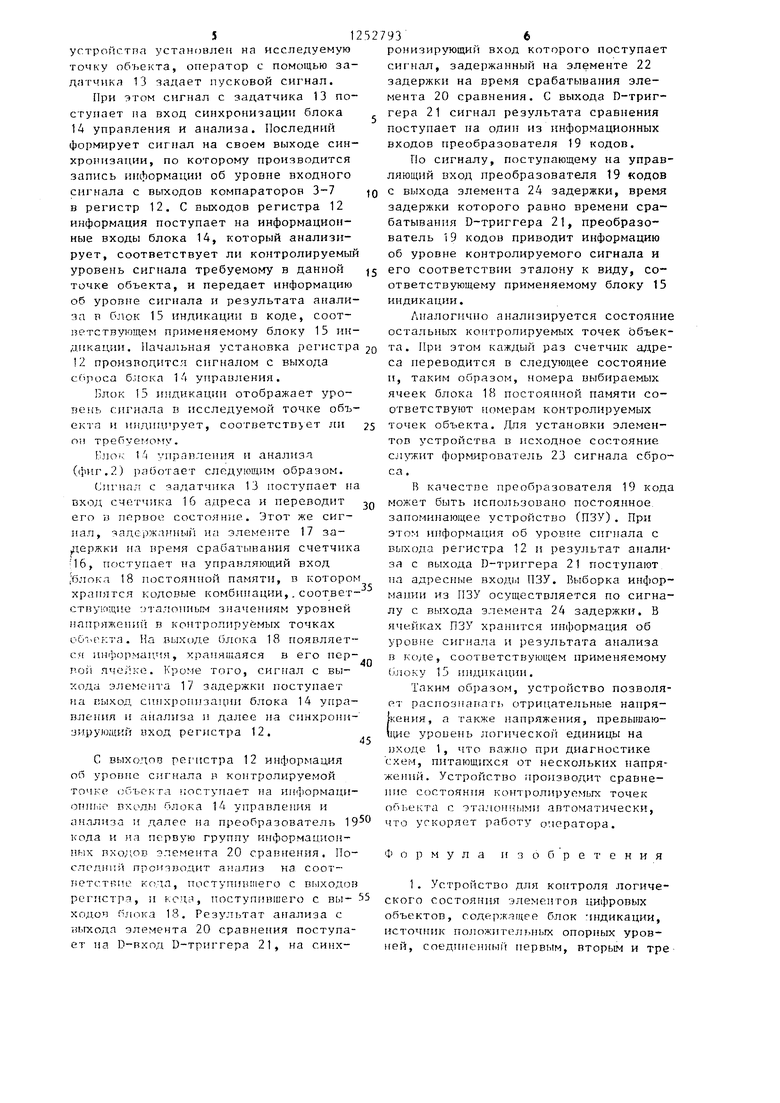

Устройство (фиг.1) содержит вход 1, первый резистор 2, четвертый 3, первый 4, второй 5, третий 6 и пятый 7 компараторы, irropuii резистор 8 (вы- сокоомный), источник 9 положительных oiiopiHiix уровней, переключатель 10 типа логики, источник 11 отрицательных опорных уровней, регистр 12, за- дптчик 13 пускового сигнала, блок 14 управле 1ия и алзлиза, блок 15 индикации .

Блок 14 управления и ангшиза (фиг.2) содержит счетчик 16 адреса, первый элемент Г/ задержки, блок 18 постоянной памяти, преобразователь 19 кодов, 3цемент 20 сравнения, D- триггер 21, второй элемент 22 задержки, формирователь 23 сигнала сброса.

третий элемент 24 задержки.

Устро 1стпо работает сле;д топ(пм образом.

R рлспоряжешги onepaTojia находится лил 1 ностическая карта объекта контроля и диаг)1ости си в ииде схемы рас- положенр я микросхем и радиоэлементов на плате с паиосенными на ней пронумерованными TO4Kat-in, уровень напряжения которых необхо71;имо контролировать в процессе контроля или диагностики объекта.

Оператор устанавливает вход 1 устройства на первую контролируемую точку. Входная информация через резистор 2 поступает на вторые входы компараторов 3-7 и на один из выводов высо- коомного резистора 8. Компараторы 3- 7 предназначены для регистрап.ии уровней логических нулей, единиц, уровней, препы;11,чю1цлх логическую едтп ицу, отринател1/г ь;-х ypoiinei i и нысокоимпе- даггсного состояния на входе устройства. Принцип действия компараторов

3-7 зависит от схемы, по которой они построены. Компараторы 3-7 могут быть реализованы, например, на микросхемах К521СЛЗ. Если на один из входов такого компаратора подать опорный уровень напряжения, а на другой вход - изменяющийся уровень, то при значениях напряжения на втором входе, меньших опорного, на выходе компаратора присутствует уровень и,, компаратора логической единицы. Если изменяюгцийся уровень напряжения превысит опорный, то на выходе компаратора уровень изменится на нулевой уровень.

Если в предлагаемом устройстве, использовать, например, микросхемы К521САЗ, то в состоянии, когда вход 1 устройства не касается тoкoвeдyп иx поверхностей (емсокоимпедансное состояние) , на вторые входы компараторов 3-7 от источника 11 отрицательных опорных уровней через высокоомный резистор 8 поступает отрицательное смещение, выбранное таким образом, что на первых входах компараторов 3-6 Ьпорные уровни препьшают это смещение, и на первом входе компаратора 7 опорный уровень ниже (более отрицат ль- ныт), чем смещение, подаваемое i на вто рые входы.

В этом случае на вьгходах компараторов 3-6 будет присутствовать напря

жение и

компараторов, а на выходе

компаратора 7 - нулевой уровень. Отрицательные опорные уровни, фopмиpye tыe источником 11 отрицательных опорных ypoBHOii, выбираются в зависимости от чувствительности микросхем компараторов и могут иметь значения десятых до- jiei i вольта (например, -0,1, -0,2 и -0,3 П соответственно). Так как пороговые выходные уровни Лог. О и Лог. I для ИМС ТТЛ серии составляют соответственно 0,9 и 1,8 В, а доГя ИМС КМОП серии при напряжении питания 5 В - соответственно 1,5 и 3,4 В, то источник 9 положительных опорных уровней формирует уровни нaпpяжelп я 0,9J 1,5, 1,9; 1,4 и 5,5 15, первые четыре из которых поступают на компараторы 5 и 4 через переключатС ль 10 типа логики.

Ксли производится контроль цифровых объектов с ИМС ТТЛ серии, то переключатель 9 устанавливается в положение ТТЛ и на iiep)3ijie входы компараторов 5 и 4 подаются соответственно уровни напряжения 0,9 и 1,9 В. При положении

31252

переключателя 9 КМОП на первые входы компараторов 5 и 4 подаются соответственно уровни 1,5 и 3,4 В. Если на вход устройства подать напряжение, соответствующее уровню Лог. О, 5 (т. е. не превьппающее 0,9 В для ТТЛ серии и 1,5 В для КМОП серии), то при соответствующем положении переключателя 9 на выходах компараторов 3-5 сохранится уровень ипит 3 на выходах О компараторов 6 и 7 будет нулевой уровень.

При постепенном повышении напряжения на входе 1 до достижения уровня Лог. 1 (т. е. до 1,9 В для ТТЛ се- 15 рии и 3,4 в для КМОП серии) при соответствующем положении переключателя 9 на выходах компараторов 5-7 присутствует нулевой уровень. При превьшении напряжением на входе 1 уровня Лог. 20 1 нулевой уровень присутствует на

9

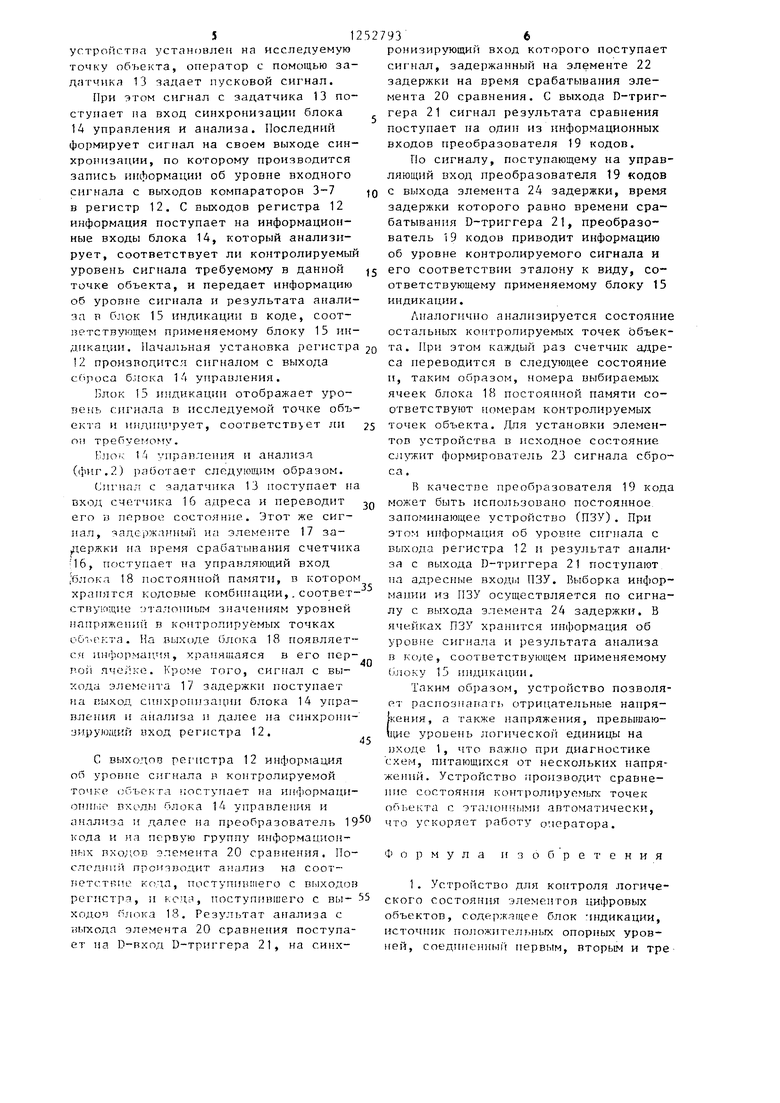

Уровень подяваемого на пиод 1 Состояние ня выхолях комплрлтороп устройства напряжения

.lПроизвольное

Отсутствие контакта или нысо- конмпедаисное состояниеU

Напряжение, превьшптщее 5,5 В

1,9-5,5 В 3,4-5,5 В 0,7-1,9 В

45

Из таблицы следует, что каждому из возможных состояний входа 1 соответствует определенное состояние логических символов на выходах компараторов 3-7. При использовании вместо компара- 50 торов К521САЗ других компараторов их выходные символы могут отличаться.

Резистор 2 предназначен для ограничения входного тока компараторов 3-7. Его величина зависит от типа ми-55 кросхем, применяемых в компараторах. Резистор 8 - высокоомный (сопротивлением несколько мегаом), необходим для

7934

выходах компараторов 4-7, а при превышении уровня 5,3 В - на выходах псех компараторов .3-7. При подаче на вход 1 устройства уровня напряжения ниже, чем отрицательный опорный уровень, поступающий на первый вход компаратора 7 (т. е. в данном случае уровня ниже -0,3 В), то на выходах всех компараторов будет присутствовать уровень и„,т (логическая единица).

В результате устройство способно распознавать подаваемые на его вход отрицательные уровни напряжения, уровни Лог. О для ТТЛ и КМОП серий, уровни, превышающие уровень Лог. О, МО меньшие уровня Лог. 1, уровни Лог. 1 для ТТЛ и КМОП серий, уров:ни, превышающие уровень Лог. Г , а также высоко1пчпедансное состояние.

Коды, формируемые на выходах компараторов 3-7, приведены в таблице.

выхолях комплрлтороп

.lЗи.эчрцио оьпсплного компараторов

t n.r Чп., п.т

о п

Р.ысокоя ипецл немое сосганние

1 лпряж1 ние, пррвмшающ ypfinpHb Лог ,

Напрйжс1 ис Jior,

Un, о

;11трнженне больше jlor. 0 но меньше Лог. Г

того, чтобы созданать отрицательное смещение на вторых входах компараторов 3-7, когда игла устройства не касается токопедущих поверхностей. При установке входа 1 устройства на исследуемые элементы резистор 8 предохраняет их от короткого замыкания с выходом источника 1 1 отрииатель и.1Х уровней.

С выходов компараторов 3-7 информация об уровне сигняла на BXtvie 1 п параллельном коде погтугтаст на нходы регистра 12. После тогг), как яход 1

устройстпа устан(П1леи на исследуемую точку объекта, оператор с помощью за- дптчикя 13 задает пусковой сигнал.

При этом сигнал с задатчика 13 поступает па вход синхронизации блока 14 управления и анализа. Последний формирует сигнал на своем выходе синхронизации, по которому производится запись информации об уровне входного сигьгала с выходов компараторов 3-7 в регистр 12. С выходов регистра 12 информация поступает на информационные входы блока 14, который анализирует, соответствует ли контролируемый уровень сигнала требуемому в данной точке объекта, и передает информацию об уровне сигнала и результата анализа п блок 15 индикации в коде, соот- петствующем применяемому блоку 15 индикации. Начальная установка регистра 2 производится сигналом с выхода спроса блока 14 управления.

Блок 15 индикации отображает уровень сигнала в исследуемой точке екта и индицирует, соответствует ли он TpeOyetfoMv.

fJjioK 14 управления и анализа ((риг. 2) 1 аботает следующим образом.

Сигнал с задатчика 13 поступает на вход счетчика 16 адреса и переводит его в первое состояние. Этот же сигнал, заде11жанны} 1 на элементе 17 за- тержки на время срабатывания счетчика Мб, поступает на управляющий вход . блока 18 постоянной памяти, в котором хранятся кодовые комбинации,.соответствующие ;)талопным значе1и-1ям уровней напряжени в контролируемых точках о&т-екта. На выходе блока 18 появляет- С5( информация, хранящаяся в его пер- p.oji ячейке. Кроме того, сигнал с выхода элемента 17 задержки поступает на выход синхронизации блока 14 упра- и а 1ализа и далее на синхронизиру)1тгий вход регистра 12.

С выходов регистра 12 информация об ypoBtie в контролируемой точке объекта поступает на информаци- oHiHiie входь блока 14 управления и анализа и далее на преобразователь 19 кода и на первую группу информационных входов элемента 20 сравне1 ия. Последний произгзодит анализ на соответствие кола, поступившего с выходов регистра, и KCULI, поступившего с вы- ходон Rjioifa 18. Результат анализа с иыхода элемента 20 сравнения поступает на D-вход D-триггера 21, на синх

, д 5 2о

25

о

5

5

5

0

ронизирующий вход которого поступает сигнал, задержанный на элементе 22 задержки на время срабатывания элемента 20 сравнения. С выхода D-триггера 21 сигнал результата сравнения поступает па один из информационных входов преобразователя 19 кодов.

По сигналу, поступающему на управляющий вход преобразователя 19 кодов с выхода элемента 24 задержки, время задержки которого равно времени срабатывания D-триггера 21, преобразователь 19 кодов приводит информацию об уровне контролируемого сигнала и его соответствии эталону к виду, соответствующему применяемому блоку 15 индикации.

Аналогично анализируется состояние остальных контролируемых точек объекта. При этом каждый раз счетчик адреса переводится в следую)цее состояние и, таким образом, номера выбираемых ячеек блока 18 постоянной памяти соответствуют номерам контролируемых точек обттекта. Для установки элементов устройства в исходное состояние сл: -жит формирователь 23 сигнала сброса .

В качестве преобразователя 19 кода может быть использовано постоянное, запоминающее устройство (ПЗУ). При этом информация об уровне сигнала с выхода регистра 12 и результат анализа с выхода D-триггера 21 поступают на адресные входы ПЗУ. Выборка инфор- мапии из ПЗУ осуществляется по сигналу с выхода элемента 24 задержки. В ячейках ПЗУ хранится информация об уровне сигнала и результата анализа в коде, соответствующем применяемому fjjioKy 15 индикац1П1.

Таким образом, устройство позволяет распознавать отрицательные напря- |кенпя, а также напряжения, превышаю- 1цие уровень логической единицы на входе 1, что важно при диагностике схем, питающ1гхся от нескольких напряжений. Устройство 1роизводит сравнение состояния контролируемых точек обье1ста с эта, автоматически, что ускоряет работу оператора.

Формула изобретения

1. Устройство для контроля логического состояния элементов цифровых объектов, содержащее блок ищикации, источник положител1,ньгх опорных уровней, соедине1П ый первым, вторым и тре

тьим выходами с соответствующими входами переключения типа логики, первый и второй выходы которого соединены соответственно с первыми входами первого и второго компараторов (Соединенных 5 вторыми входами с первы ш выводами первого и второго резисторов, второй вывод первого резистора соединен с входом устройства, содержащее также источник отрицательных опорных уров- Ю ней, соединенный первым выходом с первым входом третьего компаратора, соединенного вторым входом с первым выводом первого резистора, второй выход источника отрицательных опорных ypoB-t5 ней соединен с вторым выводом второго резистора, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения возможности выявле- 20 ния отрицательных уровней и уровней, превышающих уровень логической единицы на выходах цифровых объектов, и за счет обеспечения возможности автоматического контроля выходных уровней ера- 25 внением с эталонными уровнями, в него дополнительно введены регистр, блок управления и анализа, четвертый и пятый компараторы и задатчик пускового сигнала, причем первый вход четверто- зо го компаратора соединен с четвертым выходом источника положительных опорных уровней, первый вход пятого компаратора соединен с третьим выходом источника отрицательных опорных урон-,, ней, второй вход - с вторым входом четвертого компаратора и с первым выводом первого резистора, выходы всех компараторов соединены с информационными входами регистра, соединенного о выходами с информационными входами

бпока управления и анализа, а установочным и синхронизирующим входами - соответственно с установочным и синхронизирующим выходами блока управле- ния и анализа, соединенного управляющим входом с выходом задатчика пускового сигнала, а выходами - с входами блока индикации,

2. Устройство по П.1, отличающееся тем, что блок управления и анализа содержит счетчик адреса, вход которого является управляющим входом блока управления и анализа, который соединен с входом первого элемента задержки, выход которого является синхронизирующим выходом блока управления и анализа и соединен с управляющим входом блока постоянной памяти, соединенного адресными входами с выходами счетчика адреса, а выходами - с соответствующими первыми входами элемента сравнения, соединенного вторыми входами с первыми входами преобразователя кодов, которые являются информационными входами блока управления и анализа, а также содержит второй элемент задержки, соединенный входом с выходом первого эле- MeitTH задержки, выходом - с С-входом D-триггера непосредственно, а через третий элемент задержки - с управляющим входом преобразователя кодов, соединенного выходами с выходами блока управления и анализа, а синхро- входом - с выходом D-триггера, соединенного D-входом с выходом элемента сравнения, а R-входом - с выходом формирователя сигнала сброса, который является установочным выходом блока |управления и анализа, и с установочным входом счетчика адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ КОНТРОЛЯ КОНТАКТИРОВАНИЯ КМОП-БИС И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2009518C1 |

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1984 |

|

SU1197085A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Компаратор | 1988 |

|

SU1631512A1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Устройство измерения времени установления выходного напряжения операционных усилителей | 1986 |

|

SU1441339A1 |

| Компаратор | 1990 |

|

SU1755253A1 |

| Устройство для регенерации телеграфных посылок | 1985 |

|

SU1338080A2 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1343417A1 |

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1985 |

|

SU1356233A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля выходных уровней цифровых блоков, модулей, ячеек и микросхем. Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения возможности выявления отрицательных уровней и уровней, превышающих уровень логической едини11гы на выходах цифровых объектов, и за счет обеспечения автоматического контроля выходных уровней сравнением с эталонными уровнями. Устройство содержит два резистора, пять компараторов, источник положительных опорных уровней, источник отрицательных опорных уровней, переключатель типа логики, регистр, задат- чик пускового сигнала, блок управления и анализа, блок индикации. За счет введения двух дополнительных компараторов обеспечивается возможность контроля отрицательных уровней и превьппения уровня логической единицы. Введение регистра, блока управления и анализа и задатчика пускового сигнала обеспечивает возможность контроля выходных уровней цифровых объектов, что расширяет фуьгкциональные возможности устройства. 1 3. п. ф-лы, ,2 ил., 1 табл. с 8 (Л

Редактор В.Петраш

Составитель Н.Главизнина

Техред И.Верес Корректор И.Муска

Заказ А622/50Тираж 671 Подписное

ВНИППИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. А/5

Производственно-полиграфическое предприятие, г. Ужгород, ул, Проектная,

| Индикатор логических состояний.- Электроника, 1977, № 5, с | |||

| Способ окисления боковых цепей ароматических углеводородов и их производных в кислоты и альдегиды | 1921 |

|

SU58A1 |

| Динамический логический пробник.- Электроника, 1980, № 16, с | |||

| Устройство для сортировки каменного угля | 1921 |

|

SU61A1 |

Авторы

Даты

1986-08-23—Публикация

1984-11-06—Подача