I1

Изобретение относится к автоматике и вычислительной технике, в частности к обучающим устройствам с ис- пользованием ЭВМ.

Цель изобретения - расширение дидактических возможностей устройства.

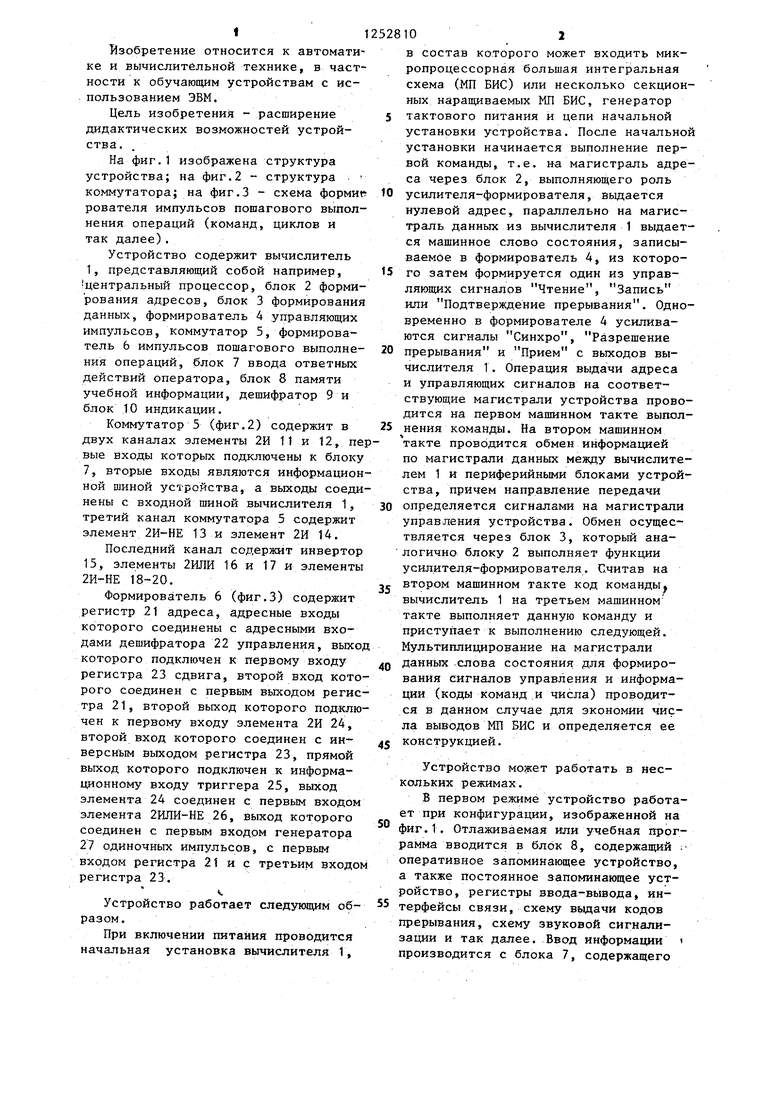

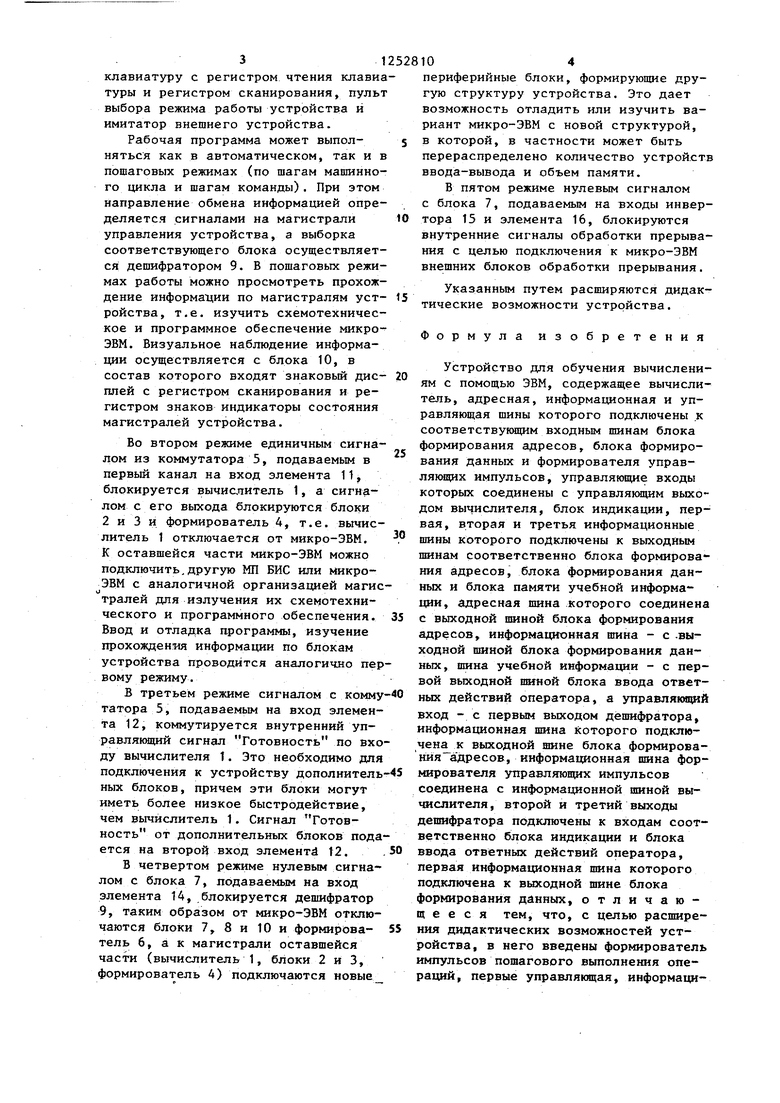

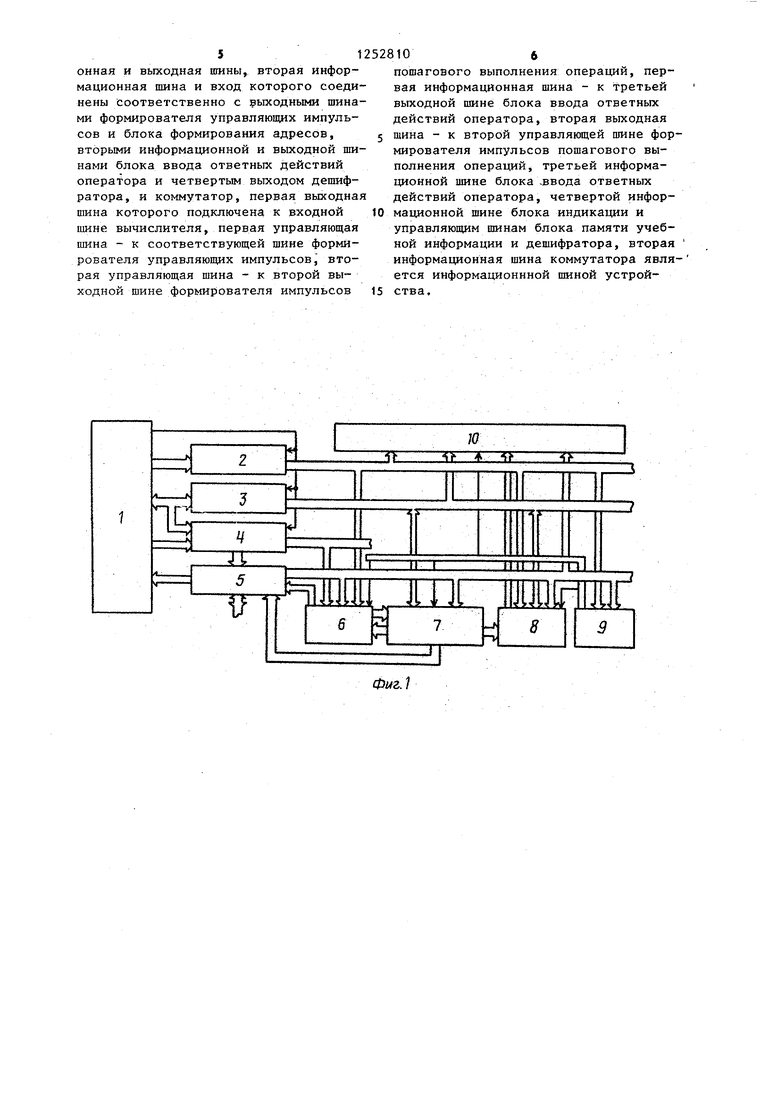

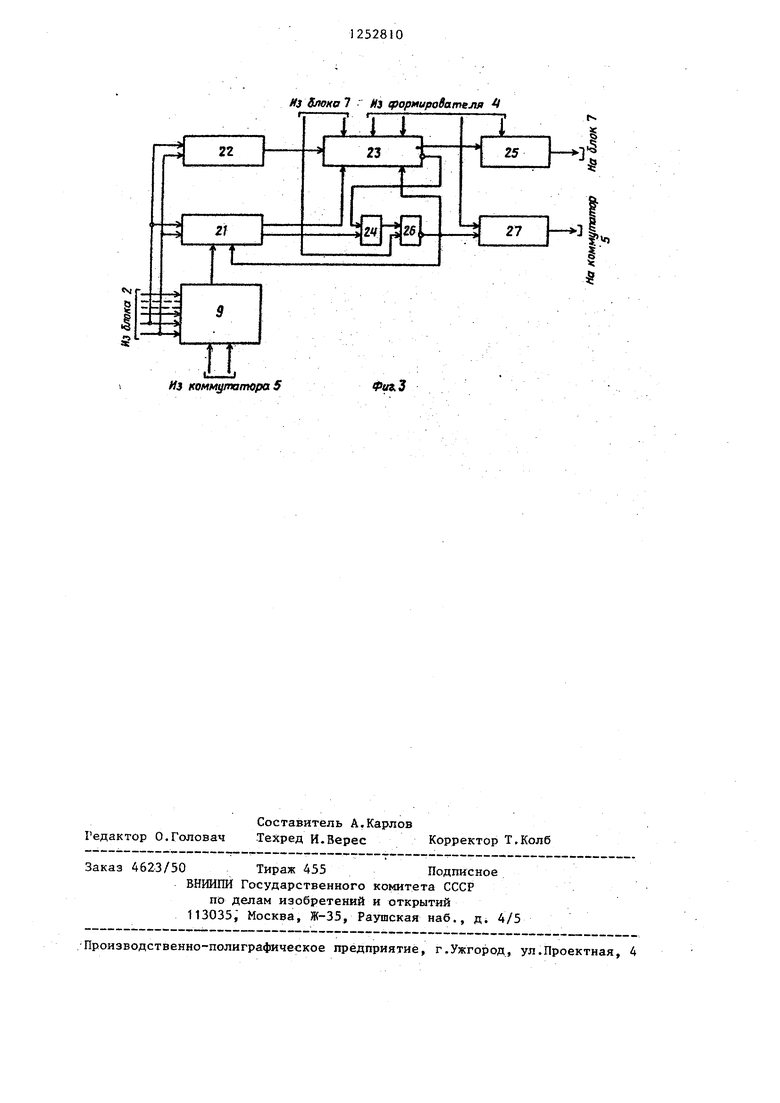

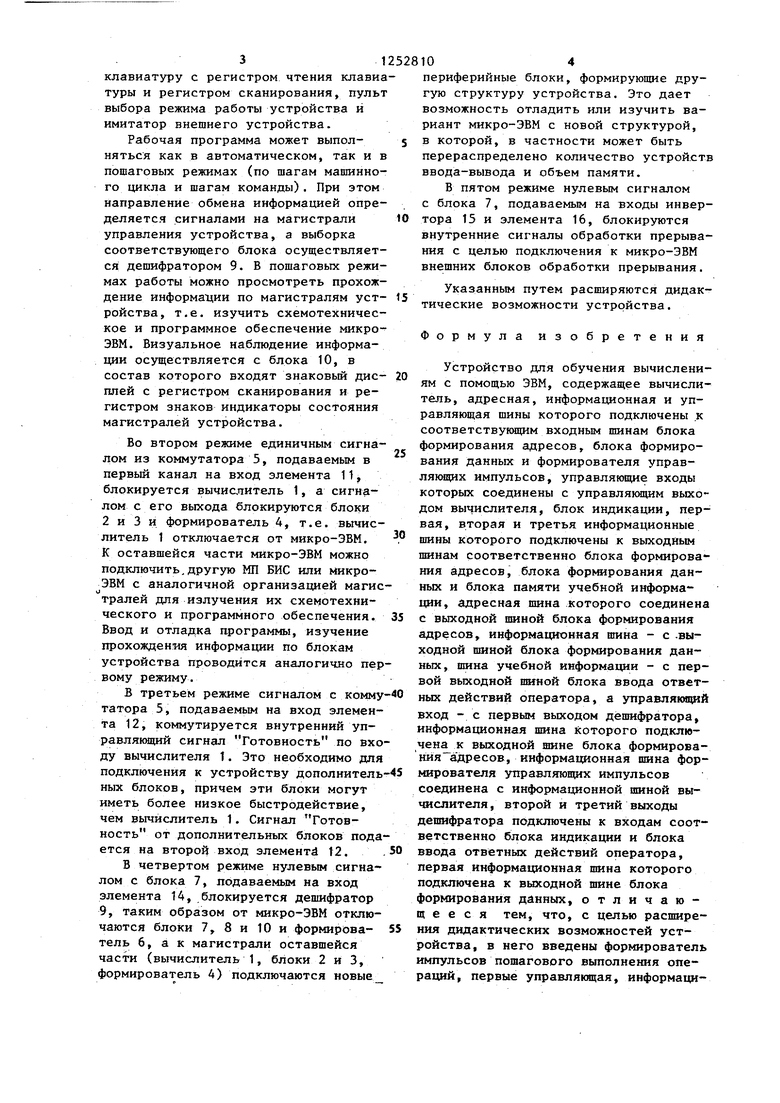

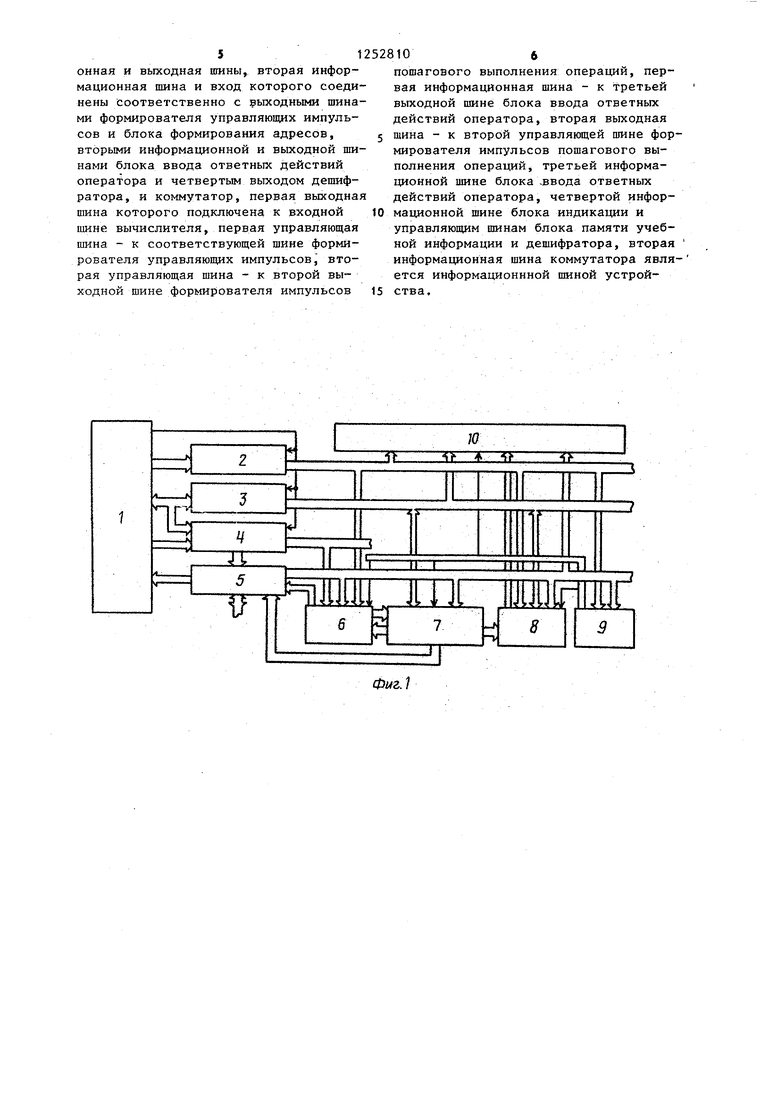

На фиг.1 изображена структура устройства; на фиг.2 - структура коммутатора; на фиг.З - схема формип рователя импульсов пошагового выполнения операций (команд, циклов и так далее).

Устройство содержит вычислитель 1, представляющий собой например, центральный процессор, блок 2 формирования адресов, блок 3 формирования данных, формирователь 4 управляющих импульсов, коммутатор 5, формирователь 6 импульсов пошагового выполне- ния операций, блок 7 ввода ответных действий оператора, блок 8 памяти учебной информации, дешифратор 9 и блок 10 индикации.

Коммутатор 5 (фиг.2) содержит в двух каналах элементы 2И 11 и 12, певые входы которых подключены к блоку 7, вторые входы являютсй информационной шиной устройства, а выходы соединены с входной шиной вычислителя 1, третий канал коммутатора 5 содержит элемент 2И-НЕ 13 и элемент 2И 14.

Последний канал содержит инвертор 15, элементы 2ИЛЙ 16 и 17 и элементы 2И-НЕ 18-20.

Формирователь 6 (фиг.З) содержит регистр 21 адреса, адресные входы которого соединены с адресными входами дешифратора 22 управления, выхо которого подключен к первому входу регистра 23 сдвига, второй вход которого соединен с первым выходом регистра 21, второй выход которого подключен к первому входу элемента 2И 24, второй вход которого соединен с ин- версным выходом регистра 23, прямой выход Которого подключен к информационному входу триггера 25, выход элемента 24 соединен с первым входом элемента 2ИЛИ-НЕ 26, выход которого соединен с первым входом генератора 27 одиночных импульсов, с первым входом регистра 21 и с третьим входо регистра 23.

ч

Устройство работает следующим об- разом.

При включении питания проводится начальная установка вычислителя 1,

5

0

5 0

5 о

п Q

5

5

102

в состав которого может входить микропроцессорная большая интегральная схема (МП БИС) или несколько секционных наращиваемых МП БИС, генератор тактового питания и цепи начальной установки устройства. После начальной установки начинается выполнение первой команды, т.е. на магистраль адреса через блок 2, выполняющего роль усилителя-формирователя, выдается нулевой адрес, параллельно на магистраль данных из вычислителя 1 выдается машинное слово состояния, записываемое в формирователь 4, из которого затем формируется один из управляющих сигналов Чтение, Запись или Подтверждение прерывания. Одновременно в формирователе 4 усиливаются сигналы Синхро, Разрешение прерывания и Прием с выходов вычислителя Т. Операция выдачи адреса и управляющих сигналов на соответствующие магистрали устройства проводится на первом машинном такте выполнения команды. На вторрм машинном такте проводится обмен информацией по магистрали данных между вычислителем 1 и периферийными блоками устройства , причем направление передачи определяется сигналами на магистрали управления устройства. Обмен осуществляется через блок 3, который аналогично блоку 2 выполняет функции усилителя-формирователя. Считав на втором машинном такте код команды вычислитель 1 на третьем машинном такте выполняет данную команду и приступает к выполнению следующей. Мультиплицирование на магистрали данных слова состояния для формирования сигналов управления и информации (коды команд .и числа) проводится в данном случае для экономии числа выводов МП БИС и определяется ее конструкцией.

Устройство может работать в нескольких режимах.

В первом режиме устройство работает при конфигурации, изображенной на фиг.1. Отлаживаемая или учебная программа вводится в блок 8, содержащий ; оперативное запоминающее устройство, а также постоянное запоминающее устройство, регистры ввода-вывода, интерфейсы связи, схему вьщачи кодов прерывания, схему звуковой сигнализации и так далее. Ввод информации производится с блока 7, содержащего

31

клавиатуру с регистром чтения клавиатуры и регистром сканирования, пульт выбора режима работы устройства и имитатор внешнего устройства.

Рабочая программа может выпол- мяться как в автоматическом, так и в пошаговых режимах (по шагам машинного цикла и шагам команды). При этом направление обмена информацией определяется сигналами на магистрали управления устройства, а выборка соответствующего блока осуществляется дешифратором 9. В пошаговых режимах работы можно просмотреть прохождение информации по магистралям уст- ройства, т.е. изучить схемотехническое и программное обеспечение микроЭВМ. Визуальное наблюдение информации осуществляется с блока 10, в состав которого входят знаковьй дис- плей с регистром сканирования и регистром знаков индикаторы состояния магистралей устройства.

Во втором режиме единичным сигналом из коммутатора 5, подаваемым в первый канал на вход элемента 11, блокируется вычислитель 1, а сигналом с его выхода блокируются блоки 2 и 3 и формирователь 4, т.е. вычис

литель 1 отключается от микро-ЭВМ.

К оставшейся части микро-ЭВМ можно подключить,другую МП БИС или микро- ЭВМ с аналогичной организацией магистралей для излучения их схемотехнического и программного обеспечения. 35 Ввод и отладка программы, изучение прохождения информации по блокам устройства проводится аналогично первому режиму.

В третьем режиме сигналом с комму- О татора 5, подаваемым на вход элемента 12, коммутируется внутренний управляющий сигнал Готовность по входу вычислителя 1. Это необходимо для подключения к устройству дополнитель-45 ных блоков, причем эти блоки могут иметь более низкое быстродействие, чем вычислитель 1. Сигнал Готовность от дополнительных блоков подается на второй вход элементй 12. .50

В четвертом режиме нулевым сигналом с блока 7, подаваемым на вход элемента 14, блокируется дешифратор 9, таким образом от микро-ЭВМ отключаются блоки 7, 8 и 10 и формирова- 55 тель 6, а к магистрали оставшейся части (вычислитель 1, блоки 2 и 3, формирователь 4) подключаются новые

s 5 0

5

0

5

О 5 0

5

104

периферийные блоки, формирующие другую структуру устройства. Это дает возможность отладить или изучить вариант микро-ЭВМ с новой структурой, в которой, в частности может быть перераспределено количество устройств ввода-вывода и объем памяти.

В пятом режиме нулевым сигналом с блока 7, подаваемым на входы инвертора 15 и элемента 16, блокируются внутренние сигналы обработки прерывания с целью подключения к микро-ЭВМ внешних блоков обработки прерывания.

Указанным путем расширяются дидактические возможности устройства.

Формула изобретения

Устройство для обучения вычислениям с помощью ЭВМ, содержащее вычисли тель, адресная, информационная и управляющая шины которого подключены к соответствукнцим входным шинам блока формирования адресов, блока формирования данных и формирователя управляющих импульсов, управляющие входы которых соединены с управлякицим выходом вычислителя, блок индикации, первая, вторая и третья информационные шины которого подключены к выходным шинам соответственно блока формирования адресов, блока формирования данных и блока памяти учебной информации, адресная шина которого соединена с выходной шиной блока формирования адресов, информационная шина - с .выходной шиной блока формирования данных, шина учебной информации - с первой выходной шиной блока ввода ответных действий оператора, а управлякяшй вход - с первым выходом дешифратора, информационная шина которого подключена к выходной шине блока формирования адресов, информащюнная шина формирователя управляюнц1х импульсов соединена с информационной шиной вы- шслителя, второй и третий выходы дешифратора подключены к входам соответственно блока индикации и блока ввода ответных действий оператора, первая информационная шина которого подключена к выходной шине блока формирования д 1нных, отличающееся тем, что, с целью расширения дидактических возможностей устройства, в него введены формирователь импульсов пошагового выполнения операций, первые управлякяцая, информационная и выходная шины, вторая информационная шина и вход которого соединены соответственно с выходными шинами формирователя управляющих импульсов и блока формирования адресов, вторыми информационной и выходной шинами блока ввода ответных действий onepatopa и четвертым выходом дешифратора, и коммутатор, первая выходная шина которого подключена к входной шине вычислителя, первая управляющая шина - к соответствующей шине формирователя управляющих импульсов, вторая управляющая шина - к второй выходной шине формирователя импульсов

пошагового выполнения операций, первая информационная шина - к третьей выходной шине блока ввода ответных действий оператора, вторая выходная шина - к второй управляющей шине формирователя импульсов пошагового выполнения операций, третьей информационной шине блока -ввода ответных действий оператора, четвертой информационной шине блока индикации и управляющим шинам блока памяти учебной информации и дешифратора, вторая информационная шина коммутатора является информационнной шиной устройства.

С блока 7 Инсрормационнай wuna цстройстВа

Фиг.2

Из &пона1 Нз срормиробателя

И

Нз коммутатора 5

Фи.3

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения электронной вычислительной машины с общей шиной | 1983 |

|

SU1144112A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ ДУГОВОЙ СВАРКИ НЕПЛАВЯЩИМСЯ ЭЛЕКТРОДОМ В СРЕДЕ ЗАЩИТНЫХ ГАЗОВ | 1988 |

|

SU1683244A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Устройство для отображения информации | 1986 |

|

SU1506478A1 |

| Устройство для отображения информации | 1983 |

|

SU1193722A1 |

| Устройство для контроля неисправностей | 1987 |

|

SU1564626A1 |

| УСТРОЙСТВО ДИАГНОСТИЧЕСКОГО КОНТРОЛЯ КАНАЛА ВОСПРОИЗВЕДЕНИЯ АППАРАТУРЫ ЦИФРОВОЙ МАГНИТНОЙ ЗАПИСИ | 1991 |

|

RU2024968C1 |

| Устройство для управления обращением к общей памяти | 1987 |

|

SU1495804A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

Гедактор О.Головач

Составитель А.Карлов

Техред И.Верес Корректор Т,Колб

Заказ 4623/50 Тираж 455Подписное

ВНИИГМ Государственного комитета СССР

по делам изобретений и открытий 113035J Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

| Гладков A.M | |||

| и Хохлов Ю.В | |||

| Дисковая паровая турбина | 1922 |

|

SU580A1 |

| - Приборы и системы управления | |||

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Красавин В.Н., Панфилов Д.И., Ро- манченко О.А | |||

| и Шаронин С.Г | |||

| Дисковая паровая турбина | 1922 |

|

SU580A1 |

| Сб | |||

| Электронная про- мьшшенность | |||

| Гребенчатая передача | 1916 |

|

SU1983A1 |

Авторы

Даты

1986-08-23—Публикация

1984-06-28—Подача