1254491

Изобретение относится к вычислип

тельной технике и может быть использовано при отладке программ специализированных цифровых вычислительных систем (СЦВС) реального времени.

Цель изобретения - повышение быстродействия времени отладки программ путем формирования прерывания при реализации в программе перехода с заданным приращением адреса.

Сущность изобретения заключается в том, что на каждом шаге вьтолнения программы вьтисляется приращение ад- деса, как абсолютная величина разности последующего А ,,, и предыдущего А кода адреса, и сравнивается с заранее заданным допустимым приращением адреса (ПА) команды.

Если абсолютная величина прираще- ния адреса команды превышает допустимую

|А.

П41- , или в другом виде

АП, А„ +

nti

ПА А - ПА,

то устройство формирует сигнал прерывания программы.

Например, если допустимое приращение адреса команды соответствует 2 (или 4 в зависимости от типа ЭВМ), то при приращении адреса команда на линейном участке программы соответственно на 1 (или на 2) сигнал прерывания формируется только при реализации команды перехода.

При меньшем значении допустимого., приращения адреса сигнал прерьгаания формируется после вьтолнения каждой команды. При большем значении допустимого приращения для части переходов программы сигнал прерывания устройством не вырабатьшается.

При этом устройство учитывает работу на границах адресного поля,определяемого принятой разрядностью кода адреса. Если в результате суммирования AJ, + ПА возникает переполнение разрядной сетки (наличие переноса в с 4маторе) или в результате вычитания разность А„ - ПА оказывается отрицательной (знаковый разряд сумматора равен t), что означает в обоих случаях выход за пределы адресного поля, то условия формирования прерывания отсутствуют.

5

0

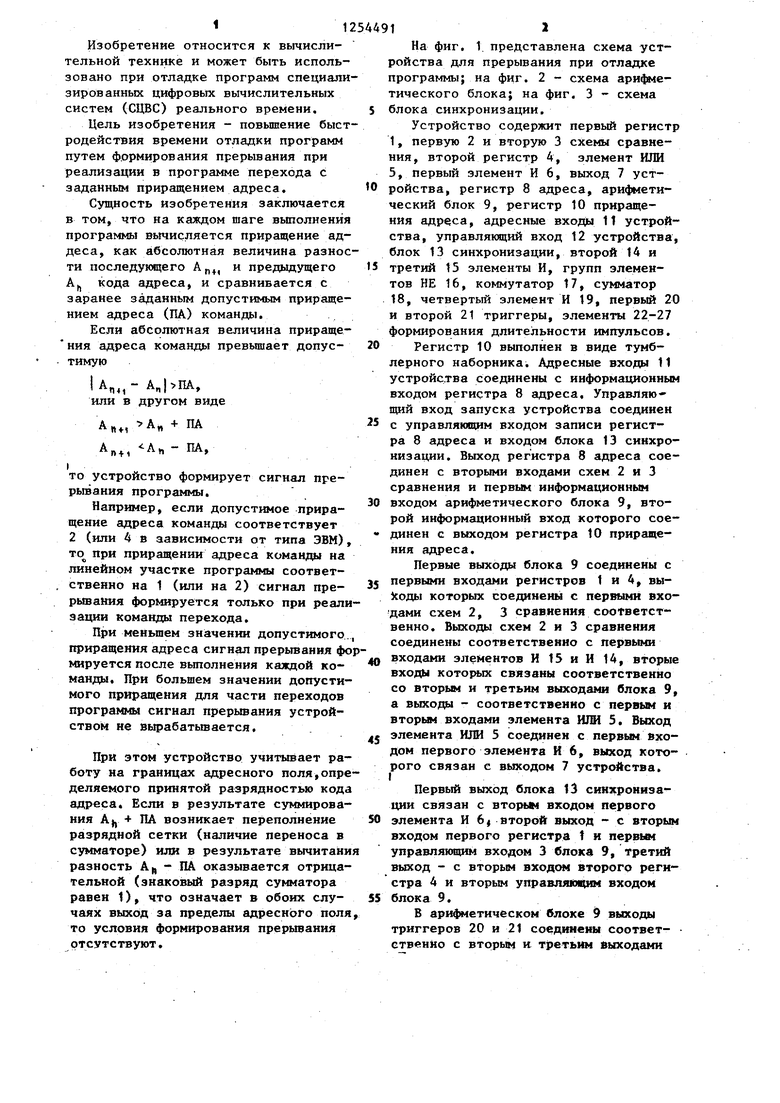

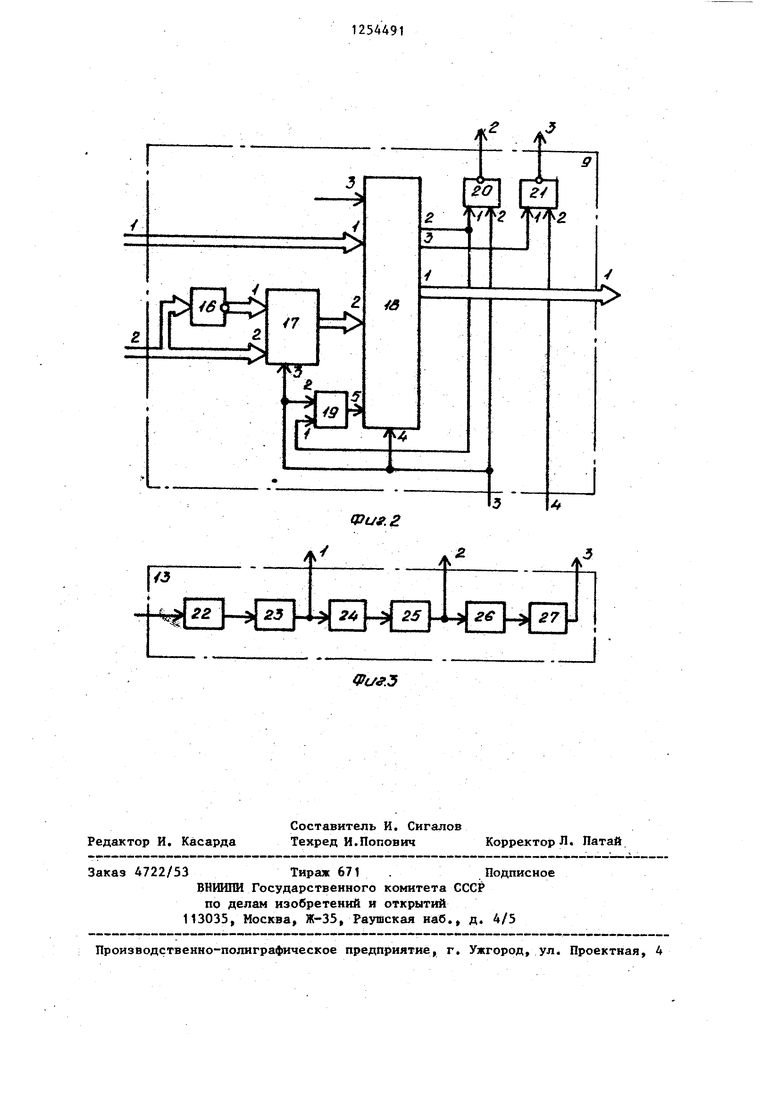

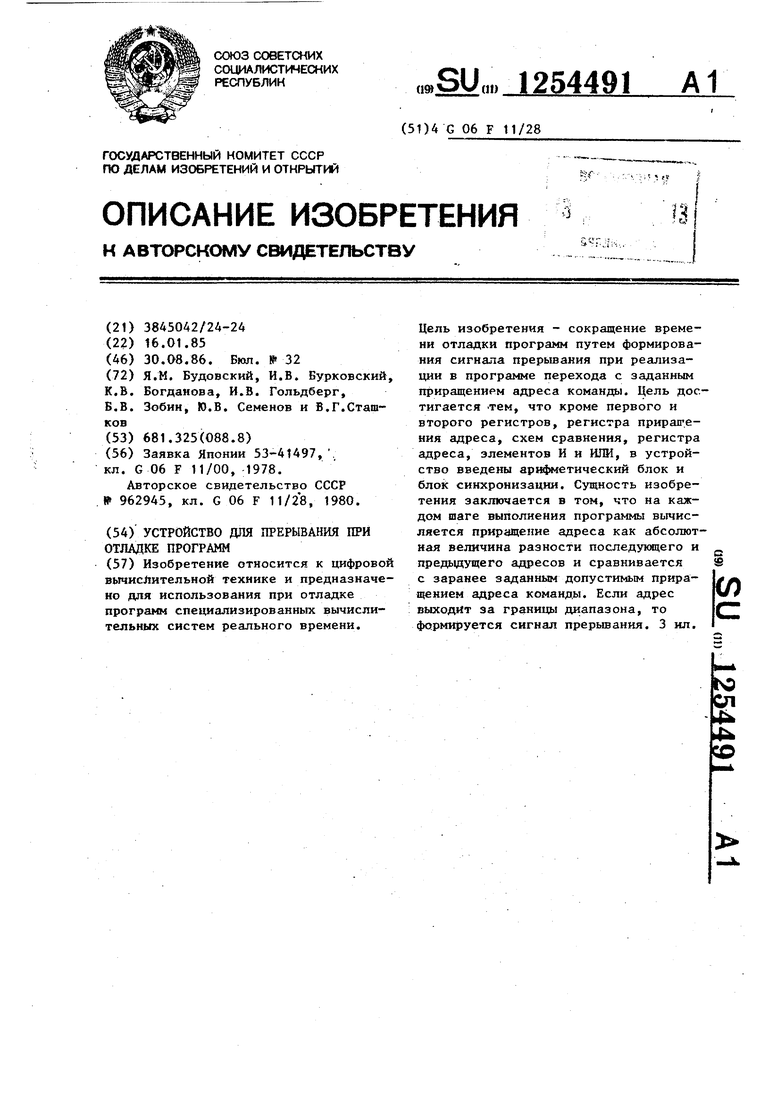

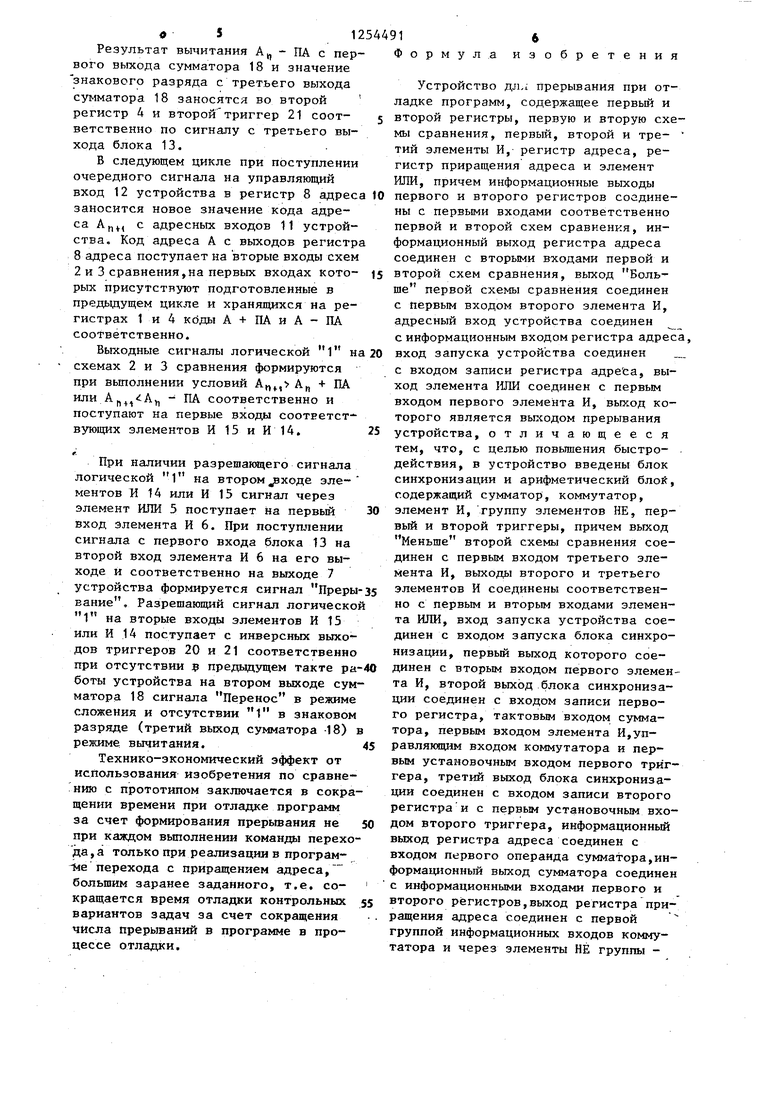

На фиг. 1 представлена схема устройства для прерывания при отладке программы; на Фиг. 2 - схема арифметического блока; на фиг. 3 - схема блока синхронизации.

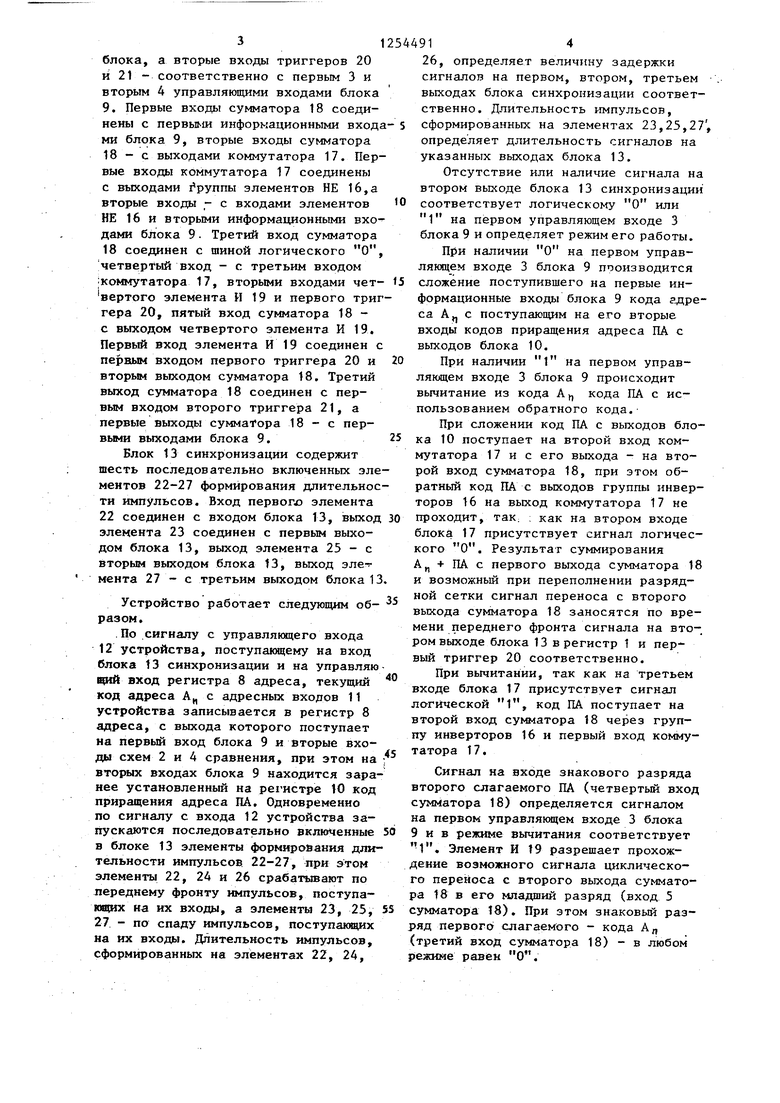

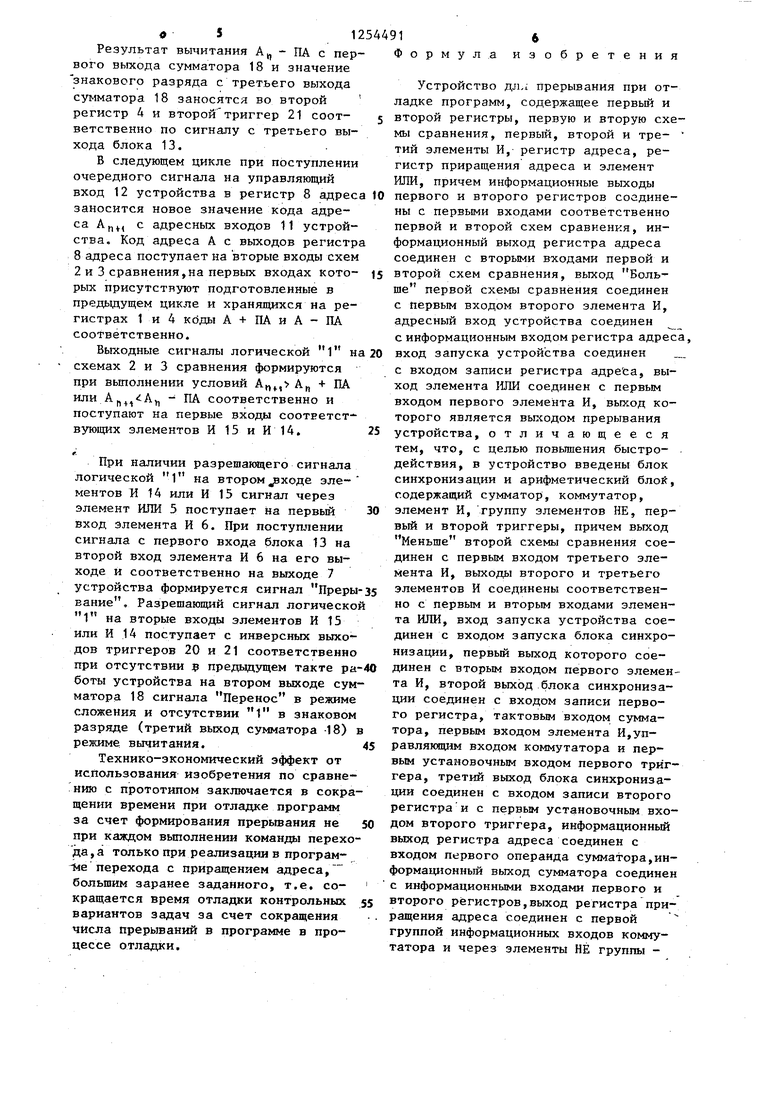

Устройство содержит первый регистр 1, первую 2 и вторую 3 схемы сравнения, второй регистр 4, злемент ИЛИ 5, первый элемент И 6, выход 7 устройства, регистр 8 адреса, арифметический блок 9, регистр 10 приращения адреса, адресные входы 11 устройства, управлякядий вход 12 устройства, блок 13 синхронизации, второй 14 и третий 15 элементы И, групп элементов НЕ 16, коммутатор 17, сумматор 18, четвертый злемент И 19, первый 20 и второй 21 триггеры, элементы 22-27 формирования длительности импульсов.

Регистр 10 выполнен в виде тумблерного наборника; Адресные входы 11 устройства соединены с информационным входом регистра В адреса. Управляющий вход запуска устройства соединен с управляющим входом записи регистра 8 адреса и входом блока 13 синхронизации. Выход регистра 8 адреса соединен с вторыми входами схем 2 и 3 сравнения и первым информационным входом арифметического блока 9, второй информационный вход которого соединен с выходом регистра 10 приращения адреса.

Первые выходы блока 9 соединены с первыми входами регистров 1 и 4, вы- )соды которых соединены с первыми вхо- дами схем 2, 3 сравнения соответственно. Выходы схем 2 и 3 сравнения соединены соответственно с первыми 0 входами элементов И 15 и И 14, вторые входы кото1 1х связаны соответственно со вторым и третьим выходами блока 9, а выходы - соответственно с первым и вторым входами элемента ИЛИ 5. Выход элемента ИЛИ 5 соединен с первым вхо5

0

5

5

дом первого элемента И 6, выход кото- рого связан с выходом 7 устройства.

Первый выход блока 13 синхрониза ции связан с вторив входом первого

0 элемента И 6| второй выход - с вторым входом первого регистра f и первьм управляющим входом 3 блока 9, третий выход - с вторым входом второго регистра 4 и вторым управля1()Цим входом

5 блока 9.

В арифметическом блоке 9 выходы триггеров 20 и 21 соединены соответ- ственно с вторым и третьим выходами

блока, а вторые входы триггеров 20 и 21 - соответственно с первым 3 и вторым 4 управляющими входами блока 9. Первые входы сумматора 18 соединены с первыьш информационными входами блока 9, вторые входы сумматора 18 - с выходами коммутатора 17. Первые входы коммутатора 17 соединены с выходами 1 руппы элементов НЕ 16,а

вторые входы - с входами элементов

НЕ 16 и вторыми информационными входами блока 9. Третий вход сумматора 18 соединен с шиной логического О, четвертый вход - с третьим входом ;Коммутатора 17, вторыми входами чет- вертого элемента И 19 и первого триггера 20, пятый вход сумматора 18 - с выходом четвертого элемента И 19. Первый вход элемента И 19 соединен с nejpEUbiM входом первого триггера 20 и вторым выходом сумматора 18. Третий выход сумматора 18 соединен с первым входом второго триггера 21, а первые выходы сумматора 18 - с первыми выходами блока 9.

Блок 13 синхронизации содержит шесть последовательно включенных элементов 22-27 формирования длительности импульсов. Вход первого элемента 22 соединен с входом блока 13, выход элемента 23 соединен с первым выходом блока 13, выход элемента 25 - с вторым выходом блока 13, выход эле- мента 27 - с третьим выходом блока 13

Устройство работает следующим об- разом.

. По сигналу с управляккцего входа 12 устройства, поступакндему на вход блока 13 синхронизации и на управляющий вход регистра 8 адреса, текущий код адреса А„ с адресных входов 11 устройства записывается в регистр 8 адреса, с выхода которого поступает на первый вход блока 9 и вторые входы схем 2 и 4 сравнения, при этом на вторых входах блока 9 находится заранее установленный на ре1 истре tO код приращения адреса ПА. Одновременно по сигналу с входа 12 устройства запускаются последовательно включенные в блоке 13 элементы формирования длительности импульсов 22-27, при этон элементы 22, 24 и 26 срабатывают по переднему фронту импульсов, поступа- кщих на их входы, а элементы 23, 25, 27 - по спаду импульсов, поступакядих на их входы. Длительность импульсов, сформированных на элементах 22, 24,

5

0

5 0 5

26, определяет величину задержки сигналов на первом, втором, третьем выходах блока синхронизации соответственно. Длительность импульсов, сформированных на элементах 23,25,27, определяет длительность сигналов на указанных выходах блока 13.

Отсутствие или наличие сигнала на втором выходе блока 13 синхронизации соответствует логическому О или 1 на первом управляющем входе 3 блока 9 и определяет режим его работы.

При наличии О на первом управляющем входе 3 блока 9 производится сложение поступившего на первые информационные входы блока 9 кода адреса А с поступающим на его вторые входы кодов приращения адреса ПА с выходов блока 10.

При наличии 1 на первом управляющем входе 3 блока 9 происходит вычитание из кода А, кода ПА с использованием обратного кода.При сложении код ПА с выходов блока 10 поступает на второй вход коммутатора 17 и с его выхода - на второй вход сумматора 18, при этом обратный код ПА с выходов группы инверторов 16 на выход коммутатора 17 не проходит, таК: : как на втором входе блока 17 присутствует сигнал логического О. Результат суммирования А + ПА с первого выхода сумматора 18 и возможный при переполнении разрядной сетки сигнал переноса с второго выхода сумматора 18 заносятся по времени переднего фронта сигнала на вто- ром выходе блока 13 в регистр 1 и первый триггер 20 соответственно.

При вычитании, так как на третьем входе блока 17 присутствует сигнал логической 1, код ПА поступает на второй вход сумматора 18 через группу инверторов 16 и первый вход коммутатора 17.

Сигнал на входе знакового разряда второго слагаемого ПА (четвертый вход сумматора 18) определяется сигналом на первом управляющем входе 3 блока 9 и в режиме вычитания соответствует 1. Элемент И 19 разрешает прохождение возможного сигнала циклического переноса с второго выхода сумматора 18 в его 4лaдший разряд (вход 5 сумматора 18). При этом знаковый разряд первого слагаемого - кода А (третий вход сумматора 18) - в любом режиме равен О.

Результат вычитания А , - ПА с первого выхода сумматора 18 и значение знакового разряда с третьего выхода сумматора 18 заносятся во второй регистр 4 и второй триггер 21 соот- ветственно по сигналу с третьего выхода блока 13.

В следующем цикле при поступлении очередного сигнала на управляющий вход 12 устройства в регистр 8 адреса заносится новое значение кода адреса Af,., с адресных входов 11 устройства. Код адреса А с выходов регистра 8 адреса поступает на вторые входы схем 2 и 3 сравнения,на первых входах кото- рых присутствуют подготовленные в предьщущем цикле и хранящихся на регистрах 1 и 4 коды А + ПА и А - ПА соответственно.

Выходные сигналы логической 1 на схемах 2 и 3 сравнения формируются при вьшолнении условий А„, А, + ПА или - ПА соответственно и поступают на первые входы соотнетст- вующих элементов И 15 и И 14.

f.

При наличии разрешакядего сигнала логической 1 на втором ходе эле- ментов И 14 или И 15 сигнал через элемент ИЛИ 3 поступает на первый вход элемента И 6. При поступлении сигнала с первого входа блока 13 на второй вход элемента И 6 на его выходе и соответственно на выходе 7 устройства формируется сигнал Преры вание. Разрешающий сигнал логическо 1 на вторые входы элементов И 15 или И 14 поступает с инверсных выходов триггеров 20 и 21 соответственно при отсутствии 9 предыдущем такте ра боты устройства на втором выходе сумматора 18 сигнала Перенос в режиме сложения и отсутствии 1 в знаковом разряде (третий вькод сумматора -18) режиме вычитания.

Технико-экономический эффект от использования изобретения по сравне- нию с прототипом заключается в сокращении времени при отладке программ за счет формирования прерывания не при каждом вьтолнении команды перехода,а только при реализации в програм- перехода с приращением адреса, большим заранее заданного, т.е. со- кращается время отладки контрольных вариантов задач за счет сокращения числа прерываний в программе в процессе отладки.

Формула изобретения

Устройство длл прерывания при отладке программ, содержащее первый и второй регистры, первую и вторую схемы сравнения, первый, второй и тре- тий элементы И, регистр адреса, регистр приращения адреса и элемент ИЛИ, причем информационные выходы первого и второго регистров соединены с первыми входами соответственно первой и второй схем сравнения, информационный выход регистра адреса соединен с вторыми входами первой и второй схем сравнения, выход Больше первой схемы сравнения соединен с первым входом второго элемента И, адресный вход устройства соединен с информационным входом регистра адрес вход запуска устройства соединен с входом записи регистра адре еа, выход элемента ИЛИ соединен с первым входом первого элемента И, выход которого является вькодом прерывания устройства, отличающееся тем, что, с целью повьшения быстродействия, в устройство введены блок синхронизации и арифметический блой, содержащий сумматор, коммутатор, элемент И, группу элементов НЕ, первый и второй триггеры, причем выход Меньше второй схемы сравнения соединен с первым входом третьего элемента И, выходы второго и третьего элементов И соединены соответственно с первым и вторым входами элемента ИЛИ, вход запуска устройства соединен с входом запуска блока синхронизации, первый выход которого соединен с вторым входом первого элемента И, второй выход блока синхронизации соединен с входом записи первого регистра, тактовым входом сумматора, первым входом элемента И,уп- равлякщим входом коммутатора и первым установочным входом первого триггера, третий выход блока синхронизации соединен с входом записи второго регистра и с первьм установочным входом второго триггера, информационный выход регистра адреса соединен с входом первого операнда сумматора,информационный выход сумматора соедине с информационными входами первого и второго регистров,выход регистра приращения адреса соединен с первой группой информационных входов коммутатора и через элементы НЕ группы с второй группой информационных входов коммутатора, выход которого соединен с входом второго операнда сумматора, выход переполнения сумматора соединен с вторым установочным входом первого триггера и вторым входом элемента И, выход которого соединен с

входом циклического переноса сумматора, выход значения знакового разряда сумматора соединен с вторым установочным входом второго триггера,выходы первого и второго триггеров соединены с вторыми входами второго и третьего элементов И соответственно.

ipuf.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1986 |

|

SU1363221A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

| Устройство для отладки программ | 1989 |

|

SU1674135A1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

| Устройство для отладки программ | 1983 |

|

SU1104521A1 |

| Устройство для обмена информацией управляющей вычислительной машины с объектами управления | 1982 |

|

SU1030792A1 |

| Устройство для отладки программ | 1988 |

|

SU1624461A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

Изобретение относится к цифровой вычислительной технике и предназначено для использования при отладке программ спе1шализированньгх вычислительных систем реального времени. Цель изобретения - сокращение времени отладки программ путем формирования сигнала прерьшания при реализации в программе перехода с заданным приращением адреса команды. Цель достигается Тем, что кроме первого и второго регистров, регистра прираге- ния адреса, схем сравнения, регистра адреса, злементов И и ИЛИ, в устройство введены арифметический блок и блок синхронизации. Сущность изобретения заключается в том, что на каждом шаге выполнения программы вычисляется приращение адреса как абсолютная величина разности последующего и предыдущего адресов и сравнивается с заранее заданным допустимым прира- 1цением адреса команды. Если адрес выходит за границы диапазона, то формируется сигнал прерывания. 3 ил. (Л

.JРедактор И. Касарда

Составитель И. Сигалов

Техред И.Попович Корректор Л. Патай

Заказ 4722/53Тираж 671 . Подписное

ВНИШШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Рауиская наб,, д. 4/5

ц,,д,П.- -..

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

fPuff.3

| Веникодробильный станок | 1921 |

|

SU53A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для прерывания при отладке программ | 1980 |

|

SU962945A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-30—Публикация

1985-01-16—Подача