Изобретение относится к области вычислительной техники и может быть использовано при отладке программ специализированных цифровых вычислительных систем (СЦВС) реального времени.

Цель изобретения - расширение области применения.

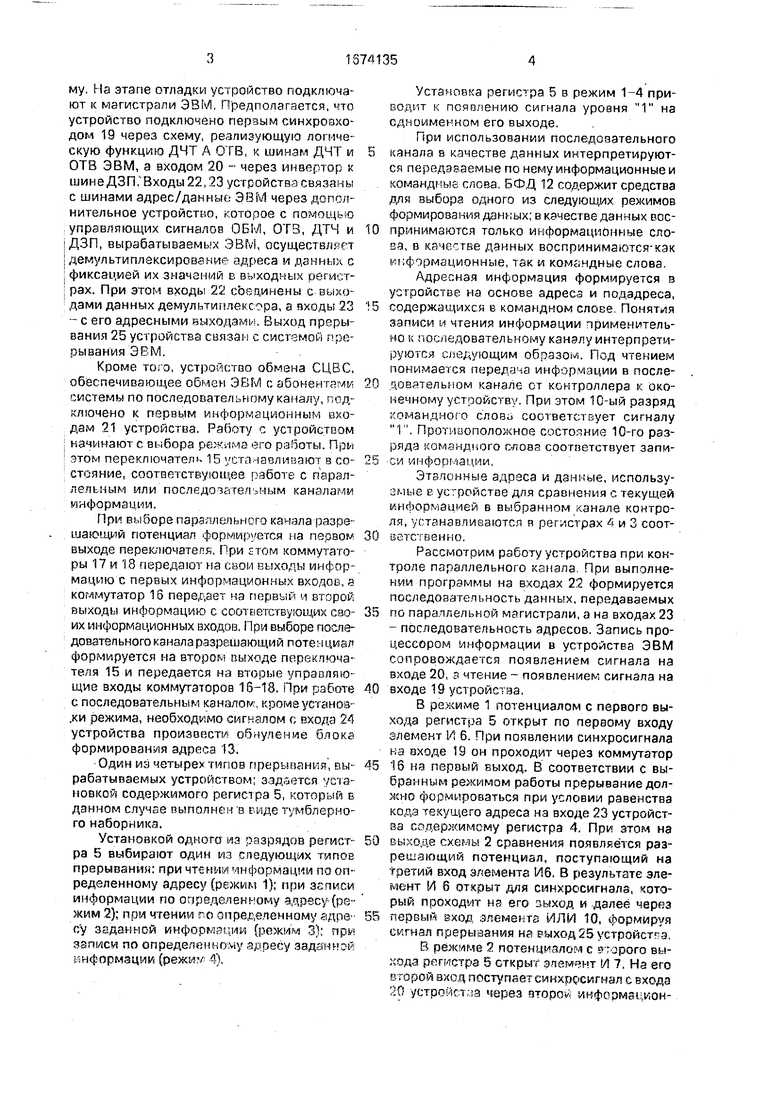

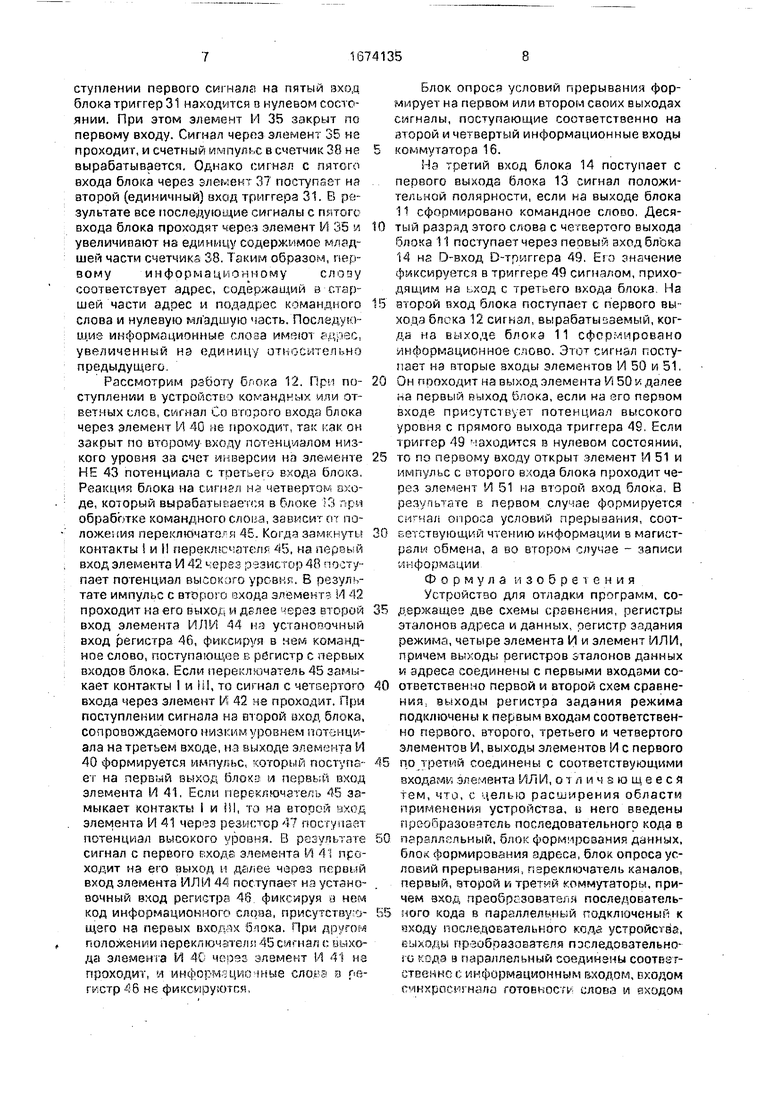

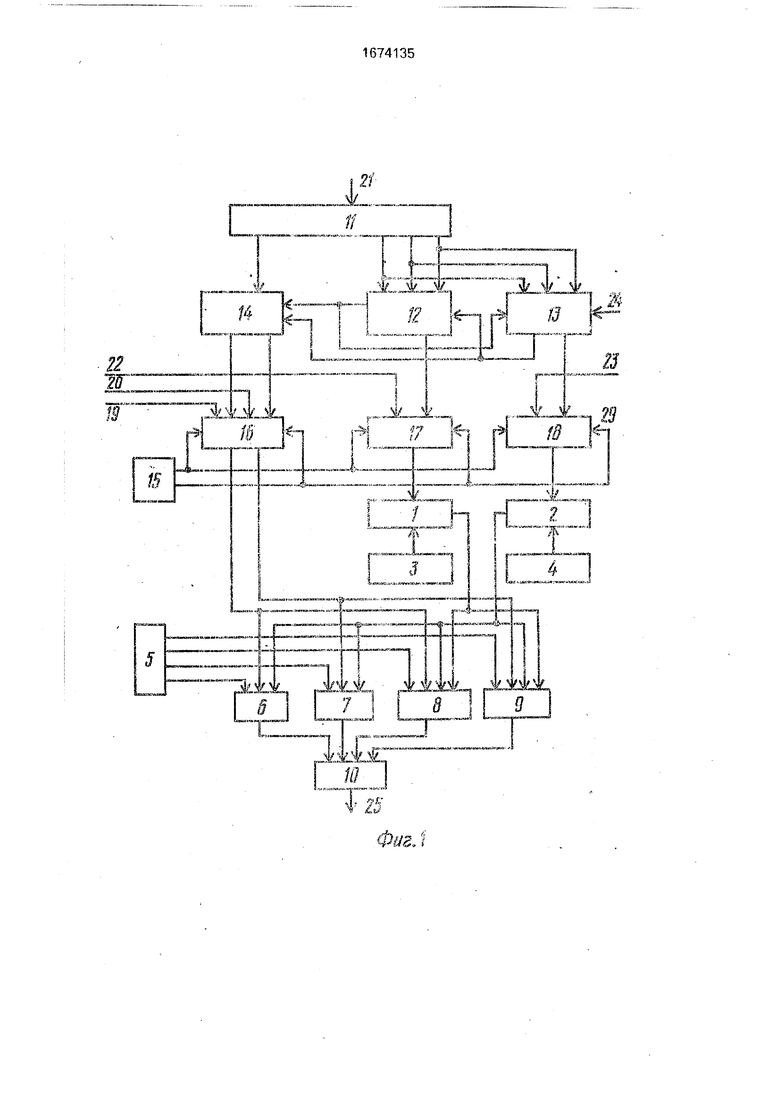

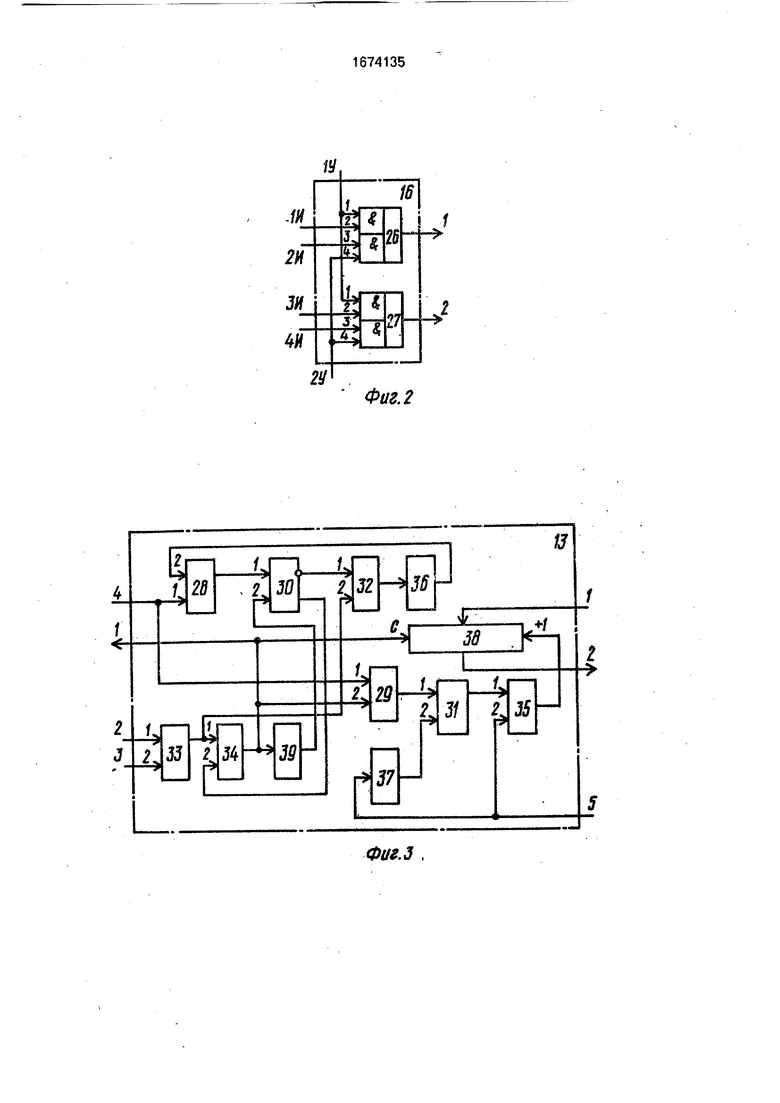

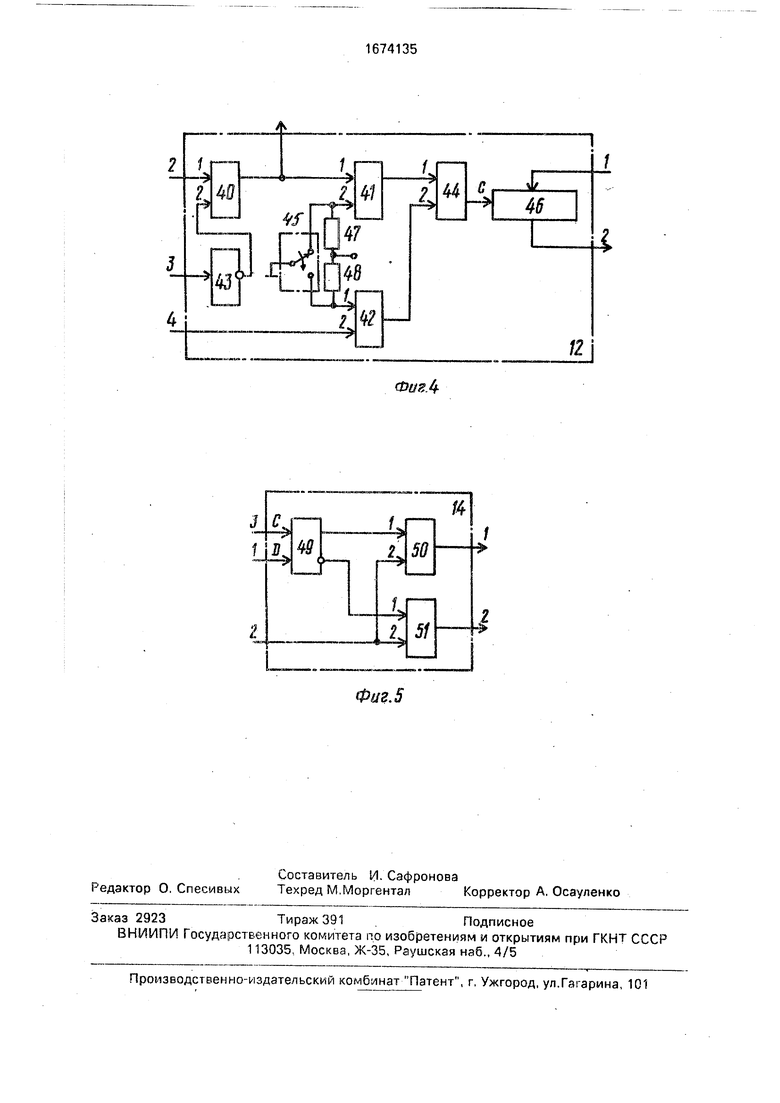

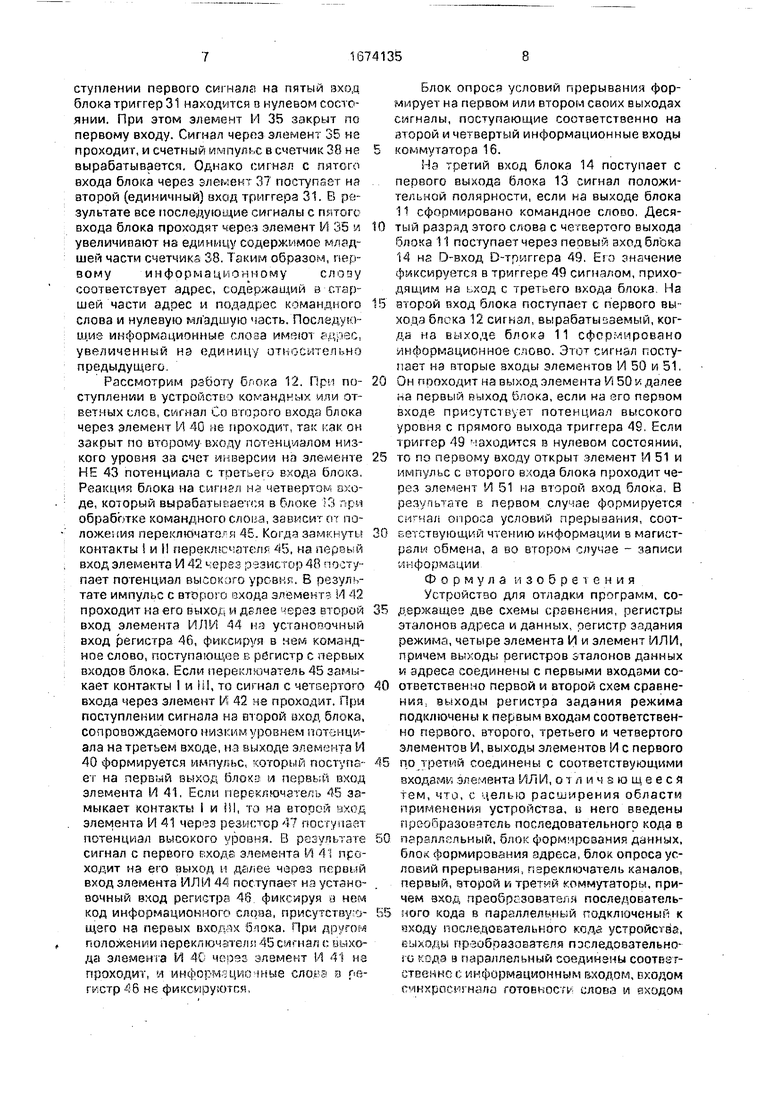

На фиг. 1 изображена структурная схема устройства; на фиг.2 - схема коммутатора 16; на фиг.З - схема блока формирования адреса; на фиг.4 - схема блока формирования данных; на фиг.5 схема блока опроса условий прерывания.

Устройство содержит первую схему 1 сравнения, вторую схему 2 сравнения, регистры 3,4, эталонов данных и адреса, регистр 5 задания режима, первый 6, второй 7, третий 8 и четвертый 9 элэменты И. элемент ИЛИ 10, преобразователь 11 последовательного кода в параллельный, блок 12 формирования данных (ВФД), блок 13 формирования адреса (БФА). блок 14 опроса условий прерывания (БОУП), переключатель 15 каналов (ПК), коммутаторы 16-18, входы чтения и записи 19, 20 устройства, первый 21, второй 22 информационные входы устройства, адресный вход 23 устройства, вход 24 начальной установки и выход 25 прерывания устройства.

Коммутатор 16 содержит первый 26 и второй 27 элементы 2-2И-ИЛИ.

Блок формирования адреса содержит элементы ИЛИ 28. 29, триггеры 30, 31, элементы И 32 35, элементы 36, 37 задержки, счетчик 38 адреса и элемент 39 задержки.

Блок 12 формирования данных содержит элементы И 40-42, элементы НЕ 43, элемент ИЛИ 44, переключатель 45, регистр (данных) 46, токоограничительные резисторы 47, 48.

Блок 14 опроса условий прерывания содержит D-триггер 49, элементы И 50. 51

Рассмотрим работу устройства совместно с СЦВМ на базе ЭВМ типа Электроника 60 реализующей отлаживаемую програмЁ

О

VI J

со ел

му. На этапе отладки устройство подключают к магистрали ЭВМ. Предполагается, что устройство подключено первым синхроохо- дом 19 через схему, реализующую логическую функцию ДЧТ А ОТВ, к шинам ДЧТ и ОТВ ЭВМ, а входом 20 - через инвг-ртор к шине ДЗП. Входы 22,23 устройства связаны с шинами адрес/данные ЭВМ через дополнительное устройство, которое с помощью управляющих сигналов ОБМ, ОТВ, ДТЧ и ДЗП, вырабатываемых ЭВМ, осуществляг-т демультиплексирование адреса и данннх с фиксацией их значений в выходных регистрах. При этом входы 22 соединены с выходами данных демультиплексора, а чходы 23 - с его адресными выходами. Выход прерывания 25 устройства связан с системой прерывания ЭВМ.

Кроме то:э, устройство обмена СЦВС, обеспечивающее обмен ЭВМ с абонентами системы по последовательному каннлу, подключено к первым информационным входам 21 устройства. Работу с устройством начинают с выбора режима его работы. При этом переключатель 15 устанавливают в состояние, соответствующее работе с параллельным или послрдозагельным каналами информации.

При выборе параллельного канала разрешающий потенциал формируется на первом выходе переключателя. При этом коммутаторы 17 и 18 передают на свои выходы информацию с первых информационных входов, а коммутатор 16 передает на первый ч второй выходы информацию с соответствующих своих информационных входов. При выборе последовательного канала разрешающий потенциал формируется на втором выходе перг- пюча- теля 15 и передается на вторые упрасляю- щие входы коммутаторов 16-18. При рлботе с последовательным каналом, кроме установ- .ки режима, необходимо сигналом с входа 24 устройства произвести обнуление блока формирования адреса 13.

Один из четырех типов прерывания, вырабатываемых устройством; задается установкой содержимого регистра 5, который в данном случае выполнен в виде тумблерного наборника.

Установкой одного из разрядов регистра 5 выбирают один из следующих типов прерывания: при чтении информации по определенному адресу (режим 1); при записи информации по определенному адресу (режим 2); при чтении по определенному чдое су заданной информации (режим 3} при записи по определенному адресу заданной информации (режим 4),

Установка регистра 5 в режим 1-4 при- содит к появлению сигнала уровня 1 на одчоименном его выходе.

При использовании последовательного

канала в качестве данных интерпретируются передаваемые по нему информационные и командные слова БФД 12 содержит средства для выбора одного из следующих режимов формирования данных; в качестве данных РСС0 принимаются только информационные слова, в качестве данных воспринимаются-кэк ш;4 трмационные, так и командные слова

Адресная информация формируется в устройстве на основе адреса и подэдреса,

5 содержащихся в командном слосе Понятия записи и чтения информации применительно к последовательному каналу интерпретируются следующим образом. Под чтением понимается пере/1-) -,а информлции в после0 новотельном канале от контроллера к оконечному устройств. При этом 10-ый разряд /омандною слово соответствует сигналу 1 . Противоположное состояние 10-го разряда командного слова соответствует запи5 i ,i инфоиг 1апии

Эгапснные адреса и данные используемые с устройстве для сравнения с. текущей информацией в выбранном канале контроля, vi т ч на впиваются R регистрах 4 и 3 соот0 БОК Г бННО

Рассмотрим работу устройства при контроле параллельною канала. При выполнении программы на входах 22 формируется последовательность данных, передаваемых

5 по паргпле 1ьной магистрали, а на входах 23 - последовательность адресов. Запись процессором информации в устройства ЭВМ «-дпровождается появлением сигнала на входе 20, з чтение - появлением сигнала на

0 входе 19 устройства.

В р. 1 потенциалом с первого выхода регистра 5 открыт по первому входу слемент И 6. При появлении синхросигнала nj входе 19 он проходит через коммутатор

5 16 на первый выход. В соответствии с выбранным режимом работы прерывание должно формироваться при условии равенства кода текущего адреса на входе 23 устройства содержимому регистра 4. При этом на

0 вькоде схемы 2 сравнения появляется разрешающий потенциал, поступающий на третий вход элемента И6. В результате элемент И 6 открыт для синхросигнала, который проходит нз его зыход и далее через

5 первый вход элемента ИЛИ 10, формируя сигнал прерывания на РЫХОД 25 устройства R режиме потенциалом с рторого выхода регистра 5 открыт элемент И 7 На его второй вхсд поступает синхросигнал с входа 20 устрлигто чирез пторо информацией1:UP С-.)/ И В ОГ.Н.Й f-i:iXGU - 0 1:--у . итор. 10.

При Г; :OF) равенства те „чего п эт.-./юи ного дд-jecoE, провар 1,- которого осу.ц,чстн- яясг о - емг 2 сравнение-, не г:е Формируется ра-юешзющ й потенциал. Б результате элемент И пропусмо по г го- рому входу -.ч- н ; рос I..и-:: л. ;;иторым через второй вход d CMt rtTO i-nl-i qO лостугv-o м ./Гг., Ц-,:ХОД, ФОР ЛНР /Я СИГ :.- Пр: ; ЬТ:-г -МГ МП

соответствующем оыход v и;. ;: л

В ОО.КИмд Р СГг( ЧО;.;ИЯ , руеГСГ Г.:. И ;рОХС;,(ПИ i.::. ЧЯ;. . , первого Бо1;:ПД-, XOMMV, 1 -,Up .::-, F/iO

рой вход элс о-:11й И Н ; ;j.:: -en )-.-;: т- aiw ь. Од элемент ИЛИ 10 на .ьг-ид ..5 уел;.- : in перчом аходе И Р рз.|ч UJ йюи-. и С: .оте;:ц.- .- обес ме -i.: из... г : Р СИ: К..-10f г. vc.-c-П.п; f.1 ;.;.:-ч.и . г.:-i-.ipa и h ,. третьем ьходе э:н:мен . - i-1 8 j /оЗ;.:1;: ,.;..;- форг 1,гуегся сиги,.. i f.i . n li in пси coijn;V,PHHH . i U-ro : ;r ,Q .i()ro адресно. На четь::ртсм E;/.-- (.. . потенциал формируется ПРИ - е : у:цего значении длины ,;: M/C/VJ. 2.v i ройства с эталоном д-зып,:д . ,.--0( в ос; и с: г ре 3.

I 1рИ ЧГОМ ДаНМЫ ; С i1. 22 V /T iV; .; I П.-,

поступаю через первые p - - .-ie входм коммутатора 17 нл с-г - 1-ыт-.ы (1 i-ao вю;)ыь инфорг -;ц г,)-1;-;., г... - .-ч

МЫ 1 , tir, r i;pli . - iJ/ОЛ-1 ПС.Ч/ГуП, 1-- ЛТЛ ЮНН н ГЛЛ г м:Г1- :.рт 3. При patr-:icn:e . (,;-. ний pa3peiua«GLHi.;fi :зтги. и я /.. .:.,/;: схемы 1 срапно::ия на ,о ; .-;( т;.-| :- ьход -гемеига 1х 8. При нмпплнон : i..r уследи: прерывания . HC.I г PODBO- го выхода коммутатора 16 мьоодиг сторой вход элемент-j И Я на его ььио; и далее через третий вход ; лемеь га ИЛИ ji на выход 25 устрпйстьо.

В режиме 4 выраЬат .лр-етея разрешаю щий сигнал на одноименном ;.г,1/:оде регистра 5. Этот сигнал открыг.ге; лвсиент И 9 по первому входу. На тpf i.-,;M i четпг:рто RXO- дах элемента И Э ра реИ Я ОЩ -. п тинпиа- лы вь рапотываю гя i;ti .е. к.:. и в f/ожпмо 3, при совпдаен1 1 с тталонаг-п- г . значений адреса и данны/. Ь камео СЛЬ-С- Р - сигнала используется с. гнал с охора 20 усгройсть Он прохс/ , м -еледовате/ii ю чераз третий информ. :bif вход is пи- рой РМХСД комму аг .р, i j. горой j-хс.д и выход элемента ;/ У i четасрт1: Р вход и BLIXO..э a lir:i/i 10 и;: ьых vi ;5 пещеры- впний усфа.1.ти. :.

o6pf;;-.. C-a ;.;jih i 1 преи .....--цчуот и,--- Ф 0,зцию. пс;сту оЮи1ую ;;з ого ; o njiic с ь. ог- . i ельн JFO .j чс . .- одм 21 ус роистой, ь пар ляо/ bHt.-ih ..:,,:

i1 -...-..г- С in-ir. р.0от; блока 1Г. ь его г. ;:..--.ч т;-и те 1ы °. . 31 ус.гана.злива;: Сс; и ИС.ХПДНОе :jOf; O l ,1в СИГНЭЯОМ, ПОСТупзю мим с ч ;тиор -. ПУОЦ:.- блока 13 через i np;3t-. пход -i з/1 . / ЛИ 28 и 29 на

.;|:::ь й (единичный) вход тр irrep.T 30 и пером. (нулр.) ь-ход триггера ; i 0 результате

Р ге;ч 30 усгаг.-оилийй-этся о единпм пв, а тл..гп. и 31 - в нулевое сопсячие. При по- - -;i онии ч блок -;рез о горой зход пог.оки- т... HMfiyii.ra, го,.порождающего ; ,,..., и-пи с тпетное .локо, он проходит i;и,..- ньрт ый вх л. г.-.1- ента 11 33 не ею н: : и ai:FO (Я пермый тход элемента И 3, j-if p.Di t L:xo, i которого огкрьгг положи- чг. ; -ч..м поч;Н1.1иэпом с пп; мого выхода Т / rep - 30. Сигь-э/ г. выхода племен :i И 33

..... , г :. : OL ГХГД i IGMRt. a И 3° НЭ ПрОХО- , p:l. TdK КОК Of О МО ВЫЙ ВХОД ,1КОЫТ

, .F-i-i, ., i.-isep. ного и хода триггера 30. В Р . зу/ц.т -лг-1 и л выходе элемента 11 ,14 форми- рут;.с,., ,10.. :,-.1 игольный импу/ ь ;. сигнамиоИ- руш..W: :. о т м. ,гг на .о.м,в б; ока

Т) iCyTC: г:, ;; : ОД К ON аНДгК .; СЛОиа. JrOT

си;;.; i посту. 13.: н-i первый е..|ход блока и : мг;з „юрой - ход элемента ИЛИ 29 - на в- j. 961 у- зния триггера 31. Э Oi же сигнал г. (-, ;.- 1емен-а 11 34 поступает на уста- ч,.ч:: iuP / ,д с етчи-:а 38 и фиксирует в кем iiH pc.pi, г.,:,.:ю, поступающую в счетчик с П( ..хоув блок.ч. При том младшая . / пгчми (.г г;ога ощяя в с . Лнсм ре- : ioiiy -.-..i .;.i. вс1Яр1м й, работзюидей FJ. j е с р;;ипм р 3жи;1ё фиксируется адрес v м .,-цоес. входящие в состав командного c/ O i,). Кроме того, сигнал г. выхода элемента И ГИ Ч .р .:.) элемент 3:, проходит на второй Pi,;:.: .)) чхсд гргггерэ 30. сбрасывая его в isyfcodd с рстсяние Когда на второй вход бло.:а )3 приходит следующий сигнал, сое- н.д;; (.. с положительным уровнем сигнала на третьем входе блока, это означает, что на информационных входах блока присутствует отвегное слоьо, несупдее информацию, ьк используемую устройством. В результате сигнал с выхода элемента И 33 через эле- мен1 I 5 4 не проходит, так как его второй FJ ../i ; ;, ыт сигналом с прямого пыхода триггера 30, нзходчидегося в нулевом состоянии. 0.1гна.т с выхода дломанта И 33 прохо- ..и 1 рс : второй вход элемента И 32 на его в.и.од ti далее- -г,ре ; элемент 36 и второй вход пемонта ИЛИ 28 на единичный (пер- оый) г;ход триггера 30. перебрасывая его в :мн :|: -типе состоят -1.

. ри поступлении на пятый нход положа тел Ь:.ого сигнала, вырабатываемого блоком 12 пои обработке информационного слова, cyi U-CT :/rji два режима его , за- i. U,e от состо-. ния триггера 31. При поступлении первого сигнала на пятый вход блока триггер 31 находится в нулевом состоянии. При этом элемент И 35 закрыт по первому входу. Сигнал через элемент 35 не проходит, и счетный импульс в счетчик 38 не вырабатывается. Однако сигнал с пятого входа блока через элемент 37 поступает на второй (единичный) вход триггера 31. В результате все последующие сигналы с пятого входа блока проходят через элемент И 35 и увеличивают на единицу содержимое младшей части счетчика 38. Таким образом, первому информационному слову соответствует адрес, содержащий в старшей части адрес и подадрес командного слова и нулевую мл адшую часть. Последующие информационные слова имеют рдрес, увеличенный на единицу отигл.ите н.но предыдущего

Рассмотрим pabory бло/.а 12. При поступлении в устройство командчм/ ипи ответных слов, сигнал Со второго ихода блока через элемент И 40 не проходит так как он закрыт по второму входу потенциалом низкого уровня за смет инверсии на элементе НЕ 43 потенциала с третьего входа блока. Реакция блока на сигнал на четвертом БХО- де. который вырабатывается в блоке 3 при обработке командного слова, зависит сп по- ложемия переключателя 45. Когда замкнуты контакты I и II переключателя 45, на первый вход элемента И 42 через резистор 4В посту пает потенциал высокого уровня. Б результате импульс с второ о охода элемента и 42 проходит на его выход и далее через второй вход элемента ИЛИ 44 на установочный вход регистра 46, фиксируя в нем командное слово, поступающее в регистр с первых входов блока. Если переключатель 45 замыкает контакты I и II, то сигнал с четвертого входа через элемент И 42 не проходит. При поступлении сигнала на второй вход блока, сопровождаемого низким уровнем потенциала на третьем входе, на выходе эгемонта И 40 формируется импульс, который поступи ег на первый выход блока и пеовьй вход элемента И 41. Если переключатся 45 замыкает контакты I и HI, то на вюрсй нх.од элемента И 41 через резистор 47 поступает потенциал высокого уровня. В результате сигнал с первого входа элемента 11 4 I проходит на его выход и далее чорез первый вход элемента ИЛИ 44 поступает нч установочный вход регистра 46, фиксируя в чем код информационною слова, присутстаую- щего на первых входах блока. При другом положении переключателя 45 сигнал с иыхо- да элемента И 40 через элемент И 41 не проходит, и информационные о регистр 46 не фиксируются.

Блок опроса условии прерывания формирует на первом или втором своих выходах сигналы, поступающие соответственно на второй и четвертый информационные входы коммутатора 16.

Но третий вход блока 14 поступает с первого выдода блока 13 сигнал положительной полярности, если на выходе блока 11 сформировано командное слово, Деся- тый разряд этого слова с четвертого выхода Плока И поступает через первы пхпд блока 14 ня 0-вход D-триггера 49. Ею онйчсние фиксируется в триггере 49 сигналом, приходящим на ьход с третьего входа бпокэ На 5 второй пход блока поступает с первого вы хода блекл 12 сигнал, вырабатываемый, когда на выходе блока 11 сформировано информационное с юво Этот поступает на вторые входы элементов И 50 и 51. 0 Он ппоходит на выход элемента И 50 v, далее на первый РЫХОД tV-.ока, если на ото первом входе присутствует потенциал высокого уровня с прямого выхода триггера 49 Если триггер 49 находится в нулевом состоянии, 5 то по первому входу открыт тлемент И 51 и импульс с иторою в сода блока проходит через элемент И 51 на второй вход гэлока. В pm. в первом слу tae формируется опроса условий прерывания, соот- 0 г..- лвующий чтению информации ъ магист- Р«Л1 обмена, а во втором спучяе записи информации

Формула изобретения У троистпо для отладки программ, со- В держащее две схемы сравнения, регистры эталонов адреса и данных, регистр задания режима, четыре элемента И и элемент ИЛИ, причем выходы оегистров эталонов данных и -эдреса соединены с первыми входами со- 0 ответственно первой и второй схем сравнения выходы регистра задания режима подключены к первым входам соответственно первого, второго, третьего и четвертого элементов И, выходы элементов И с первого 5 по третий соединены с соответствующими сходами элемента ИЛИ, отличающееся тем, что, с елью расширения области применения устройства, и него введены преопразоБ-тгсль последовательного кода в 0 пэррпл льный. блок форммрсвания данных, блок формирования адреса, блок опроса условий прерывания, переключателе каналов первый, второй и третий коммутаторы, причем вход преобргзователя после/юватель- 5 ного кода в параллельный подключены к чходу последовательного кода устройства, выходы преобразователя последовзтельно- io ксдя в параллельный соединены соотвег- стреинг, с инфсфмационным входом, сходом

ОЧНХрОСГ Hit/Id ГОТОВНОСТИ СЛОВО И ВХОДОМ

идентификации, блока формирования данных и информационным входом блока опроса услогий прерывания, первый и второй обходы блока формирования данных соединены состветстгечно с первым синхровхо- дом блока опроса условий прерывания и первым информационным входом первого коммутатора, второй информационный вход первого коммутатора подключен к входу параллельного кода устройства, первый и второй выходы блока фоомирования адро- са соединены соответственно с вторым синх- ровходом блока опроса условий прерывания и персым информационным входом второю шммутэгора, чторой информационней вход которого подключен к адресному вход/ устройства, информационные входы третьего чоммутзторас перио о почетвер.ый соединены соответственно с входами призна- Ой записи и чтения устройства и выхо.тами соска опроса условий прерывания, пор шй и вгорсй выходы переключателя каналов подключены соотпет твенно - первым и вторым управляющим входам коммутаторог, первый выход третьего коммутатора соединен с вторыми входами первого и третьего элементов И, второй выход третьего коммутатора соединен с вторыми входами второго и четвертого элементов И, выходы первого и второго коммутаторов соединены с вторыми входами соответственно первой и второй схем сравнения, выход второй схемы сравнения соединен с третьими входами элементов И с первого по четвертый, выход первой схемы с( авнения соединен с четвертыми входами TpeTiero и четвертого элементов И выход четвертсго элемента И соединен с четвертым входом элемента ИЛИ, выход которого является выходов прерывания устройства, выходы преобразователя последовательного кода в параллельный с первого по третий соединены соответственное информационным входом, входами признаков синхросиг- налэ готовности слова и идентификации блока формирования адреса, вход начальной установки которого подключен к входу начальной установки устройств, первый яычод блока формирования адреса соединен с синхровходом блока формирования данных, пеовый выход которого соединен с синхровходом блока формирования адреса, блок формирования данных содержит три элемента И, элемент ИЛИ, элемент НЕ, регистр, переключатель, два токоограничи- тельны/ резистора, причем первый вход первого элемзнта И является входом при- змзка командного слова блока, выход первого элемента И является первым выходом блок и соединен с первым входом второго элемента М, второй вход которого соединен

с iep6c M выходом переключателя и через первый гекоограт читальный резистор подключен тине единичного г.пчнциала блока, выход сторого элементя И соединен с 5 первым входом элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, первый вход котор«го соыдш ен с вторым выходом переключателя и чеоез второй токоограничительный резиггор

0 подключен к шине единичного потенциала у. т юйг,, второй вход третьего элемента И соединен с входом синхронизации бгокл, вход элемента НЕ является входом идснти Фи зции блока, о выход гоедлнен с вторым

5 первого элемента И, -ыход элемента ИЛИ соединен с входом устлчивки рргис - рд, ин4 ормациснный в/.од и вых зд которого чвл, ютс« соотьетс1венно HI. {юрмациоьным входом и вторым выход jv блока, вход пере0 кгючателп подключен к шине нулевого потенциала устройства блок формирование адргса содержит четыре элемента И, два элемента ИЛИ, два триггера, т ч и элемента задержчи, с гтчик адресе-, причем ni рьые

5 входы (lepaoro и второго зпементоо ИЛИ обьединены и подключены к входу начальной ycTdi овки блока, выход первою элемента ИЛИ (.оединен с единичным входом п ;OROfO 1 1лг jpa, инверсный выход которо0 го сседьчс и - первым входом первого элемента i/l, амход которого через первый элеме -i задержки соединен г, втопым вхо- iif первого элг/мента ИЛИ, первый и вто- ро входы аторого элемента И являются

5 соотзэтственно входом синхросигнала готовности и идентификации блока, выход второго элемента И соединен с первым входом третьею элемента И и вторым входом первого элемента И, выход третьего элемен0 та И через второй элемент задержки соединен с нулевым входом первого триггера, выход третьего элемента И соединен с вторым входом второго элемента ИЛИ, с синхровходом счетчика адреса и является

5 первым выходом блока второй вход третьего элемента И соединен с прямым выходом первого триггера, выход второго элемента ИЛИ соединен с нулевым входом второго триггера, единичный вход которого соеди0 мен с выходом третьего элемента задержки, вход которого соединен синхровходом и с первым входом четвертого элемента И, второй вход и выход которого соединены соответственно с прямым выходом второго

5 триггера и счетным входом счетчика адреса, информационный выход которого является вторым выходом блока информационный вход счетчика адреса является информационным входом блока

1

llH

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух вычислительных машин | 1980 |

|

SU922716A1 |

| Устройство для сопряжения двух вычислительных машин | 1985 |

|

SU1315987A1 |

| Устройство для обмена данными между источником и приемником информации | 1988 |

|

SU1557566A1 |

| Устройство для сопряжения двух вычислительных машин | 1987 |

|

SU1474665A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2029359C1 |

| Устройство для ввода информации | 1987 |

|

SU1539761A1 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1777145A2 |

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Устройство для синхронизации распределенной вычислительной системы | 1988 |

|

SU1508201A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

Изобретение относится к вычислительной технике и может быть использовано при отладке программ специализированных цифровых вычислительных систем реального времени. Цель изобретения - расширение области применения. Это достигается за счет систем, реализующих отлаживаемые программы, не обеспечивающих доступ отладочных средств к параллельным каналам обмена информацией и позволяющих подключение к последовательным каналам, что приводит к повышению производительности работы по отладке программного обеспечения вычислительных систем. 5 ил.

rV

I D ,, I -. E--j p

«rH «r- U.

к,

Сл i

-4- 1Ь1 4 S

J;

:,i

CO

г

5

JU

T

J I

Г- П i i M

w

U L

i

k- 1

4 U-4l trrl

I ( iV г -. j

NO

o -j

Xi CO

ел

Г ГП lit

Hf И

i i

д .

i UJ -% 1ь«

So

.t-t

iii i i L

«s

I

7J

I

- -

M ,

Фиг4

Фиг. 5

| ВОЛНОВАЯ МУФТА | 0 |

|

SU213482A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для прерывания при отладке программ | 1980 |

|

SU962945A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

Авторы

Даты

1991-08-30—Публикация

1989-02-13—Подача