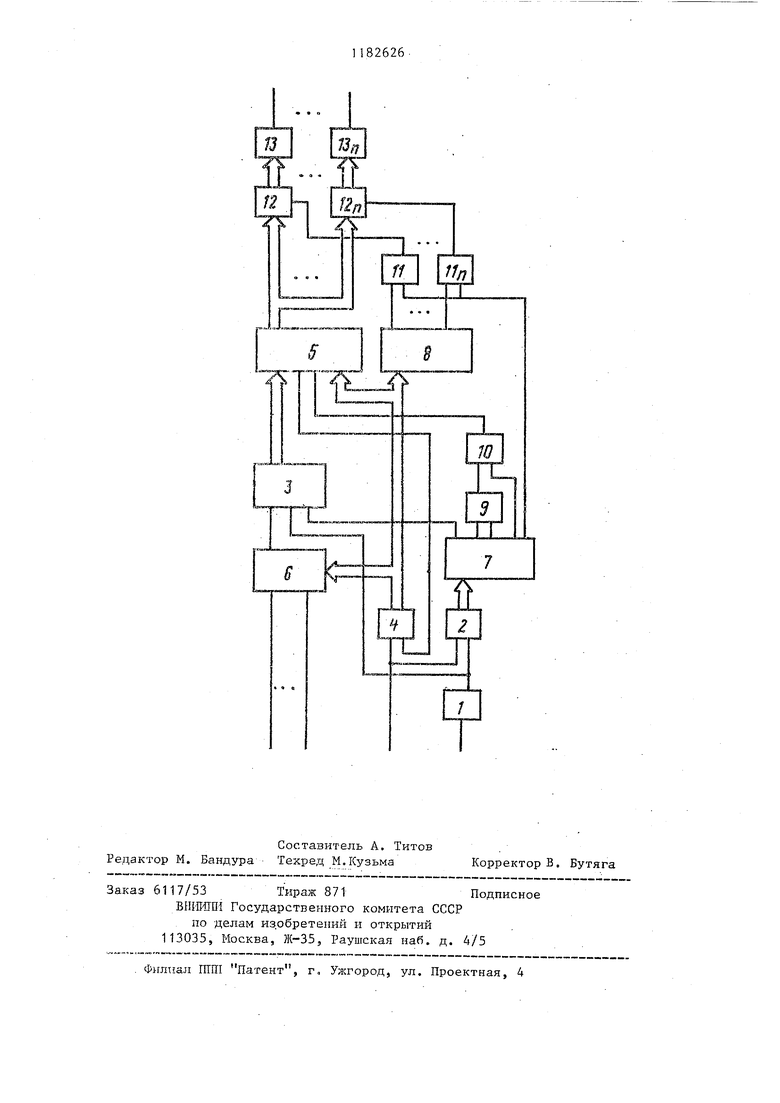

ИзобретёТние относится к аналого-цифровой технике и может быть использовано ь корректирующих фильт рах автоматических систем для сдвига фазы аналоговых сигналов управления. Цель изобретения - расширение функционалылЕс возможностей устройства задержки за счет обеспечения управления величиной задержки нескольких независимых , аналоговых сигналов. - На чертеже приведена функциональная схема аналого-цифрового устройства задержки. Аналого-цифровое устройство задсрк;.,н со/лержпт преобразователь напр женне - частсзта 1, первый счетчик 2, аналого-цифровой преобразователь 3, второй счетчик 4, оперативно запоминающее устройство 5, мультиплексор 6, первый дешифратор 7, второй дешифратор 8, RS-триг гер 9, элемент 2 ИЛИ 10,п злементов 2 И 11,п регистров 12 и пцифроаналоговых преобразователей 13. Выход преобразователя напряжение частота 1 подключен к входам первого счетчика 2 и аналого-цифрового преобразователя 3, установочные вхо ды счетчиков 2 и 4 объединены, выходы счетчика 4 подключены к входам оперативного запоминающего устройства 5, мультиплексора 6 и дешифратора В, а выходы счетчика 2 подключены к входам дешифратора 7, а такж к входу счетчика 4 и оперативного запоминающего устройства 5, другие входы которого подключены соответст венно к выходам аналого-цифрового преобразователя 3, входы которого соединены соответственно с выходом мультиплексора 6, с выходом преобразователя напряжение - частота 1 и с выходом дешифратора 7, другие выходы которого соединены соответст венно с входами RC-триггера 9, элемента 2 ИЛИ 10, другой вход которого подключен к выходу RC-триггера 9, а выход - к управляющему вход оперативного запоминающего устройства 5, и - к одним входам элементов 2 И 11, другие йходы которых соединены с выходами дешифратора 13, а выходы - к управляющим входам регистров 12, информационные входы которых подключены к выходам опера|гив1.ого запоминающего устройства5, а выходы к входам цифроаналоговых преобразователей 13. Аналого-цифровое устройство задержки работает следующим образом. В момент включения устройства импульс начальной установки поступает на R -входы первого 2 и второго 4 счетчиков и обнуляет их. Импульсный сигнал, частота которого определяется уровнем аналогового сигнала на входе управления устройства, с выхода преобразователя напряжение - частота 1 поступает на С-вход первого счетчика 2, который осуществляет пересчет импульсов, и на С-вход аналого-цифрового преобразователя 3. Изменение содержимого второго счетчика 4 происходит по заднему фронту импульса, поступившего на его СЕ-вход с выхода старшего разМ ряда первого счетчика 2. На входы мультиплексора 6 поступают аналоговые сигналы, задержку , которых необходимо осуществить в устройстве. Управление мультиплексором 6 осуществляется импульсными сигналами на выходах соответствующих младших разрядов второго счетчика 4. Аналого-цифровой преобразователь 3 осуществляет преобразование уровня аналогового сигнала на его входе в цифровой код. Начальная установка аналого-цифрового преобразователя 3 осуществляется импульсньм сигналом на первом выходе первого дешифратора 7, Запись кода, сформированного на выходах аналого-цифрового преобразователя 3, в оперативное запоминающее устройство 5 осуществляется по адресу, код которого сформирован на выходах второго счетчика 4. Режим работы оперативного запоминающего устройства 5 определяется логическим уровнем импульсного сигнала на выходе старшего разряда первого счетчика 2, а выборка оперативного запоминающего устройства 5 в режимах записи и считывания информации осуществляется импульсным сигналом на вькоде элемента 2 ИЛИ 10. Формирование сигнала выборки оперативного запоминающего устройства 5 в режиме считывания осуществляется с помощью RC-триггера 9, управляемого импульса3ми на втором и третьем выходах пер вого дешифратора 7. . Каждому аналоговому сигналу на входах устройства задержки соот ветствуют определенные ячейки памя оперативного запоминающего устройс ва 5, в которые последовательно за ишсываются коды уровней соответстВ5ТОЩИХ аналоговых сигналов в опред ленные моменты времени. Считывание информации из оперативного зап минающего устройства 5 в соответствующий из п регистров 12 осуществляется по адресу, код которого сформирован на выходах второг счетчика 4, во время формирования кода на выходах аналого-цифрового преобразователя 3.Таким образом, цикл обращения к оперативному запоминающему устройству 5 в каждом нале состоит из считывания и запис информации по соответствующему адр су. Величина задержки аналоговых сигналов,t,, в устройстве определяется выражением , где N - количество ячеек памяти, зарезервированных в оперативном запоминающем уст ройстве 5 под информацию в каналах устройства заде ки - тактовая частота импульсн ного сигнала на выходе преобразователя напряжени -частота Ij 64. k - количество тактов в цикле обращения к оперативному запоминающему устройству 5, д1с - количество тактов между импульсами выборки оперативного запоминающего устройства 5 в пределах цикла обращения, Т - время преобразования кода в уровень сигнала в цифроаналоговых преобразователях 13. Между каналами устройства задержки и п регистрами 12 существует взаимно однозначное соответствие, так как входы второго дешифратора 8 соединены с соответствующими входами управления мультиплексора 6, В каждый из п регистров 12 по переднему фронту импульса, поступившего на его С-вход с пятого выхода первого дешифратора 7 через соответствующий элемент 2 И 11, записывается информация из ячеек памяти оперативного запоминающего устройства 5, соответствующая одному из каналов устройства, с помощью цифроаналоговых преобразователей 13, осуществляющих преобразование кодов на выходах соответствующих п регистров 12 в соответствующие уровни сигналов, в:ходные аналоговые сигналы воспроизводятся на соответствующих выходах устройства с задержкой, величину которой можно изменить в процессе работы устройства соответствукицим изменением уровня аналогового сигнала на входе управления устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное аналого-цифровое устройство задержки | 1983 |

|

SU1256150A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Многоканальное устройство для ввода информации | 1989 |

|

SU1633383A1 |

| Цифроаналоговая система сбора и обработки информации | 1986 |

|

SU1363271A1 |

| УПРАВЛЯЮЩИЙ АППАРАТНО-ПРОГРАММНЫЙ КОМПЛЕКС ДЛЯ ОБРАБОТКИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 2001 |

|

RU2222028C2 |

| Формирователь сложной функции | 1982 |

|

SU1107293A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1995 |

|

RU2096801C1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

АНАЛОГО-ЦИФРОВОЕ УСТРОЙСТВО ЗАДЕРЖКИ, содержащее п цифроаналоговых преобразователей, выходы которых являются выходами устройства задержки, отличающееся тем, что, с целью расширения функциональных возможностей устройства задержки за счет обеспечения управления величиной задержки нескольких независимых аналоговых сигналов, в него введены преобразователь напряжение - частота, два счетчика, два дешифратора, R5-триггер, элемент 2 ИЛИ, мультиплексор, аналого-цифро вой преобразователь, оперативное запоминающее устройство, п элементов 2 И и п регистров, выходы которьк соединены с соответствующими входами соответствующих цифроаналоговых преобразователей, информационные входы - с соответствуюыщми выходами оперативного запоминающего :устройства, а С-входы - с выходами ;соответствующих элементов 2 И, при,чем D -входы оперативного запоминающего устройства соединены с соот- , ветствующими выходами аналого-цифрового преобразователя, С-вход - с выходом элемента 2 ИЛИ, вход управления режимом работы с вьгходом старшего разряда первого счетчика и СЕ-входом второго счетчика, а адресные входы - с соответствующими выходами второго счетчика, вход аналого-цифрового преобразователя через мультиплексор соединен с входами устройства, С-вход - с выходом преобразователя напряжение - частота, вход которого соединен с входом управления устройства, и С-входом первого счетчика, а вход начальной установки - с первым выходом (Л первого дешифратора, входы которого соединены с соответствующими выходами перво.го счетчика, R -входы счетчиков соединены с входом начальной - установки устройства, входы управления мультиплексора и входы второго дешифратора соединены с 00 ГС соответствующими выходами второго счетчика, 5-и f -входы PS-триггера р соединены соответственно с вторым ;И третьим выходами первого дешифратора, а выход - с первым входом элемента 2 ШШ, второй вход которого соединен с четвертым выходом первого дешифратора, выходы второго дешифратора соединены соответственно с первыми входами п элементов 2 И, вторые входы которых соединены с пятым выходом первого дешифратора.

| Дискретно-аналоговое устройство задержки | 1979 |

|

SU879758A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Дискретно-аналоговая линия задержки | 1980 |

|

SU930583A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-09-30—Публикация

1983-04-07—Подача