Изобретение относится к вычислиельной технике и может быть испольовано в многоканальных телеметричесих системах и системах автоматичесого контроля для управления многоанальной измерительной системой.

Целью изобретения является повыение быстродействия.

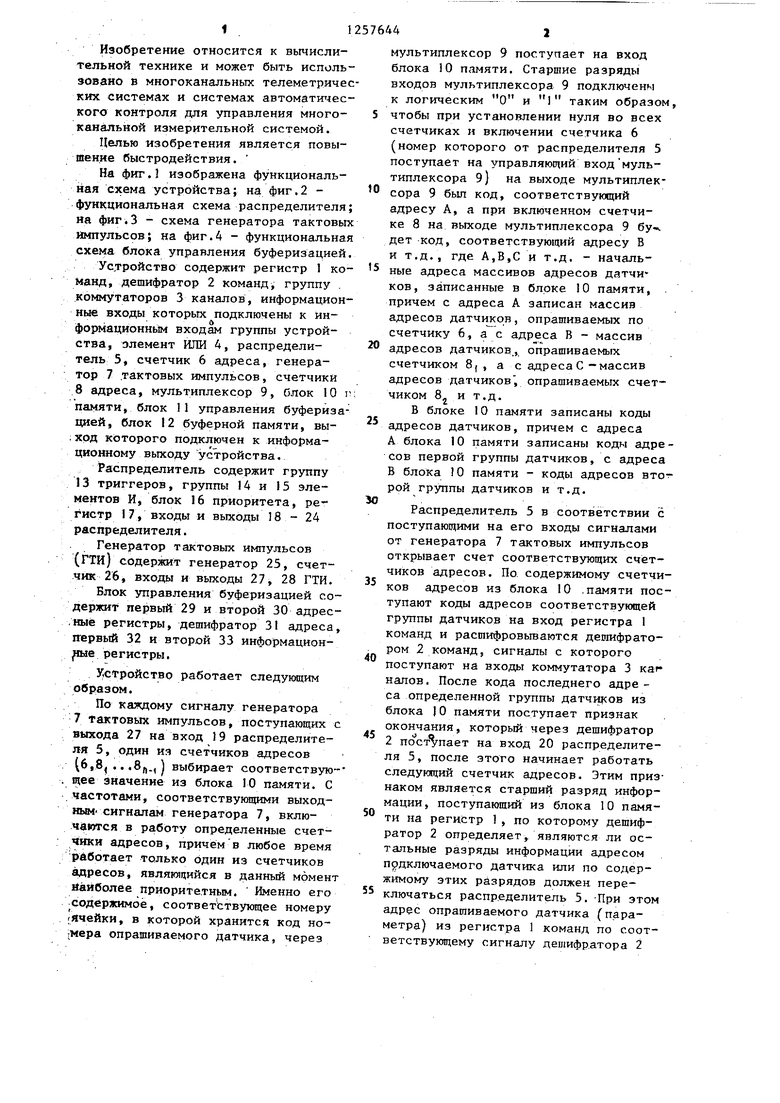

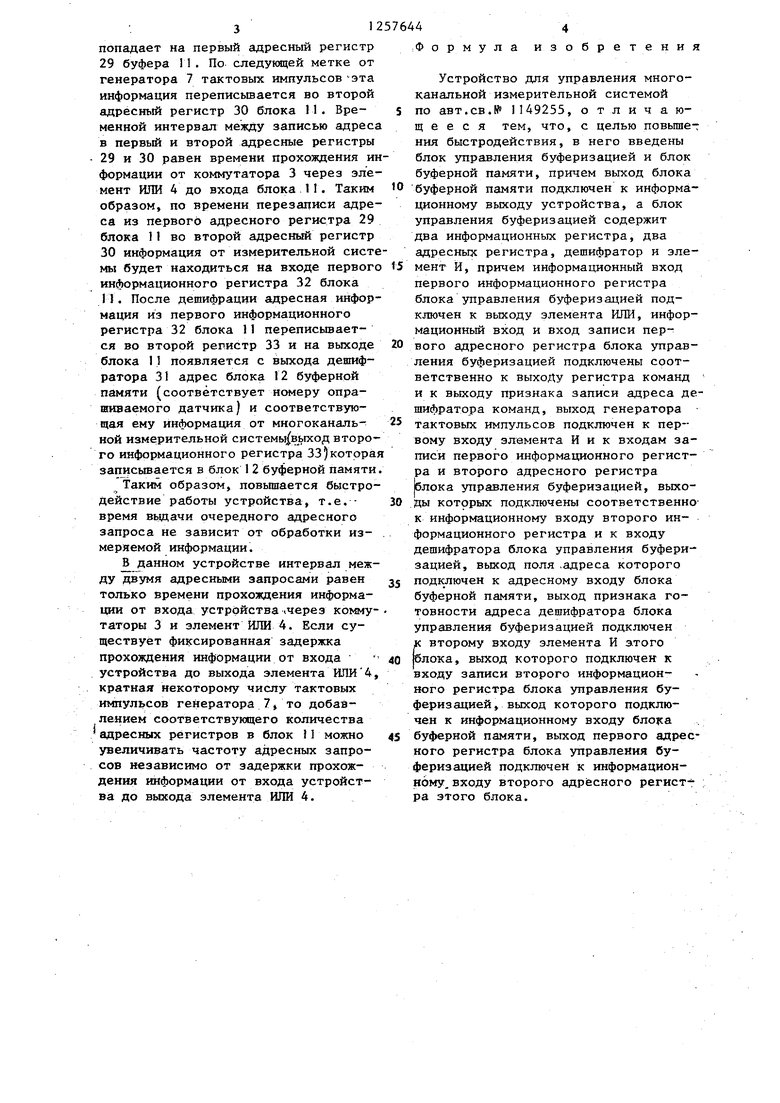

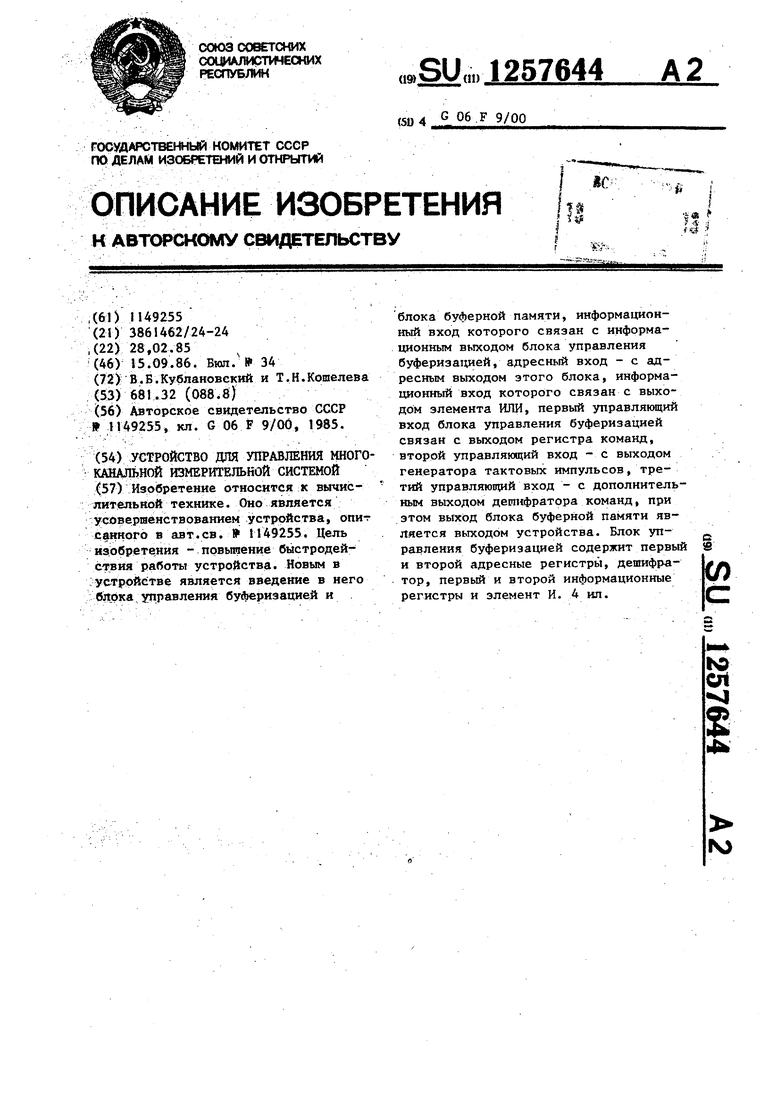

На фиг.1 изображена функциональая схема устройства; на фиг.2 - ункциональная схема распределителя; на фиг.З - схема генератора тактовых Импульсов; на фиг.4 - функциональная схема блока управления буферизацией.

Ус,тройство содержит регистр 1 команд, дешифратор 2 команд, группу . коммутаторов 3 каналов, информационные входы которых подключены к ин- формационнь1м входам группы устройства, элемент ИЛИ 4, распределитель 5, счетчик 6 адреса, генератор 7 .тактовых импульсов, счетчики 8 адреса, мультиплексор 9, блок 10 г; памяти, блок 11 управления буферизацией, блок 12 буферной памяти, вы- хрд которого подключен к информационному выходу устройства.

Распределитель содержит группу 13 триггеров, группы 14 и 15 элементов И, блок 16 приоритета, ре-- гистр 17, входы и выходы 18 - 24 распределителя.

Генератор тактовых импульсов (ГТИ) содержит генератор 25, счет- .чик 26, входы и выходы 27, 28 ГТИ.

Блок управления буферизацией содержит первый 29 и второй 30 адрес- ныё регистры, дешифратор 31 адреса, п ервый 32 и второй 33 информацион- ше регистры.

Устройство работает следующим образом.

По каждому сигналу генератора 7 тактовых импульсов, поступающих с выхода 27 на вход 19 распределителя 5, один из счетчиков адресов (6,8,1 ,. ,8., I выбирает соответствую- щее значение из блока 10 памяти. С частотами, соответствующими выходным сигналам генератора 7, включаются в работу определенные счетчики адресов, причём в любое время ;работает только один из счетчиков адресов, являгацийся в данный момент Наиболее приоритетным. Именно его содержимое, соответствующее номеру (Ячейки, в которой хранится код но- vMepa опрашиваемого датчика, через

S

5

мультиплексор 9 поступает на вход блока 10 памяти. Старшие разряды входов мультиплексора 9 подключены к логическим О и 1 таким образом, чтобы при установлении нуля во всех счетчиках и включении счетчика 6 (номер которого от распределителя 5 поступает на управляющий вход мультиплексора 9} на выходе мультиплексора 9 был код, соответствующий адресу А, а при включенном счетчике 8 на выходе мультиплексора 9 бу- дет код, соответствующий адресу В и т.д., где А,В,С и т.д. - начальные адреса массивов адресов датчи ков, записанные в блоке 10 памяти, причем с адреса А записан массив адресов датчиков, опрашиваемых по счетчику 6, а с адреса В - массив 0 адресов датчиков.,, опрашиваемых счетчиком 8( , ас адреса С -массив адресов датчиков , опрашиваемых счетчиком 8j и т.д.

В блоке IО памяти записаны коды адресов датчиков, причем с адреса А блока 10 памяти записаны коды адресов первой группы датчиков, с адреса В блока }0 памяти - коды адресов вто- рой группы датчиков и т.д.

Распределитель 5 в соответствии с поступающими на его входы сигналами от генератора 7 тактовых импульсов открывает счет соответствующих счётчиков адресов. По. содержимому счетчиков адресов из блока 10 .памяти поступают коды адресов соответствующей группы датчиков на вход регистра 1 команд и расщифровьгоаются дешифратором 2 команд, сигналы с которого поступают на входы коммутатора 3 каг налов. После кода последнего адреса определенной группы датчиков из блока 10 памяти поступает признак окончания, который через дешифратор 2 псэст пает на вход 20 распределителя 5, после зтого начинает работать следующий счетчик адресов. Этим признаком является старший разряд информации, поступающий из блока 10 памяти на регистр 1, по которому дешифратор 2 определяет, являются ли остальные разряды информации адресом подключаемого датчика или по содержимому этих разрядов должен пере- ключаться распр.еделитель 5, -При этом адрес опрашиваемого датчика (параметра) из регистра 1 команд по соответствующему сигналу деишфр.атора 2

0

5

0

0

попадает на первый адресный регистр 29 буфера 11. По следующей метке от генератора 7 тактовых импульсов эта информация переписьюается во второй адресный регистр 30 блока 11. Временной интервал между записью адреса в первый и второй адресные регистры

29и 30 равен времени прохождения информации от коммутатора 3 через элемент ИЛИ 4 до входа блока . 11. Таким образом, по времени перезаписи адреса из первого адресного регистра 29 блока 11 во второй адресный регистр

30информация от измерительной системы будет находиться на входе первого 15 мент И, причем информационный вход

информационного регистра 32 блока 11. После дешифрации адресная информация из первого информационного регистра 32 блока 11 переписывается во второй регистр 33 и на выходе блока 11 появляется с выхода дешифратора 31 адрес блока 12 буферной памяти (соответствует номеру опрашиваемого датчика) и соответствующая ему информация от многоканальной измерительной системь вьгход второго информационного регистра 33)котрра записывается в блок 1 2 буферной памяти Таким образом, повышается быстродействие работы устройства, т.е. время вьадачи очередного адресного запроса не зависит от обработки измеряемой информации.

В данном устройстве интервал между двумя адресными запросами равен только времени прохождения информации от входа устройства «через коммутаторы 3 и элемент ИЛИ 4. Если существует фиксированная задержка прохождения информации от входа устройства до выхода элемента ИЛИ 4, кратная некоторому числу тактовых шотульсов генератора 7, то добавлением соответствующего количества адресных регистров в блок II можно увеличивать частоту адресных запросов независимо от задержки прохождения информации от входа устройства до выхода элемента ИЛИ 4.

а

1257644

,Ф о

рмула изобретения

Устройство для управления многоканальной измерительной системой по авт.св.№ 1149255, отличающееся тем, что, с целью повьппет ния быстродействия, в него введены блок управления буферизацией и блок буферной памяти, причем вьпсод блока буферной памяти подключен к информационному выходу устройства, а блок управления буферизацией содержит два информационных регистра, два адресных регистра, дешифратор и элепервого информационного регистра блока управления буферизацией подключен к выходу элемента ИЛИ, информационный вход и вход записи первого адресного регистра блока управления буферизацией подключены соответственно к выходу регистра команд и к выходу признака записи адреса дешифратора команд, выход генератора тактовых импульсов подключен к первому входу элемента И и к входам записи первого информационного регистра и второго адресного регистра блока управления буферизацией, выходы которых подключены соответственно

к информационному входу второго информационного регистра и к входу дешифратора блока управления буферизацией, выход поля .адреса которого подк лючен к адресному входу блока буферной памяти, выход признака готовности адреса дешифратора блока управления буферизацией подключен к второму входу элемента И этого рлока, выход которого подключен к входу записи второго информационного регистра блока управления буферизацией, выход которого подключен к информационному входу блора буферной памяти, выход первого адресного регистра блока управления буферизацией подключен к информационному входу второго адресного регист- : ра этого блока.

21 22 2219

On 6/1.2 1)п&1.7 От 5п.7 Фиг.2

n

ОтМ Опб1.7

Составитель М.Силин Редактор Э.Слиган Техред Л.Сердюкова Корректор С.Черни

Заказ 4958/48 Тираж 671 . Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производствеино-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

7П

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления многоканальной измерительной системой | 1983 |

|

SU1149255A1 |

| Устройство для телеконтроля | 1990 |

|

SU1732366A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Устройство для индикации | 1985 |

|

SU1261005A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для сопряжения электронной вычислительной машины с каналами связи | 1983 |

|

SU1117627A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

Изобретение относится к вычис- лятельной технике. Оно является усовершенствованием устройства, опит сатого в авт.св. 1149255. Цель изобретения - повышение быстродействия работы устройства. Новым в ;устройстве является введение в него управления буферизацией и блока буферной памяти, информационный вход которого связан с информационным выходом блока управления буферизацией, адресный вход - с адресным выходом этого блока, информационный вход которого связан с выходом элемента ИЛИ, первый управляющий вход блока управления буферизацией связан с выходом регистра команд, второй управляющий вход - с выходом генератора тактовых импульсов, третий управляющий вход - с дополнительным выходом дешифратора команд, при этом выход блока буферной памяти является выходом устройства. Блок управления буферизацией содержит первый и второй адресные регистры, дешифратор, первый и второй информационные регистры и элемент И. 4 ил.

| Устройство для управления многоканальной измерительной системой | 1983 |

|

SU1149255A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-15—Публикация

1985-02-28—Подача