: ... . -

Изобретение относится к вычислительной технике и может быть исполь- эованр при построении управляющих автоматов.

Цепью изобретения является сокра- й(е1ше оборудования.

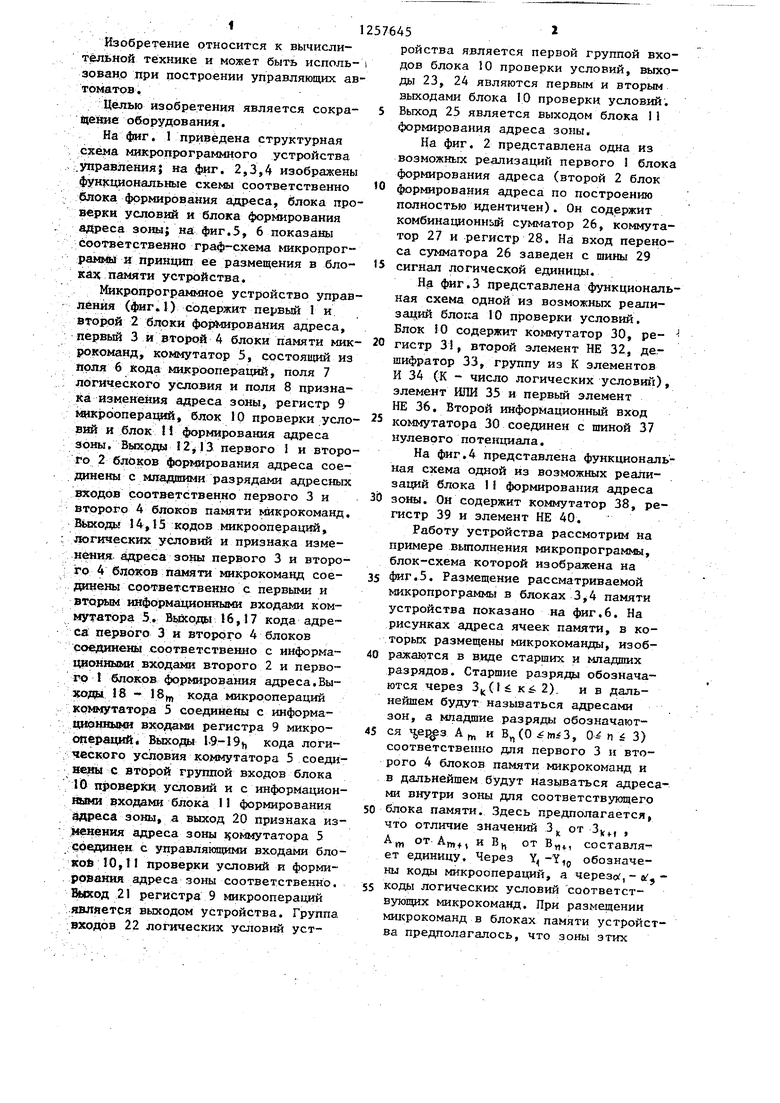

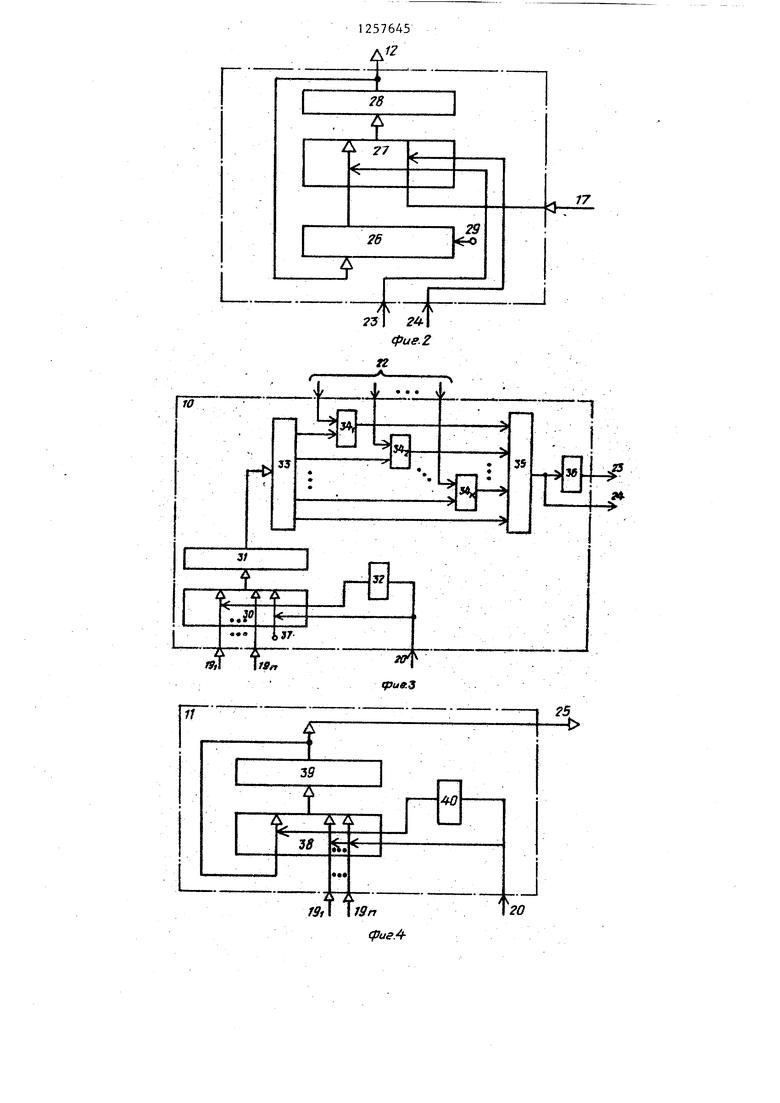

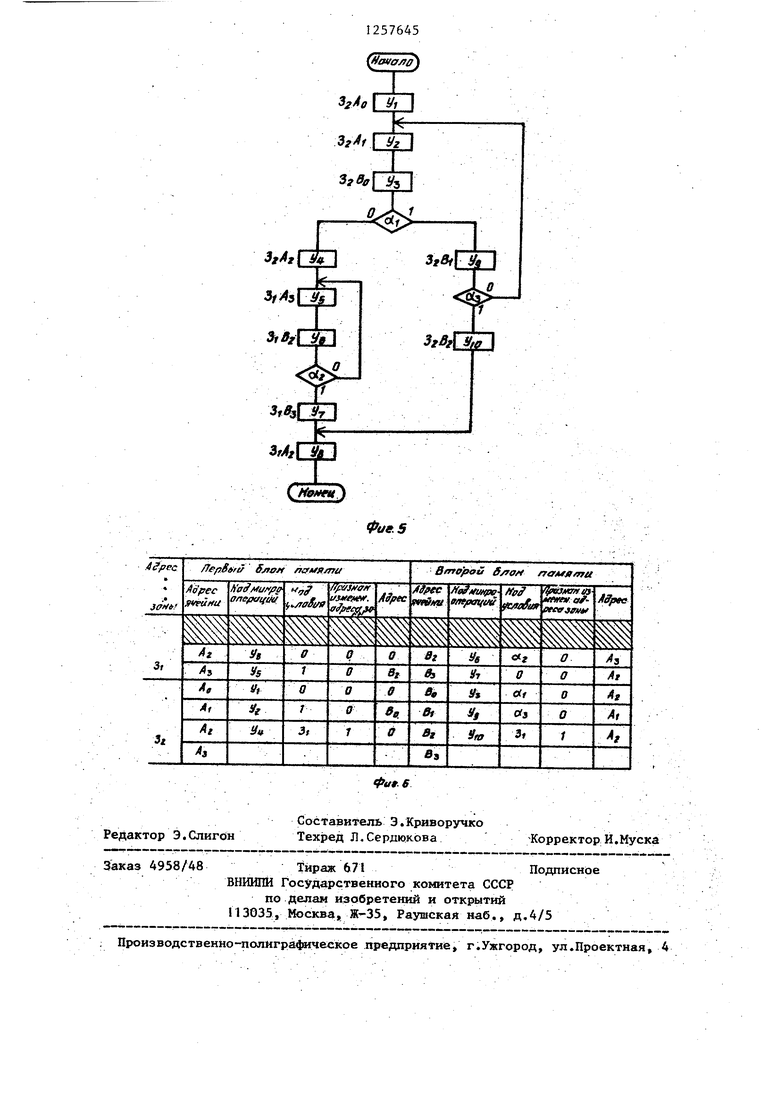

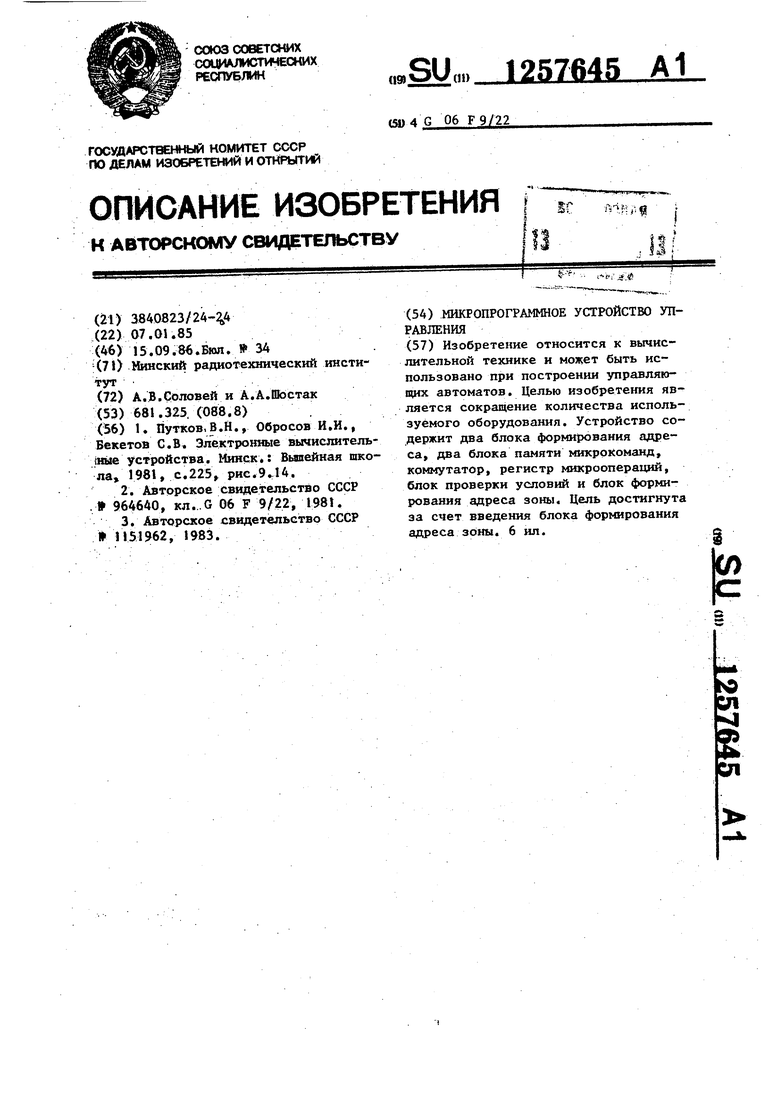

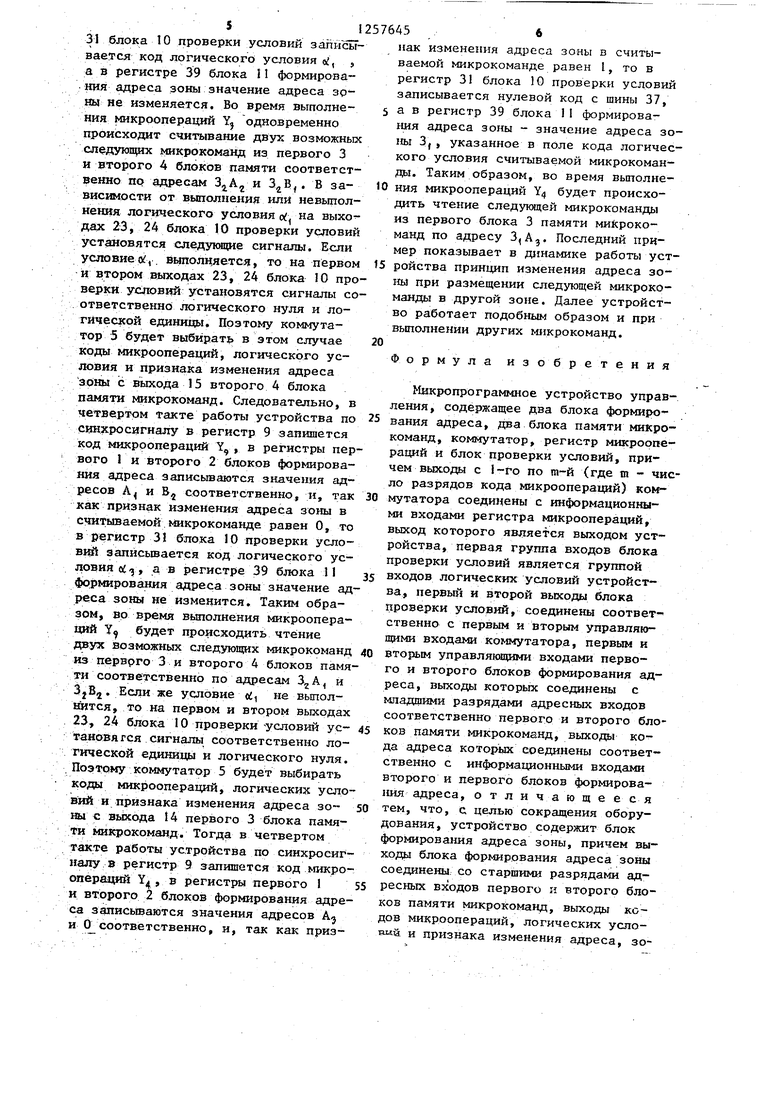

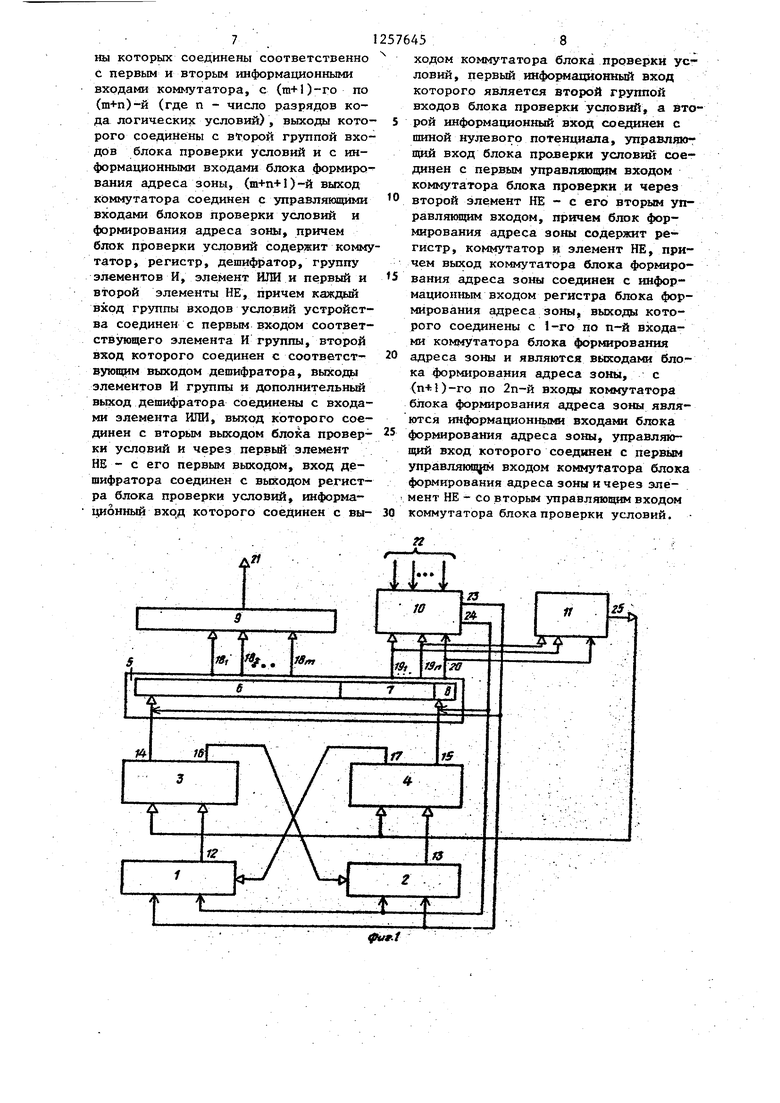

На фиг. 1 приведена структурная схема микропрограммного устройства .управления} на фиг. 2,3,4 изображены фун сциональные схемы соответственно блока формирования адреса, блока проверки условий и блока формирования адреса зоны; на фиг.5, 6 показаны соответственно граф-схема микропрог- рамми и принцип ее размещения в блоках памяти устройства.

6 кpQпpoгpaммнoe устройство управления (фиг.1) содержит первый 1 и второй 2 близки формирования адреса, первый 3 и эторой 4 блоки памяти микрокоманд, коммутатор 5, состоящий из поля 6 кода микроопераций, поля 7 логического условия и поля 8 признака изменения адреса зоны, регистр 9 микроопераций, блок 10 проверки условий и блокП формирования адреса Зоны, Выхода I2jl3 первого 1 и второго 2 блоков Армирования адреса соединены с младшими разрядами адресных входов соответственно первого 3 и второго 4 блоков памяти микрокоманд. Выходы 14,15 кодов микроопераций, логических условий и признака изменения адреса зоны первого 3 и второ- ipo 4 блоков памяти микрокоманд соединены соответственно с первыми и вторым информационными входами коммутатора 5. 16,17 кода адреса первого 3 и BTopcJTo 4 блоков соединены соответственно с информационными входами второго 2 и первого 1 блоков формирования адреса,Выхода 18 - 1В ff, кода микроопераций ко1 1Утатора 5 соединены с информационными входам регистра 9 микро- мперацнй Выходы 1-9-19, кода логического условия коммутатора 5 соеди- неш с второй труппой входов блока 10 проверки условий и с информационными эходами блока I1 формирования ддреса зоны, а выход 20 признака из- ;мененкя адреса зоны 1{оммутатора 5 соединен с управлякицими входами бло- коб 10,11 проверки условий и формирования адреса зоны соответственно. сод 21 регистра 9 микроопераций является выходом устройства. Группа входов 22 логических условий уст57645

ройства является первой группой вхо- дов блока 10 проверки условий, mjxo- ды 23, 24 являются первым и вторым выходами блока 10 проверки условий. 5 Выход 25 является выходом блока 11 формирования адреса зоны.

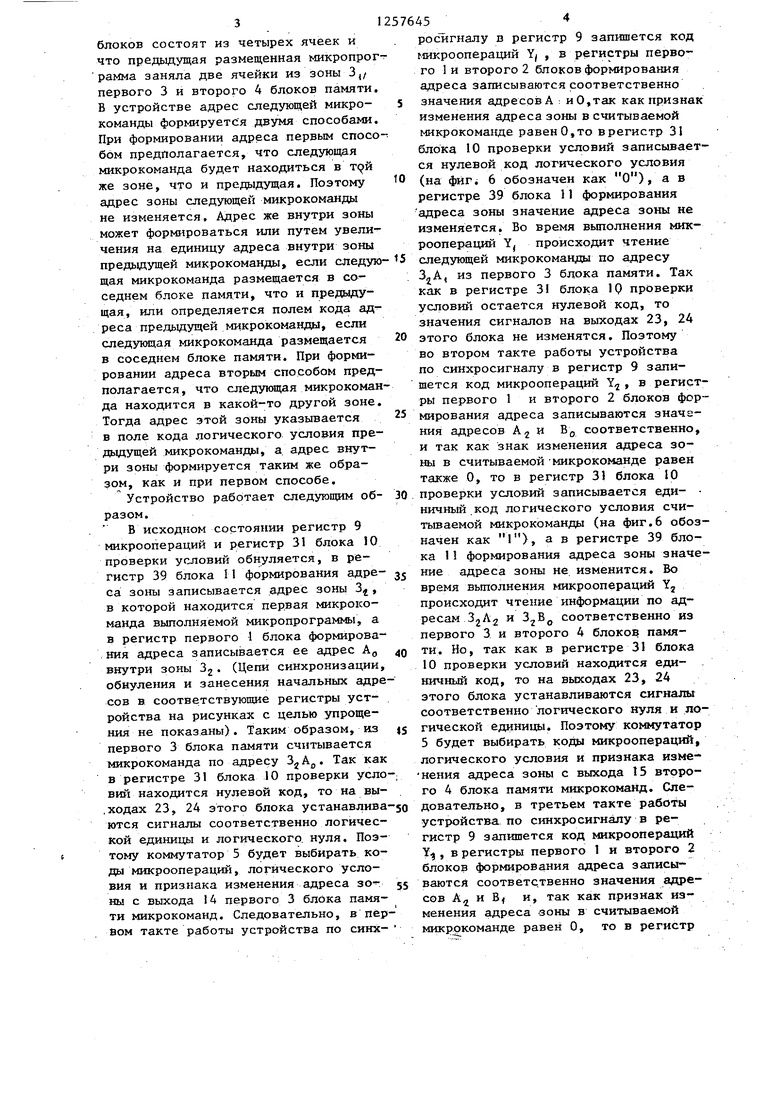

На фиг, 2 представлена одна из возможных реализаций первого блока формирования адреса (второй 2 блок О формирования адреса по построению полностью идентичен). Он содержит комбинационный сумматор 26, коммутатор 27 и регистр 28. На вход переноса сумматора 26 заведен с шины 29 5 сигнал логической единицы.

Нд фиг.З представлена функциональная схема одной из возможных реализаций блока 10 проверки условий. Блок 10 содержит коммутатор 30, ре-

20 гистр 31, второй элемент НЕ 32, дешифратор 33, группу из К злементов И 34 (К - число логических условий), злемент ИЛИ 35 и первый элемент НЕ 36. Второй информационный вход

25 коммутатора 30 соединен с шиной 37

нулевого потенциала.

На фиг.4 представлена функциональная схема одной из возможных реализаций блока II формирования адреса

ЗЬ зоны. Он содержит коммутатор 38, регистр 39 и элемент НЕ 40.

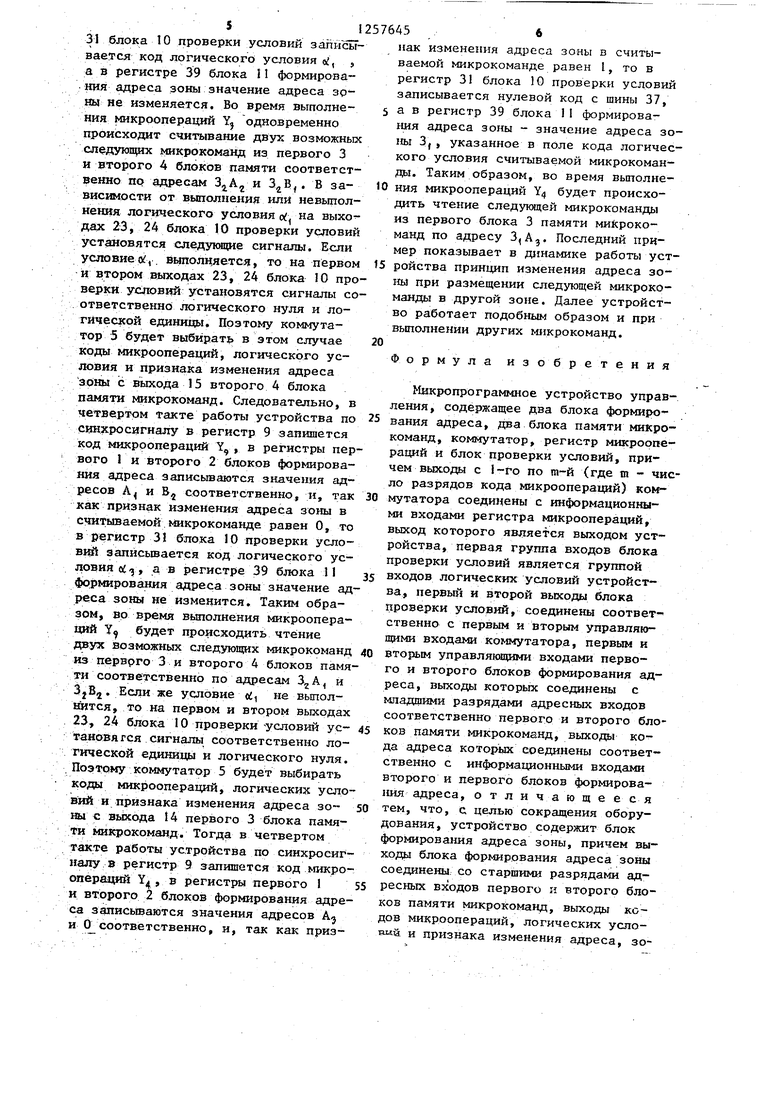

Работу устройства рассмотрим на примере вьшолнения микропрограммы, блок-схема которой изображена на

35 фиг.5. Размещение рассматриваемой микропрограммы в блоках 3,4 памяти устройства показано на фиг.6. На рисунках адреса ячеек памяти, в которых размещены микрокоманды, изоб40 ражаются в в,иде старших и мпадших разрядов. Старшие разряды обозначаются через 3(). и в дальнейшем будут называться адресами зон, а младшие разряды обозначают45 ся 4, А f« и В„ (О , 0 п i 3) соответственно для первого 3 и второго 4 блоков памяти микрокоманд и в дальнейшем будут называться адресами внутри зоны для соответствующего

50 блока памяти. Здесь предполагается, что отличие значений 3 от 3, , А от АПТ, и В от В„, составля- ет единицу. Через Y -Y,(, обозначены коды микроопераций, а через(Х, - o j

55 кодь логических условий соответствующих микрокоманд. При размещении микрокоманд в блоках памяти устройства предполагалось, что зоны зтих

блоков состоят из четырех ячеек и что предьщущая размещенная микропрог рамма заняла две ячейки из зоны 3,/ первого 3 и второго 4 блоков памяти. В устройстве адрес следующей микро- команды формируется двумя способами. При формировании адреса первым способом предполагается, что следующая микрокоманда будет находиться в Т9й же зоне, что и предыдущая. Поэтому адрес зоны следующей микрокоманды не изменяется. Адрес же внутри зоны может формироваться или путем увели- чения на единицу адреса внутри зоны предыдущей микрокоманды, если следую щая микрокоманда размещается в соседнем блоке памяти, что и предыдущая, или определяется полем кода адреса предьздущей микрокоманды, если следующая микрокоманда размещается в соседнем блоке памяти. При формировании адреса вторым способом предполагается, что следуияцая микрокоманда находится в какой-то другой зоне. Тогда адрес этой зоны указывается в поле кода логического условия пре- дьщущей микрокоманды, а. адрес внутри зоны формируется таким же образом, как и при первом способе.

Устройство работает следующим об- разом.

В исходном состоянии регистр 9 микроопераций и регистр 31 блока 10 проверки условий обнуляется, в регистр 39 блока II формирования адре- са зоны записывается адрес зоны 3, в которой находится первая микрокоманда выполняемой микропрограммы, а в регистр первого 1 блока формирова. ния адреса записывается ее адрес А,, внутри зоны 32. (Цепи синхронизации, обнуления и занесения начальных адресов в соответствующие регистры устройства на рисунках с целью упрощения не показаны). Таким образом, из первого 3 блока памяти считывается микрокоманда по адресу 3 А. Так как в регистре 31 блока 10 проверки уело ВИЙ находится нулевой код, то на вы,ходах 23, 24 этого блока устанавлива ются сигналы соответственно логической единицы и логического, нуля. Поэтому коммутатор 5 будет выбирать коды микроопераций, логического условия и признака изменения адреса зог ны с выхода 14 первого 3 блока памяти микрокоманд. Следовательно, в Пёр Вом такте работы устройства по синх-

росигналу в регистр 9 запишется код микроопераций Y( , в регистры первого 1 и второго 2 блоков формирования адреса записываются соответственно значения адресов А ; и О,так как призна изменения адреса зоны в считываемой мнкрокома1ще равен О,то в регистр 31 блока 10 проверки условий записывается нулевой код логического условия (на фйг 6 обозначен как О), а в регистре 39 блока 11 формирования адреса зоны значение адреса зоны не изменяется. Во время выполнения микроопераций YJ происходит чтение следующей микрокоманды по адресу , из первого 3 блока памяти. Так как в регистре 31 блока 1Q проверки условий остается нулевой код, то значения сигналов на выходах 23, 24 этого блока не изменятся. Поэтому во втором такте работы устройства по синхросигналу в регистр 9 запишется код микроопераций Y; , в регистры первого 1 и второго 2 блоков формирования адреса записываются значения адресов Aj и В соответственно, и так как знак изменения адреса зоны в считываемой микрокоманде равен также О, то в регистр 31 блока 10 проверки условий записывается еди- ничный.код логического условия счи- тьшаемой микрокоманды (на фиг.6 обозначен как 1), а в регистре 39 блока 11 формирования адреса зоны значение адреса зоны не изменится. Во время выполнения микроопераций Yj происходит чтение информа.ции по адресам 32 А g и соответственно из первого 3 и второго 4 блоков памяти. Но, так как в регистре 31 блока 10 проверки условий находится единичный код, то на выходах 23, 24 этого блока устанавливаются сигналы соответственно логического нуля и логической еднницы. Поэтому коммутатор 5 будет выбирать коды микроопераций, логического условия и признака изме- нения адреса зоны с выхода 15 второго 4 блока памяти микрокоманд. Следовательно, в третьем такте работы устройства по синхросигналу в регистр 9 запишется код микроопераций Y, в регистры первого 1 и второго 2 блоков формирования адреса записываются соответственно значения адресов А и В| и, так как признак изменения адреса -зоны в считываемой микрркома.нде равен О, то в регистр

51

31 блока 10 проверки условий записывается код логического условия oi, , а в регистре 39 блока I1 формирования адреса зоны значение адреса зр- ны не изменяется. Во время выполнения микроопераций Yj одновременно происходит считывание двух возможных следующих микрокоманд из первого 3 и второго 4 блоков памяти соответст

венно по адресам и ,. В за- 10 ния микроопераций 4 будет происходить чтение следукядей микрокоманды из первого блока 3 памяти миЛроко- манд по адресу . Последний пример показывает в динамике работы уст- условие :,. выполняется, то на первом 15 ройства принцип изменения адреса зо- и втором в« псодах 23, 24 блока 10 про- ны при размещении следующей микроко- верки условий установятся сигналы со- манды в другой зоне. Далее устройствисимости от выполнения или невыполнения логического условия oi на выходах 23, 24 блока 10 проверки условий установятся следующие сигналы. Если

ответственнб логического нуля и логической единицы. Поэтому коммутатор 5 будет выбирать в этом случае коды микроопераций, логического условия и признака изменения адреса зоны с выхода 15 второго 4 блока памяти микрокоманд. Следовательно, в

20

во работает подобным образом и при выполнении других микрокоманд.

Формула изобретения

ва, первый и второй выходы блока проверки условий, соединены соответственно с первым и вторым управляющими входами коммутатора, первым и

Микропрограммное устройство управления, содержащее два блока формиро- четвертом такте работы устройства по 5 вания адреса, два блока памяти микро- синхросигналу в регистр 9 запишется команд, коммутатор, регистр микроопе- код микроопераций Y,, в регистры пер- раций и блок проверки условий, при- вого 1 и второго 2 блоков формирова- чем выходы с 1-го по т-й (где tn - чис- ния адреса записьшаются значения ад- ло разрядов кода микроопераций) ком- ресов А и В соответственно, и, так 30 мутатора соединены с информационны- как признак изменения адреса зоны в ми входами регистра микроопераций, считываемой микрокоманде равен О, то выход которого является выходом уст- в регистр 3 блока 10 проверки уело- ройства, первая группа входов блока вщ1 запйсьшаетея код логического ус- проверки условий является группой ловияо с|, а в регистре 39 блока 11 35 входов логических условий устройст- формирования адреса зоны значение адреса зоны не изменится. Таким образом, во время выполнения микроопераций У будет происходить чтение ffByx возможных следую1цих микрокоманд 40 вторым управляющими входами перво- из перврго 3 и второго 4 блоков памя- го и второго блоков формирования ад- ти соответственно по адресам и реса, выходы которых соединены с 3jBj,. Если же условие cdi не выпол- младшими разрядами адресных входов нйтся. То на первом и втором выходах соответственно первого и второго бло- 23, 24 блока 10 проверки условий ус- 45 ков памяти микрокоманд, выходаг ко- танрвягея сигналы соответственно ло- да адреса которых соединены соответ- гической единицы и логического нуля. Поэтому коммутатор 5 будет выбирать коды микроопераций, логических уаю- вий и признака изменения адреса зо- 50 ша с вькода 14 первого 3 блока памяти микрокоманд. Тогда в четвертом тахте работы устройства по синхросиг - налу в регистр 9 запишется код микрорпер&ций Y, в регистры первого 1 55 ресных входов первого и второго бло- и второгр 2 блоков формирования адре- ков памяти микрокоманд, вьпсоды коса записьшаются значения адресов Aj и О соответственно, и, так как призственно с информащ1онными входами второго и первого блоков формирова- 1ШЯ адреса, отличающееся тем, что, с целью сокращения оборудования, устройство содержит блок формирования адреса зоны, причем выходы блока формирования адреса зоны соединены/Со старшими разрядами аддов микроопераций, логических усло- i«iu и признака изменения адреса, зоиак изменения адреса зоны в считываемой микрокоманде равен I, то в регистр 31 блока 10 проверки условий записывается нулевой код с шины 37, зав регистр 39 блока 1I формирования адреса зоны - значение адреса зоны 3f, указанное в пОле кода логического условия считываемой микрокоманды. Таким образом, во время выполне20

во работает подобным образом и при выполнении других микрокоманд.

Формула изобретения

ва, первый и второй выходы блока проверки условий, соединены соответственно с первым и вторым управляющими входами коммутатора, первым и

Микропрограммное устройство управления, содержащее два блока формиро- вания адреса, два блока памяти микро- команд, коммутатор, регистр микроопе- раций и блок проверки условий, при- чем выходы с 1-го по т-й (где tn - чис ло разрядов кода микроопераций) ком- мутатора соединены с информационны- ми входами регистра микроопераций, выход которого является выходом уст- ройства, первая группа входов блока проверки условий является группой входов логических условий устройст- вторым управляющими входами перво- го и второго блоков формирования ад- реса, выходы которых соединены с младшими разрядами адресных входов соответственно первого и второго бло- ков памяти микрокоманд, выходаг ко- да адреса которых соединены соответ-

Микропрограммное устройство управления, содержащее два блока формиро- вания адреса, два блока памяти микро- команд, коммутатор, регистр микроопе- раций и блок проверки условий, при- чем выходы с 1-го по т-й (где tn - чис ло разрядов кода микроопераций) ком- мутатора соединены с информационны- ми входами регистра микроопераций, выход которого является выходом уст- ройства, первая группа входов блока проверки условий является группой входов логических условий устройст- вторым управляющими входами перво- го и второго блоков формирования ад- реса, выходы которых соединены с младшими разрядами адресных входов соответственно первого и второго бло- ков памяти микрокоманд, выходаг ко- да адреса которых соединены соответ-

ственно с информащ1онными входами второго и первого блоков формирова- 1ШЯ адреса, отличающееся тем, что, с целью сокращения оборудования, устройство содержит блок формирования адреса зоны, причем выходы блока формирования адреса зоны соединены/Со старшими разрядами адресных входов первого и второго бло- ков памяти микрокоманд, вьпсоды кодов микроопераций, логических усло- i«iu и признака изменения адреса, зо

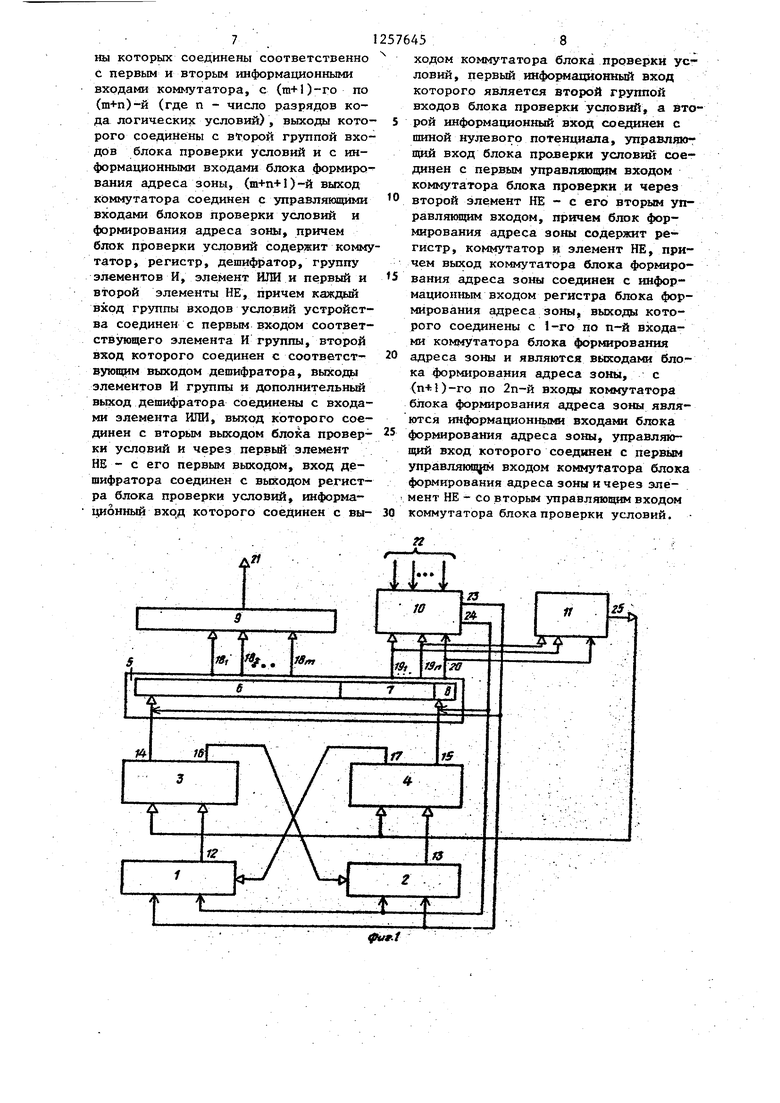

шя которых соединены соответственно с первым и вторым информационными входами коммутатора, с (т+1)-го по (т+п)-й (где п - число разрядов кода логических условий), выходы кото- рого соединены с второй группой входов блока проверки условий и с информационными входами блока формирования адреса зоны, (т+п+1)-й выход коммутатора соединен с управляющими входами блоков проверки условий и формирования адреса зоны, причем блок проверки условий содержит коммутатор, регистр, дешифратор, группу элементов И, элемент ИЛИ и первый и второй элементы НЕ, причем каждый вход группы входов условий устройства соединен с первым входом соответствующего элемента И группы, второй вход которого соединен с соответствующим выходом дешифратора, выхода элементов И группы и дополнительный вьрсод дешифратора соединены с входами элемента ИЛИ, выход которого сое- данен с вторым выходом блока провер- ки условий и через первьй элемент НЕ - с его первым выходом, вход дешифратора соединен с выходом регистра блока проверки условий, информационный вход которого соединен с вы

ходом коммутатора блока проверки ус - ловий, первый информационный вход которого является второй группой входов блока проверки условий, а второй информационный вход соединен с пшной нулевого потенциала, управляю- вщй вход блока проверки условий соединен с первьш управляющим входом коммутатора блока проверки и через второй элемент НЕ - с его вторым управ л яннцим входом, причем блок формирования адреса зоны содержит регистр, кoм fyтaтop и элемент НЕ, причем выход коммутатора блока формирования адреса зоны соединен с информационным входом регистра блока формирования адреса зоны, выходы которого соединены с 1-го по п-й входами коммутатора блока формирования адреса зоны и являются выходами блока формирования адреса зоны, с (п-ь 1) -го по 2п-й входы коммутатора блока формирования адреса зоны являются информационным входами блока формирования адреса зоны, управляющий вход которого соединен с первым управляют входом коммутатора блока формирования адреса зоны и через эле- мент НЕ - со вторым управляюпщм входом коммутатора блока проверки условий.

3r

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1985 |

|

SU1381503A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1629910A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Многопрограммное устройство управления | 1984 |

|

SU1231501A1 |

| Программный управляющий модуль с контролем | 1990 |

|

SU1758634A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Устройство для управления,контроля и диагностирования | 1985 |

|

SU1297063A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении управляющих автоматов. Целью изобретения является сокращение количества используемого оборудования. Устройство содержит два блока формирования адреса, два блока памяти микрокоманд, коммутатор, регистр микрооперацнй, блок проверки условий и блок формирования адреса зоны. Цель достигнута за счет введения блока формирования адреса збны. 6 ил. г

Редактор Э.Слигон

Составитель Э.Криворучко Техред Л, Сердклкова

Заказ 4958/48Тираж 671Подписное

ВНИИГШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

. Производственно-полиграфическое предприятие г.Ужгород, ул.Проектная, 4

Корректор И.Муска

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Путков,В.Н., Сбросов И,И., Бекетов С.В | |||

| Электронные вычислительчные устройства | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Синхронизирующее устройство для аппарата, служащего для передачи изображений на расстояние | 1920 |

|

SU225A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-09-15—Публикация

1985-01-07—Подача