Изобретение относится к вычисли тельной технике и может быть исполь зовано в вычислительных устройствах и системах.

Цель изобретения повьшение бЫ стродействия устройства за счет обеспечения одновременного анализа и условий (п 2),

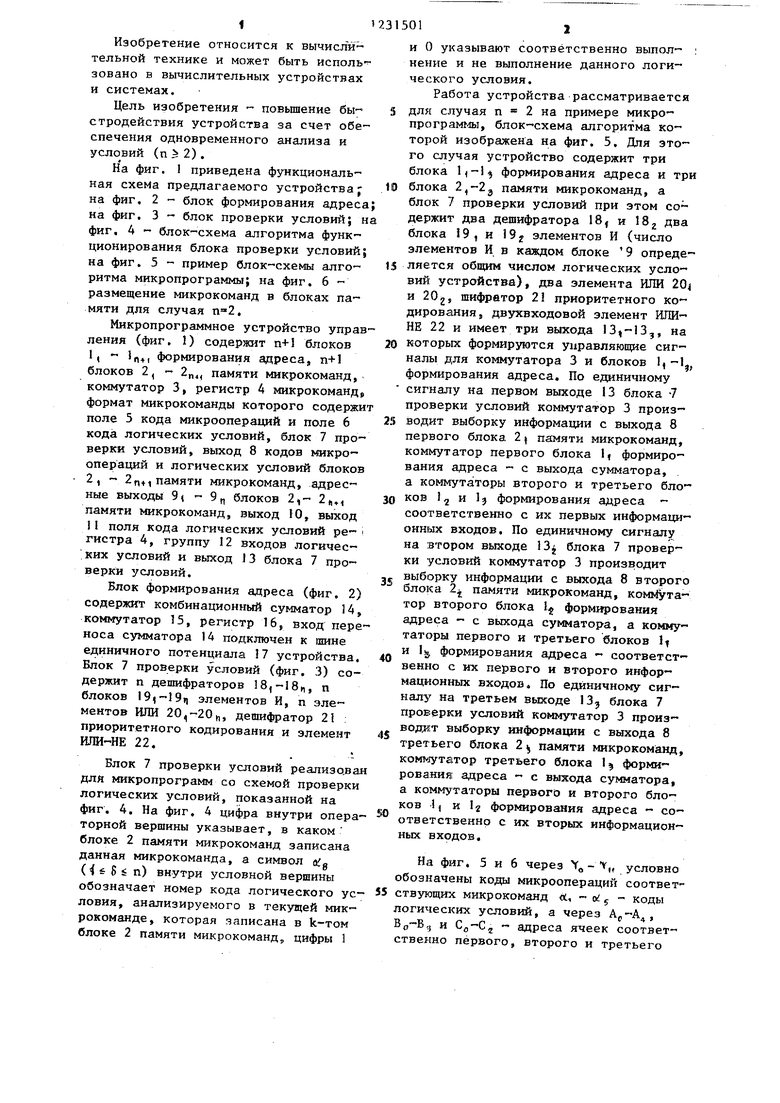

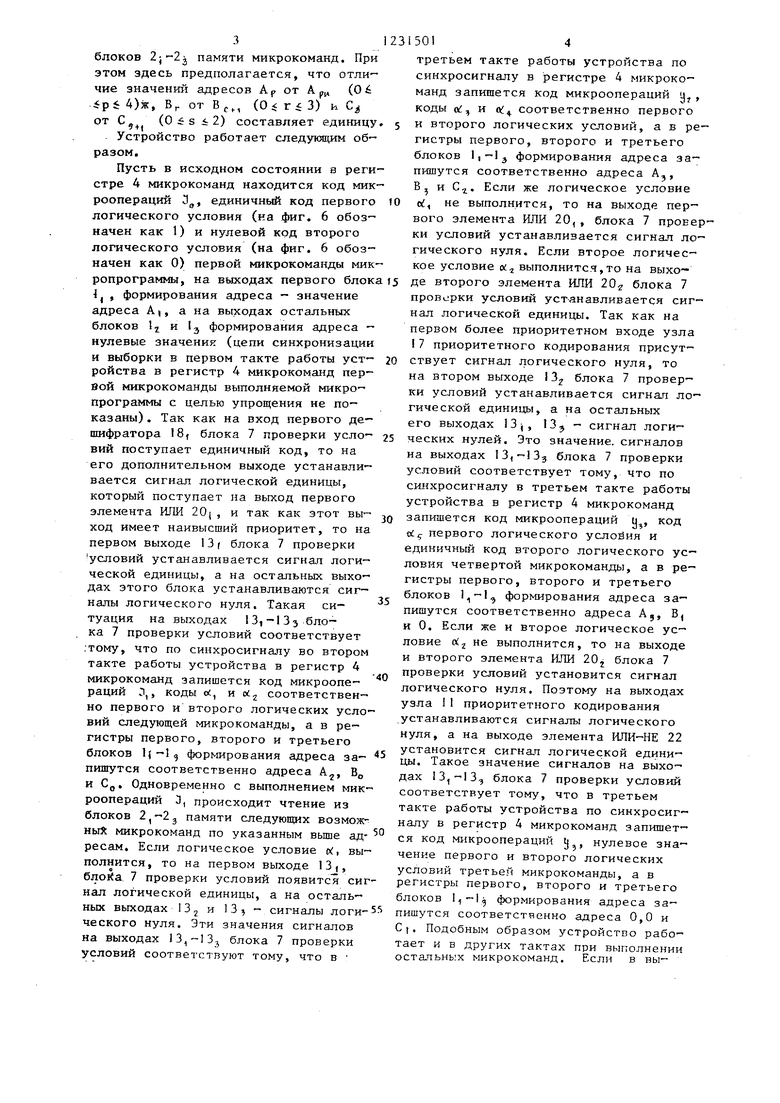

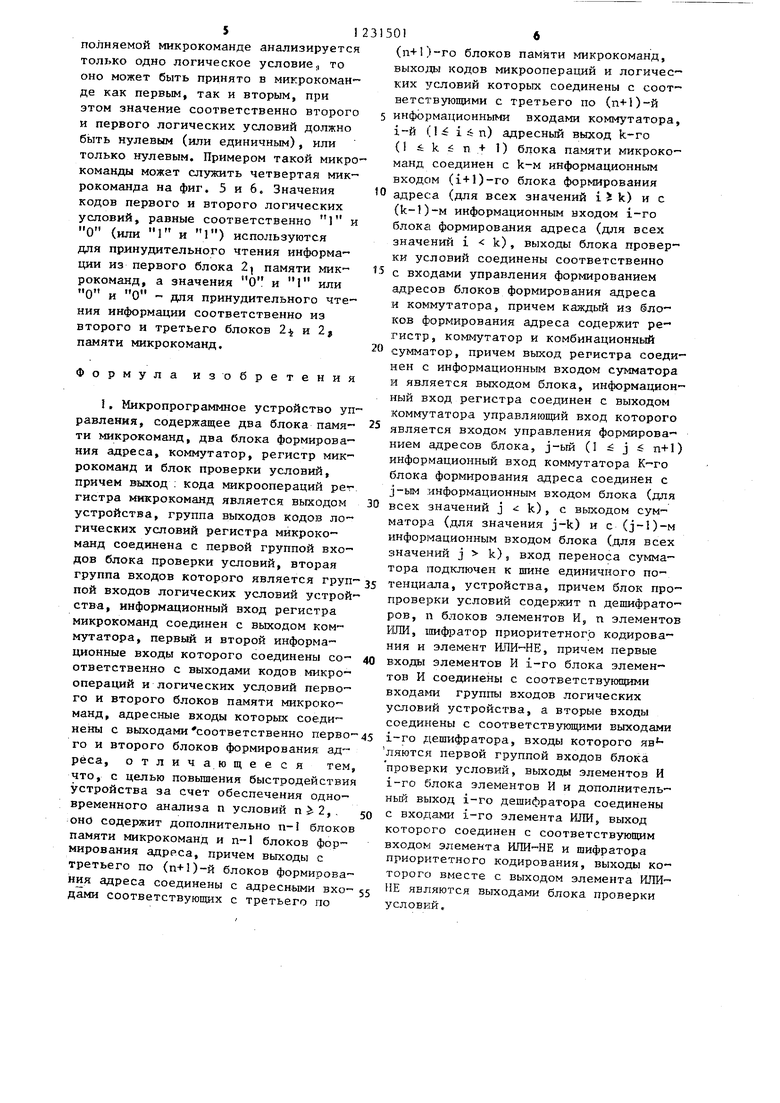

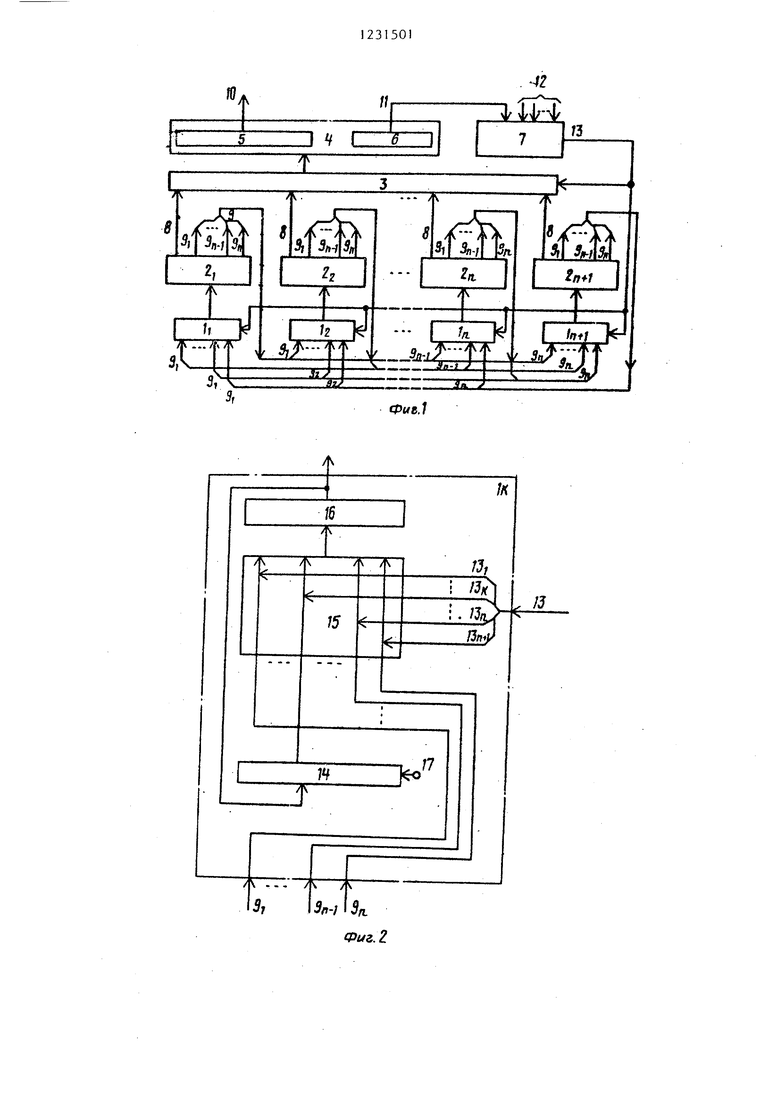

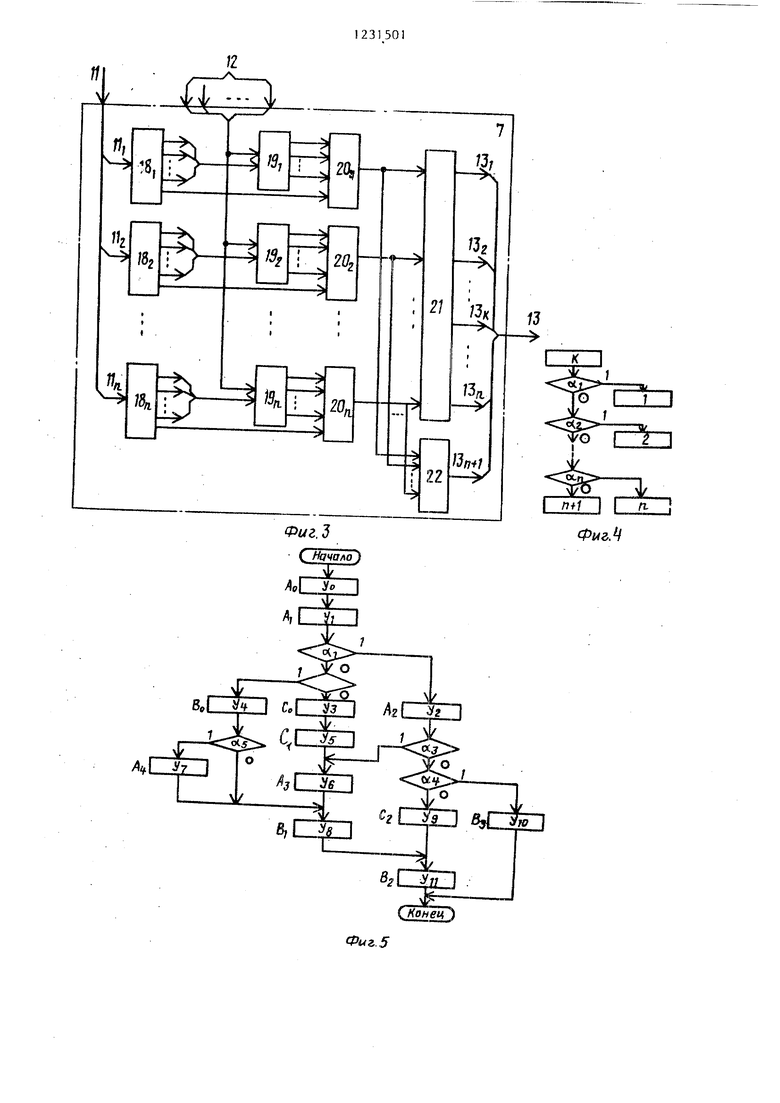

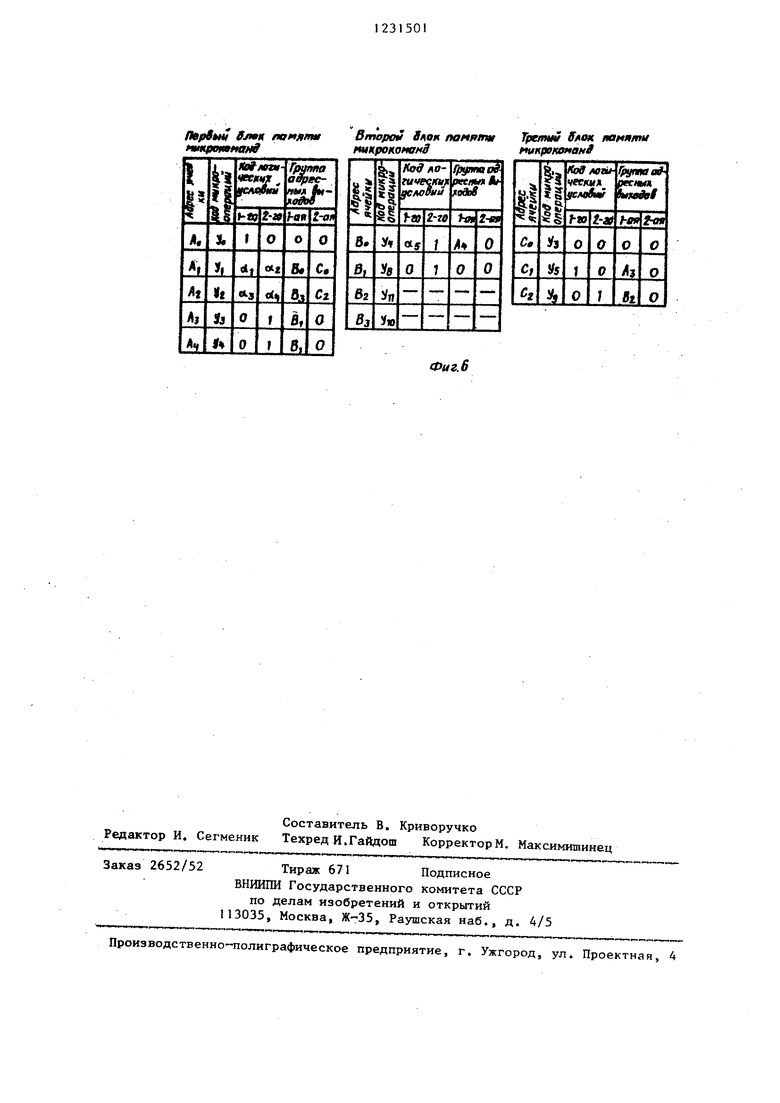

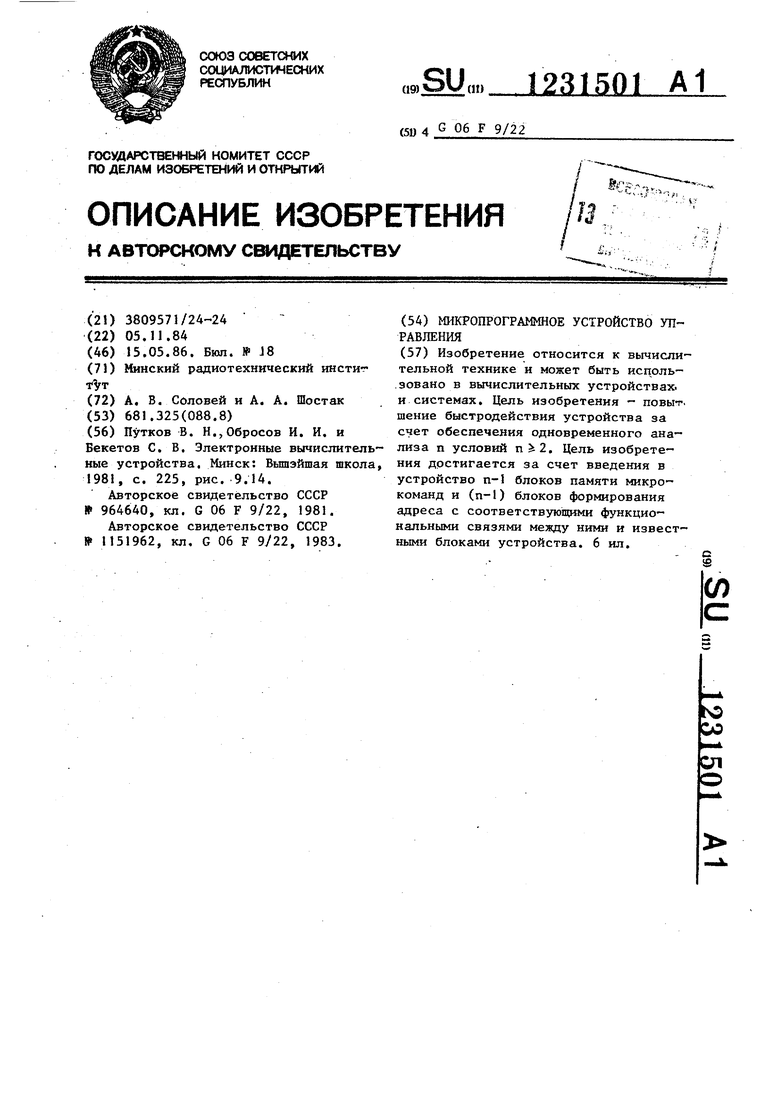

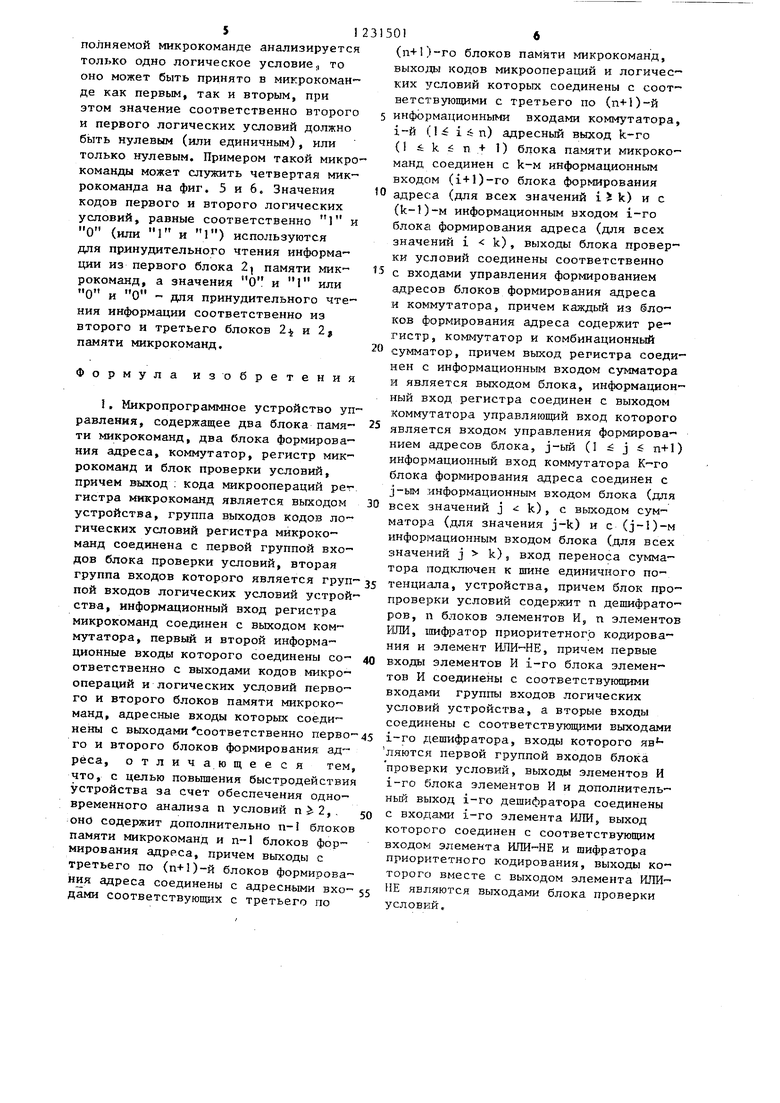

На фиг. 1 приведена функциональная схема предлагаемого устройства ; на фиг. 2 - блок формирования адреса; на фиг. 3 - блок проверки условий; на фиг, 4 - блок-схема алгоритма функционирования блока проверки условий; на фиг. 5 - пример блок-схемы алгоритма микропрограммы; на фиг. 6 - размещение микрокоманд в блоках памяти для случая ,

Микропрограммное устройство управления (фиг. 1) содержит п+1 блоков 1, Ц+, формирования адреса, п+1

блоков

7 ,

2„ памяти микрокоманд.

коммутатор 3, регистр 4 микрокоманд, формат микрокоманды которого содержит поле 5 кода микроопераций и поле 6 кода логических условий, блок 7 проверки условий, выход 8 кодов микроопераций и логических условий блоков 2, - 2f,t, памяти микрокоманд, адресные выходы 9 - 9fl блоков 2,- 2t,ft памяти микрокоманд, выход 10, выход I поля кода логических условий ре- i гистра 4, группу 12 входов логических условий и выход 13 блока 7 проверки условий.

Блок формирования адреса (фиг. 2) содержит комбинационный сумматор 14, коммутатор 15, регистр 16, вход переноса сумматора 14 подключен к шине единичного потенциала 7 устройства. Блок 7 проверки условий (фиг. 3) содержит п дешифраторов 8,-18ч, п блоков элементов И, п элементов ИЛИ 20,-20п, дешифратор 21 приоритетного кодирования и элемент ИЛИ-НЕ 22.

Блок 7 проверки условий реализова для микропрограмм со схемой проверки логических условий, показанной на фиг. 4. На фиг. 4 цифра внутри опера торной вершины указывает, в каком блоке 2 памяти микрокоманд записана данная микрокоманда, а символ ajg (( « В S п) внутри условной вершины

обозначает номер кода логического ус- 5 ствуиэщи: микрокоманд Л,

ловия, анализируемого в текущей микрокоманде, которая записана в k-том блоке 2 памяти микрокоманд„ цифры 1

231501X

и О указывают соответственно выпол- : нение и не выполнение данного логического условия.

Работа устройства рассматривается

5 для случая п 2 на примере микро- програм{ 1Ы, блок-схема алгоритма которой изображена на фиг. 5. Для этого случая устройство содержит три блока 1(- формирования адреса и три

10 блока 2,-2з памяти микрокоманд, а блок 7 проверки условий при этом содержит два дешифратора 18 и 18 два блока 19, и 19f элементов И (число элементов И в каждом блоке 9 опреде13 ляется общим числом логических условий: устройства), два элемента ИЛИ 20| и 202, шифратор 2 приоритетного кодирования, двухвходовой элемент ИЛИ30

НЕ 22 и имеет три выхода ,, на 20 которых формируются управляющие сигналы для коммутатора 3 и блоков Ц -1,, формирования адреса. По единичному сигналу на первом выходе 13 блока -7

проверки условий коммутатор 3 произ- 25 водит выборку информации с выхода 8 первого блока 2) памяти микрокоманд, коммутатор первого блока формирования адреса - с выхода сумматора, а коммутаторы второго и третьего бло

ков Ц и Ц формирования адреса - соответственно с их первых информащ - онных входов. По единичному сигналу на втором выходе 13 блока 7 проверки условий коммутатор 3 производит выборку информации с выхода 8 второго блока .2j памяти микрокоманд, KOMtfyTa- тор второго блока Ц формщ)ования адреса - с выхода сумматора, а коммутаторы первого и третьего блоков It и l, формирования адреса - соответственно с их первого и второго информационных входов. По единичному сигналу на третьем выходе 13 блока 7 условий коммутатор 3 произ- вормт выборку информации с выхода 8 третьего блока 2 памяти микрокоманд, KOMwtyTaTop третьего блока 1 формирования адреса - с выхода сумматора, а коммутаторы первого и второго блоков 1( и 1у формирования адреса - соответственно с их вторых информационных входов.

На фиг. 5 и 6 через X - V,, условно обозначены коды микроопераций соответ 6 коды

логических условий, а через , В о-в,, и Сд-Сг - адреса ячеек соответственно первого, второго и третьего

3

блоков памяти микрокоманд. При этом здесь предполагается, что отличие значений адресов Ар от Арц (Oi .р 4)ж, В г от Bf,, (0 ri 3) h С от С 5 (О S : 2) составляет единицу

Устройство работает следукядим образом.

Пусть в исходном состоянии в регистре 4 микрокоманд находится код микроопераций Jg, единичный код первого логического условия (на фиг. 6 обозначен как 1) и нулевой код второго логического условия (на фиг. 6 обозначен как 0) первой микрокоманды микропрограммы, на выходах первого блок Ij , формирования адреса - значение адреса А|, а на выходах остальнъгх блоков Ij и 1з формирования адреса - нулевые значения (цепи синхронизации и выборки в первом такте работы уст- ройства в регистр 4 микрокоманд первой микрокоманды выполняемой микропрограммы с целью упрощения не показаны). Так как на вход первого дешифратора I8f блока 7 проверки уело- ВИЙ поступает единичный код, то на его дополнительном выходе устанавливается сигнал логической единицы, который поступает на выход первого элемента ИЛИ 20j, и так как этот вы- ход имеет наивысший приоритет, то на первом выходе 13( блока 7 проверки условий устанавливается сигнал логической единицы, а на остальн1)1х выходах этого блока устанавливаются сигналы логического нуля. Такая ситуация на выходах 13i-133 блока 7 проверки условий соответствует ;тому, что по синхросигналу во втором такте работы устройства в регистр 4 микрокоманд запишется код микроопераций П,, коды с(, и соответственно первого и второго логических условий следующей микрокоманды, а в регистры первого, второго и третьего блоков 1{ -1 формирования адреса за- пишутся соответственно адреса А, В, и Сд, Одновременно с выполнением микроопераций 3, происходит чтение из блоков 2,-2 3 памяти следующих возможных микрокоманд по указанным выше яд- ресам. Если логическое условие с, выполнится, то на первом выходе 13(, блойа 7 проверки условий появитс сигнал логической единицы, а на остальных выходах 13 и 135 - сигналы логического нуля. Эти значения сигналов на выходах 13,-13 блока 7 проверки условий соответствуют тому, что в

5

10f520 25 JQ 55055

35

40

третьем такте работы устройства по синхросигналу в регистре 4 микрокоманд запишется код микроопераций ц, , коды €, и соответственно первого и второго логических условий, а в регистры первого, второго и третьего блоков формирования адреса запишутся соответственно адреса А, В, и C.J. Если же логическое условие о;, не выполнится, то на выходе первого элемента ИЛИ 20,, блока 7 проверки условий устанавливается сигнал логического нуля. Если второе логическое условие л-г выполнится,то на выходе второго элемента ИЛИ 20 блока 7 проверки условий устанавливается сигнал логической единицы. Так как на первом более приоритетном входе узла 7 приоритетного кодирования присутствует сигнал логического нуля, то на втором выходе 13 блока 7 проверки условий устанавливается сигнал логической единицы, а на остальных его выходах 13j, 13, - сигнал логических нулей. Это значение, сигналов на выходах 13, блока 7 проверки условий соответствует тому, что по синхросигналу в третьем такте работы устройства в регистр 4 микрокоманд запишется код микроопераций у, код oi первого логического услойия и единичный код второго логического условия четвертой микрокоманды, а в регистры первого, второго и третьего блоков Ц Ц формирования адреса запишутся соответственно адреса А,, В( и 0. Если же и второе логическое условие не выполнится, то на выходе и второго элемента ИЛИ 20j блока 7 проверки условий установится сигнал логического нуля. Поэтому на выходах узла 11 приоритетного кодирования устанавливаются сигналы логического нуля, а на выходе элемента ИЛИ-НЕ 22

установится сигнал логической единицы. Такое значение сигналов на выходах 3,-13з блока 7 проверки условий соответствует тому, что в третьем такте работы устройства по синхросигналу в регистр 4 микрокоманд запишется код микроопераций tj, нулевое значение первого и второго логических условий третьей микрокоманды, а в регистры первого, второго и третьего блоков l,- формирования адреса запишутся соответственно адреса 0,0 и С. Подобным образом устройство работает и в других тактах при выполнении остальных микрокоманд. Если в выполняемой микрокоманде анализируется только одно логическое условие,, то оно может быть принято в микрокоман де как первым, так и вторым, при этом значение соответственно второго и первого логических условий должно быть нулевым (или единичным), или только нулевым. Примером такой микро команды может служить четвертая микрокоманда на фиг, 5 и 6. Значения кодов первого и второго логических условий, равные соответственно 1 и О (или 1 и 1) используются для принудительного чтения информа дин из первого блока 2 памяти микрокоманд, а значения О и I или О и О - для принудительного чтения информации соответственно из второго и третьего блоков 2 и 2 памяти микрокоманд.

Формула изобретения

, Микропрограммное устройство управления, содержащее два блока памяти микрокоманд, два блока формирования адреса, коммутатор, регистр микрокоманд и блок проверки условий, причем выход : кода микроопераций рет гистра микрокоманд является выходом устройства, группа выходов кодов логических условий регистра микрокоманд соединена с первой группой входов блока проверки условий, вторая

группа входов которого является груп-35 тенци ала, устройства, причем блок пропой входов логических условий устройства, информационный вход регистра микрокоманд соединен с выходом коммутатора, первый и второй информационные входы которого соединены соответственно с выходами кодов микроопераций и логических усл.овий первого и второго блоков памяти микрокоманд, адресные входы которых соедипроверки условий содержит п дешифраторов, п блоков элементов И, п элементов КШИ, 1(1иф1эатор приоритетного кодирования и элемент ИЛИ-НЕ, причем первые 40 входы элементов И i-ro блока элементов И соединены с соответствующими вxoдa ш группы входов логических условий з стройства, а вторые входы соединены с соответствующими выходами

нены с выходами соответственно перво-45 i-ro дешифратора, входы которого го и второго блоков формирования адреса, отличающееся тем, что, с целью повьппения быстродействия устройства за счет обеспечения одновременного анализа п условий ,. 50 оно содержит дополнительно п- блоков памяти микрокоманд и п-1 блоков формирования адреса, причем с третьего по (п-И)-й блоков формирования адреса соединены с адресными входами соответствующих с третьего по

55

ляются первой группой входов блока проверки условий, выходы элементов И i-ro блока элементов И и дополнительный выход i-ro дешифратора соединены с входами i-ro элемента ИЛИ, выход которого соединен с соответствующим входом элемента ИЛИ-НЕ и шифратора приоритетного кодирования, выходы которого вместе с выходом элемента ШШ- НЕ являются выходами блока проверки условий.

(n-t-l)ro блоков памяти микрокоманд, выходу кодов микроопераций и логических з словий которых соединены с соответствующими с третьего по (п- -О-й 5 информационными входами коммутатора, ( i-; п) адресный выход k-ro (I i k п + 1) блока памяти микрокоманд соединен с k-м информационным входом (i+l)-ro блока формирования

О адреса (для всех значений i 5 k) и с (k-l)-M информационным входом i-ro блока формирования адреса (для всех значений i k), выходы блока проверки условий соединены соответственно

с входами управления формированием адресов блоков формирования адреса и ком:мутатора, причем каждый из блоков формирования адреса содержит регистр , коммутатор и комбинационный

20 сумматор, причем выход регистра соединен с информационным входом сумматора и является выходом блока, информационный вход регистра соединен с выходом Коммутатора управляющий вход которого

является входом управления формированием адресов блока, j-ый (I j 5 п+1 информационный вход коммутатора К-го блока формирования адреса соединен с j-ым информационным входом блока (для

30 всех значений j -; k), с выходом сумматора (для значения j-k) и с (j-l)-M информационным входом блока (для всех значений j k)g вход переноса сумматора подключен к шине единичного по-

проверки условий содержит п дешифраторов, п блоков элементов И, п элементов КШИ, 1(1иф1эатор приоритетного кодирования и элемент ИЛИ-НЕ, причем первые входы элементов И i-ro блока элементов И соединены с соответствующими вxoдa ш группы входов логических условий з стройства, а вторые входы соединены с соответствующими выходами

i-ro дешифратора, входы которого

ляются первой группой входов блока проверки условий, выходы элементов И i-ro блока элементов И и дополнительный выход i-ro дешифратора соединены с входами i-ro элемента ИЛИ, выход которого соединен с соответствующим входом элемента ИЛИ-НЕ и шифратора приоритетного кодирования, выходы которого вместе с выходом элемента ШШ- НЕ являются выходами блока проверки условий.

3r

Фив.1

Фиъ..

Фиг.З

Фмг.

8.1

О AzdjT

.

Фиг. 5

Первм /WW/VAW

Pa iijiof fioffo

Составитель В. Криворучко Редактор И. Сегменик Техред И.Гайдош Корректор М. Максимишинец

2652/52

Тираж 671 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

BiriopoS 8ивл понпнш fWnpoMfMiH9

Tpemuv нанята fWKitOKaMaHi

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1985 |

|

SU1381503A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1134936A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Программируемый контроллер | 1990 |

|

SU1714599A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1275442A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1257645A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108449A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1151962A1 |

| Устройство для программного управления и контроля | 1991 |

|

SU1784943A1 |

| Программируемый контроллер | 1988 |

|

SU1642446A1 |

Изобретение относится к вычислительной технике и может быть исполь- .зовано в вычислительных устройствах, и системах. Цепь изобретения - повыт. шение быстродействия устройства за счет обеспечения одновременного анализа п условий . Цель изобретения достигается за счет введения в устройство п-1 блоков памяти микрокоманд и (п-1) блоков формирования адреса с соответствующими функциональными связями между ними и известными блоками устройства. 6 ил. с S NS 00

| Путков В | |||

| Н.,Сбросов И | |||

| И | |||

| и Бекетов С | |||

| В | |||

| Электронные вычислительные устройства | |||

| Минск: Вышэйшая школа, 1981, с | |||

| Синхронизирующее устройство для аппарата, служащего для передачи изображений на расстояние | 1920 |

|

SU225A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Микропрограммное устройство управления | 1981 |

|

SU964640A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1151962A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-15—Публикация

1984-11-05—Подача