00

00 :л

00

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1257645A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

| Многопрограммное устройство управления | 1984 |

|

SU1231501A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1629910A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1310818A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1133595A1 |

| Асинхронное устройство для программного управления | 1987 |

|

SU1481712A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1134936A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2013803C1 |

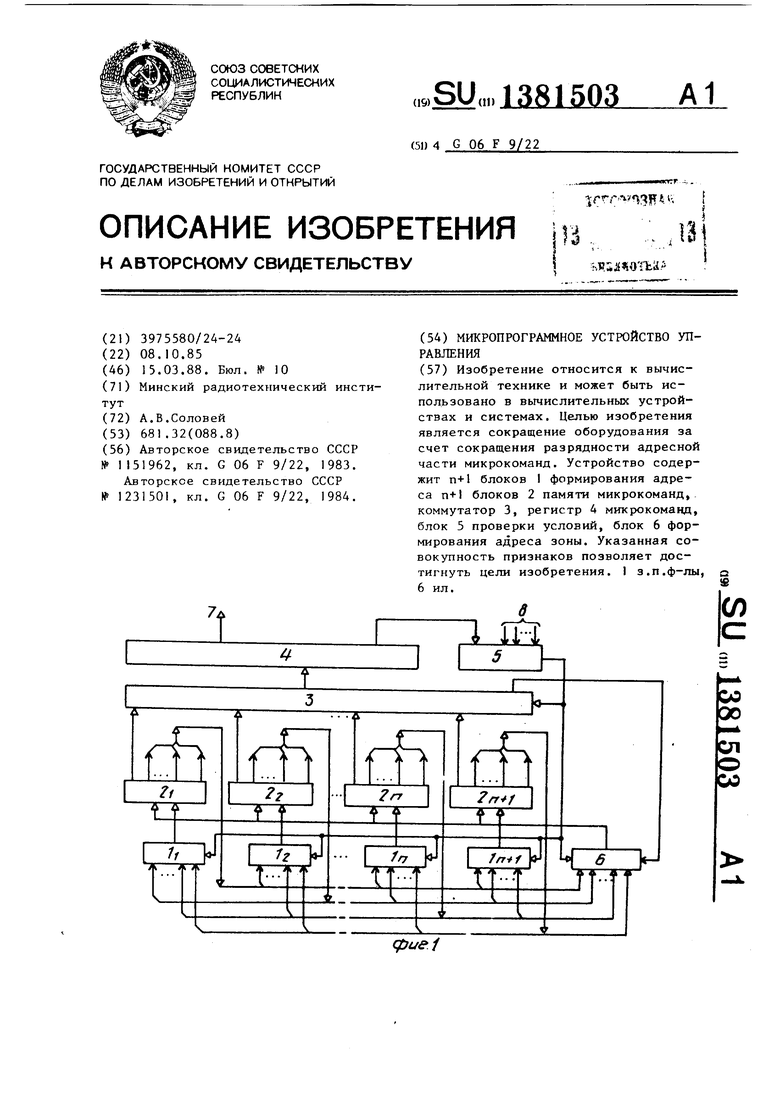

Изобретение относится к вычислительной технике и может быть использовано в вычислительных устройствах и системах. Целью изобретения является сокращение оборудования за счет сокращения разрядности адресной части микрокоманд. Устройство содержит п+1 блоков I формирования адреса п+1 блоков 2 памяти микрокоманд, коммутатор 3, регистр 4 микрокоманд, блок 5 проверки условий, блок 6 формирования адреса зоны. Указанная совокупность признаков позволяет достигнуть цели изобретения. 1 з.п.ф-лы, 6 ил. в Q (Л

фие1

Изобретение относится к вычислительной технике и может быть использовано в вычислительных устройствах и системах.

Целью изобретения является сокращение количества используемого оборудования за счет сокращения разрядности адресной части микрокоманд.

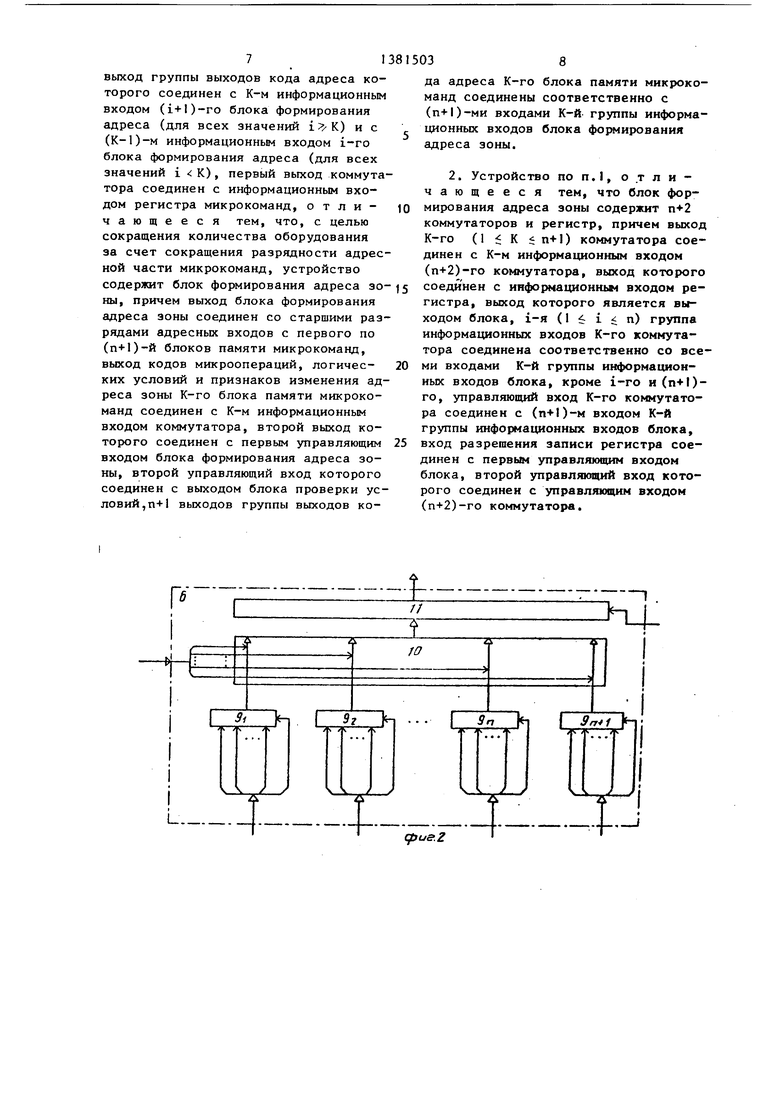

На фиг.1 приведена структурная схема микропрограммного устройства управления; на фиг.2 - функциональная схема, блока формирования адреса зоны; на фиг.З - схема блока формирования адреса; на фиг.4 .- схема бло ка проверки условий: на фиг.5 и 6 - пример граф-схемы микропрограммы и принцип ее размещения в блоках памяти устройства для случая .

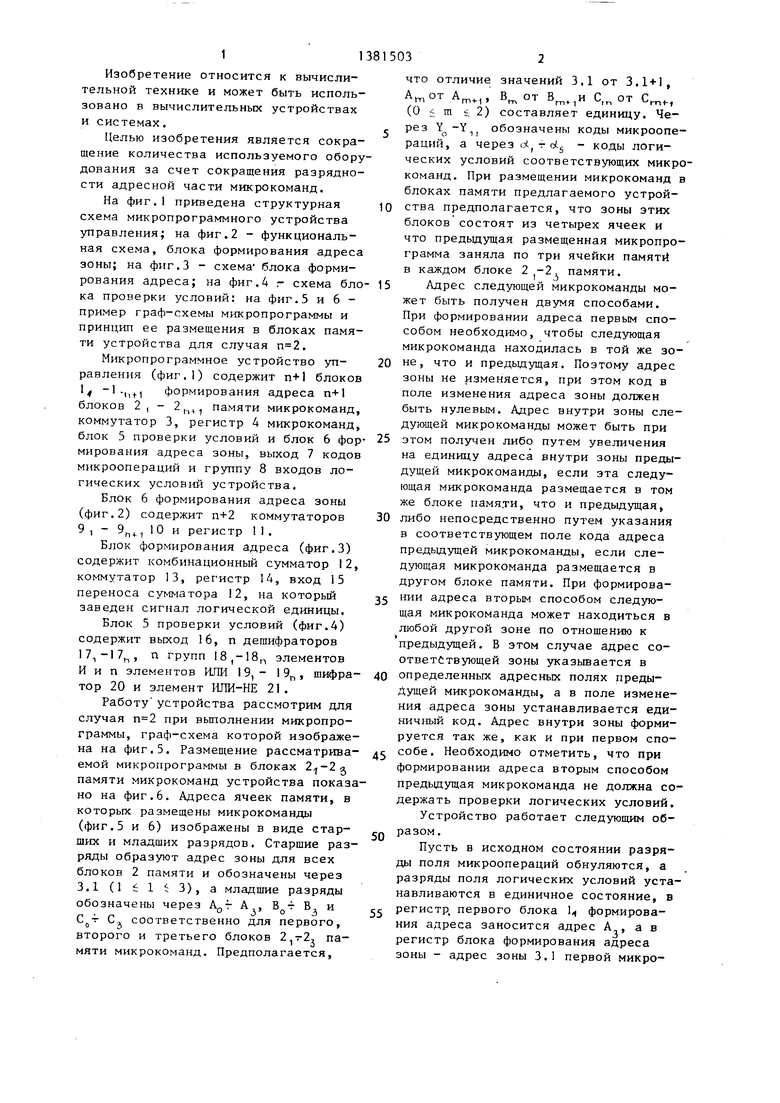

Микропрограммное устройство управления (фиг,1) содержит п+1 блоков ivti формирования адреса п+1 блоков 2, - 2 памяти микрокоманд, коммутатор 3, регистр 4 микрокоманд, блок 5 проверки условий и блок 6 формирования адреса зоны, выход 7 кодов микроопераций и группу 8 входов логических условий устройства.

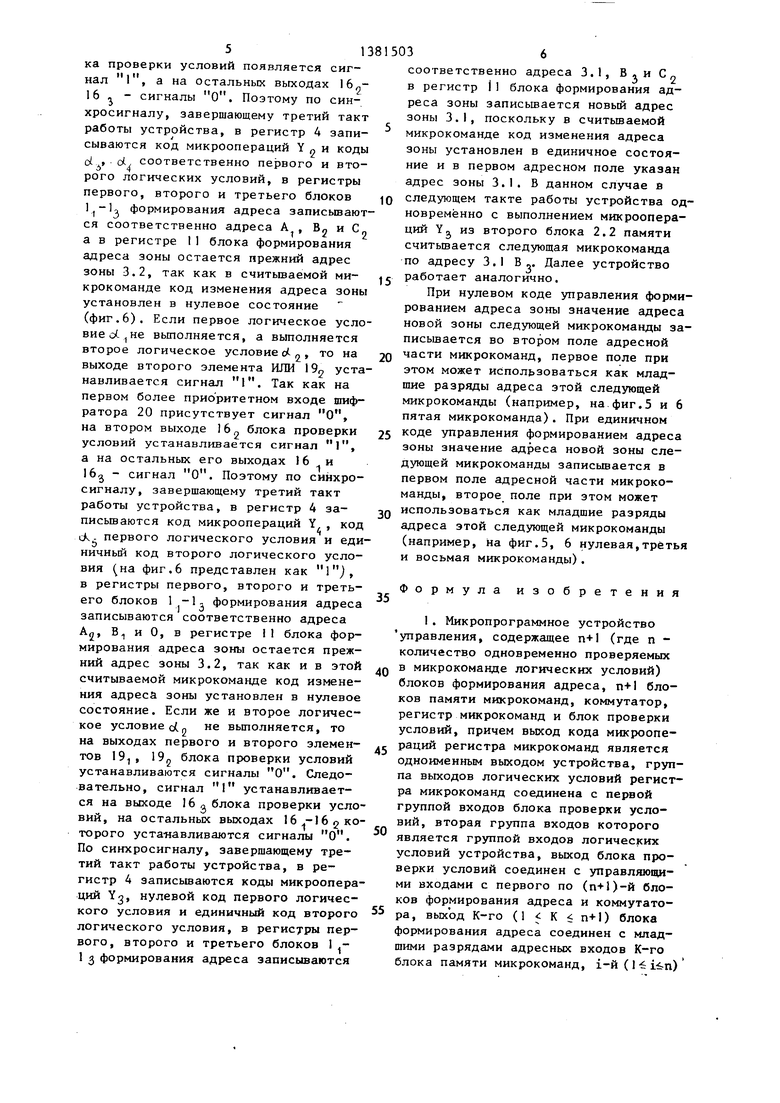

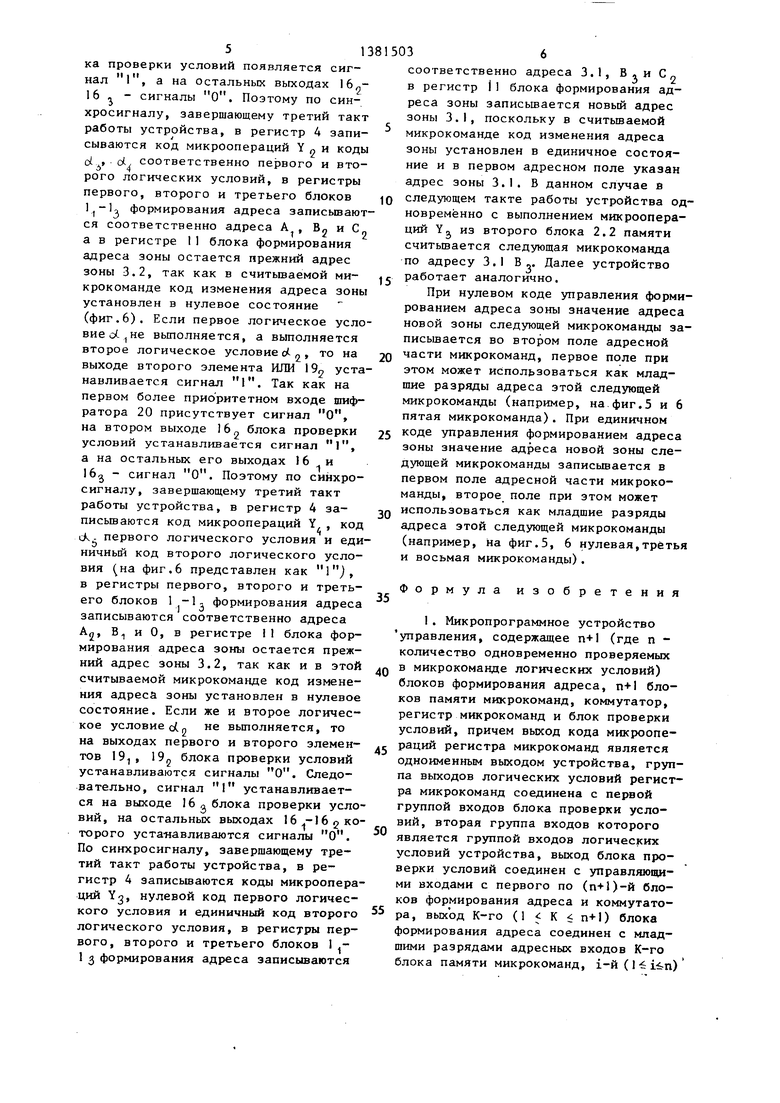

Блок 6 формирования адреса зоны (фиг.2) содержит п+2 коммутаторов 9 1 - 9 10 и регистр 11.

Блок формирования адреса (фиг.З) содержит комбинационный сумматор 12, коммутатор 13, регистр 14, вход 15 переноса сумматора 12, на который заведен сигнал логической единицы. Блок 5 проверки условий (фиг.4) содержит выход 16, п дещифраторов , п групп 18,-18г, элементов И и п элементов ИЛИ 19,- 19, шифратор 20 и элемент ИЛИ-НЕ 21.

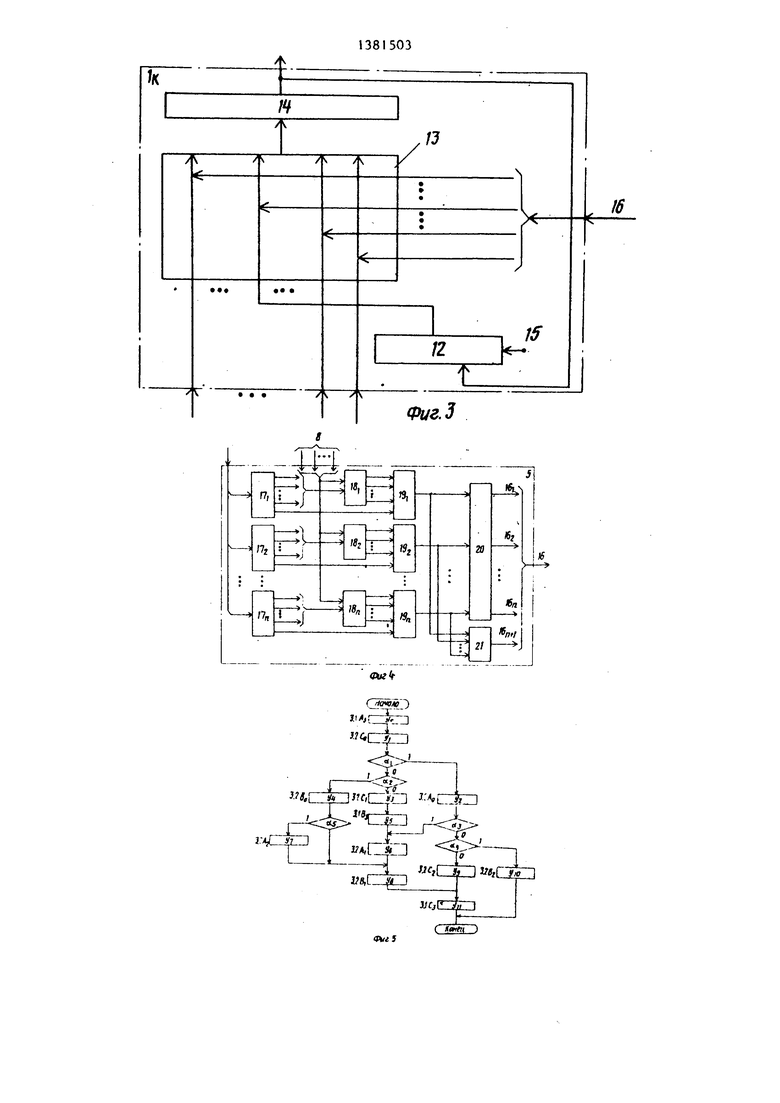

Работу устройства рассмотрим для случая при выполнении микропрограммы, граф-схема которой изображена на фиг.З. Размещение рассматриваемой микропрограм 1ы в блоках памяти микрокоманд устройства показано на фиг.6. Адреса ячеек памяти, в которых размещены микрокоманды (фиг.З и 6) изображены в виде старших и младших разрядов. Старшие разряды образуют адрес зоны для всех блоков 2 памяти и обозначены через 3.1(1 li3),a младшие разряды обозначены через Agf А , В.. и Cj соответственно для первого, второго и третьего блоков , памяти микрокоманд. Предполагается,

0

5

5

5

0

0

что отличие значений 3.1 от 3., AM от А,, В от В,,и С, от С, (О m i 2) составляет единицу. Через обозначены коды микроопераций, а через cf. т d - коды логических условий соответствующих микрокоманд. При размещении микрокоманд в блоках памяти предлагаемого устройства предполагается, что зоны этих блоков состоят из четырех ячеек и что предыдущая размещенная микропрограмма заняла по три ячейки памяти в каждом блоке 2-2. памяти.

Адрес следующей микрокоманды может быть получен двумя способами. При формировании адреса первым способом необходимо, чтобы следующая микрокоманда находилась в той же зоне, что и предыдущая. Поэтому адрес зоны не изменяется, при зтом код в поле изменения адреса зоны должен быть нулевым. Адрес внутри зоны следующей микрокоманды может быть при этом получен либо путем увеличения на единицу адреса внутри зоны предыдущей микрокоманды, если эта следующая микрокоманда размещается в том же блоке памяти, что и предыдущая, либо непосредственно путем указания в соответствующем поле кода адреса предыдущей микрокоманды, если следующая микрокоманда размещается в другом блоке памяти. При формировании адреса вторым способом следующая микрокоманда может находиться в любой другой зоне по отношению к предыдущей. В этом случае адрес соответствующей зоны указьтается в определенных адресных полях предыдущей микрокоманды, а в поле изменения адреса зоны устанавливается единичный код. Адрес внутри зоны формируется так же, как и при первом спос собе. Необходимо отметить, что при формировании адреса вторым способом предыдущая микрокоманда не должна содержать проверки логических условий. Устройство работает следующим образом.

Пусть в исходном состоянии разряды поля микроопераций обнуляются, а разряды поля логических условий устанавливаются в единичное состояние, в

е регистр, первого блока 1 формирова0

ния адреса заносится адрес А

3

а в

регистр блока формирования адреса зоны - адрес зоны 3.1 первой микро3

команды вьтолняемой микропрограммы (цепи занесения начальных адресов и установки в нулевое и единичное состояния соответствующих разрядов регистра 4 микрокоманд, а также цепи синхронизации не показаны). Так как на вход первого дешифратора 17 блока 5 проверки условий поступает единичный код, то на его дополнительном выходе устанавливается сигнал 1, который поступает через первый элемент ИЛИ 19 на первый вход шифратора 20. Поскольку зтот вход имеет наивысший приоритет, то на первом выходе 16 блока 5 проверки условий устанавливается сигнал 1,на остальных выходах устанавливаются сигналы О. Поэтому коммутатор 3 настраивается на выборку информации с выхода первого блока 2 памяти,из которого считывается микрокоманда по адресу 3.1 А ; коммутатор 10 блока формирования адреса зоны настраивается на выборку информации с выхода первого коммутатора I9 , на первый вход которого с второго выхода группы выходов кода адреса первого блока 2 памяти поступает адрес С, а на второй вход с первого выхода группы выходов кода адреса первого блока 2 памяти - адрес новой зоны 3.2, который и передается на выход коммутатора 9., т.к. на его управляющий вход с третьего выхода группы выходов кода адреса первого блока 2 памяти поступает сигнал 1 (на фиг.6 в поле кода управления формированием адреса зоны считываемой микрокоманды установлен единичный код); коммутаторы первого, второго и третьего блоков 1-1, формирования адреса настраиваются на выборку информации соответственно с выхода сумматора . первого блока формирования адреса и с первого и второго выходов группы выходов кода адреса первого блока 2 , памяти. По синхросигналу, завершающему первый такт работы устройства, в регистр 4 записываются код микроопераций Y и нулевые коды первого и второго логических условий (на. фиг.6 обозначены как О), в регистры первого, второго и третьего блоков 3 формирования адреса - соответственно А.,, 3.2 и GO, так как на вход разрешения записи регистра блока 6 с второго выхода коммутатора

815034

3 поступает сигнал 1 (на фиг.6 в считьшаемой микрокоманде код изменения адреса зоны установлен в единич- 1ное состояние), то в регистр 11 за- письшается новый адрес зоны 3.2.

Одновременно с выполнением мгшро- операций Y из блоков памяти происходит чтение информации соответIQ ственно по адресам 3.2 А, 3.2 3.2 и 3.2 Ср. Но так как на входы первого и второго дешифраторов 17 и 17 блока 5 проверки условий поступают нулевые коды, то на выходе 16 блока

|г 5 ус Ганавливается сигнал 1, а на остальных выходах 16,-16 сигналы О. Следовательно, коммутатор 3 настраивается на выборку информации с выхода третьего блока 2 памяти, ком2Q мутатор 10 блока формирования адреса зоны - с выхода третьего коммутатора 9„, но так как с второго выхода коммутатора 3 на вход разрешения записи регистра 11 поступает сигнал О (на

25 фиг.6 в считываемой микрокоманде Y, код изменения адреса зоны установлен в нулевое состояние), то по синхросигналу в этом регистре информация не меняется. Коммутаторы первого,

2Q второго и третьего блоков I -I формирования адреса- настраиваются на выборку информации соответственно с первого и второго выходов группы выходов кода адреса третьего блока

3

памяти и сумматора третье

J- . ГО блока формирования адреса.Итак,

по синхросигналу, завершающему второй такт работы устройства, в регистр 4 записьшаются код микроопераций Y и кодыЫ, Ы,-, соответственно

первого и второго логических условий, в регистре 11 блока формирования адреса зоны остается прежней адрес зоны 3.2, в регистры первого, второго и третьего блоков 1 -1. формирования адреса записываются соответственно адреса А, В и С.

Одновременно с выполнением микроопераций Y. происходит чтение возможных следующих микрокоманд из блоков

памяти соответственно по адресам 3.2А, 3..2С.В зависимости от выполнения или не выполнения условий ы и о( л при выполнении текущей микрокоманды на выходах

блока проверки условий устанавливаются следующие сигналы. Если первое логическое условие d выполняется, то на первом выходе 16 блока проверки условий появляется сигнал 1, а на Остальных выходах 16л 16 , - сигналы О. Поэтому по синхросигналу, завершающему третий такт работы устройства, в регистр 4 записываются код микроопераций Y „ и коды

oi , d, соответственно первого и рого логических условии, в регистры

первого, второго и третьего блоков 1|-Ц формирования адреса записьшают- ся соответственно адреса А , Bj и С а в регистре I1 блока формирования адреса зоны остается прежний адрес зоны 3.2, так как в считьшаемой микрокоманде код изменения адреса зоны установлен в нулевое состояние (фиг.6). Если первое логическое условие ot не вьшолняется, а выполняется второе логическое условие of- „ то на выходе второго элемента ИЛИ 192 навливается сигнал 1. Так как на первом более приоритетном входе шифратора 20 присутствует сигнал О, на втором выходе 6у блока проверки условий устанавливается сигнал 1, а на остальных его выходах 16 и 16 - сигнал О. Поэтому по синхросигналу, завершающему третий такт работы устройства, в регистр 4 за- письшаются код микроопераций Y , код ck- первого логического условия и единичный код второго логического условия (на фиг.6 представлен как , в регистры первого, второго и третьего блоков 1 Ij формирования адреса записываются соответственно адреса АЛ, В и О, в регистре I1 блока формирования адреса зоны остается прежний адрес зоны 3.2, так как и в этой считываемой микрокоманде код изменения адреса зоны установлен в нулевое состояние. Если же и второе логическое условие о(,| не вьтолняется, то на выходах первого и второго элементов 19,, 192 проверки условий устанавливаются сигналы О. Следовательно, сигнал I устанавливается на выходе 16 а блока проверки условий, на остальных выходах 16,-16 которого уста-навливаются сигналы О. По синхросигналу, завершающему третий такт работы устройства, в регистр 4 записьшаются коды микроопераций Yg, нулевой код первого логического условия и единичный код второго логического условия, в регистры первого, второго и третьего блоков 15 формирования адреса записываются

соответственно адреса 3.1, В.и С„ в регистр I1 блока формирования адреса зоны записьюается новый адрес зоны 3.1, поскольку в считьюаемой

микрокоманде код изменения адреса зоны установлен в единичное состояние и в первом адресном поле указан адрес зоны 3.1. В данном случае в

следующем такте работы устройства одновременно с выполнением микроопераций YJ из второго блока 2.2 памяти считьшается следующая микрокоманда по адресу 3.1 В.. Далее устройство

работает аналогично.

При нулевом коде управления формированием адреса зоны значение адреса новой зоны следующей микрокоманды за- письшается во втором поле адресной

части микрокоманд, первое поле при этом может использоваться как младшие разряды адреса этой следующей микрокоманды (например, на.фиг.5 и 6 пятая микрокоманда). При единичном

коде управления формированием адреса зоны значение адреса новой зоны следующей микрокоманды записывается в первом поле адресной части микрокоманды, второе поле при этом может

использоваться как младшие разряды адреса этой следующей микрокоманды (например, на фиг.5, 6 нулевая,третья и восьмая микрокоманды).

35

Формула изобретения

в микрокоманде логических условий) блоков формирования адреса, п+1 блоков памяти микрокоманд, коммутатор, регистр микрокоманд и блок проверки условий, причем выход кода микроопераций регистра микрокоманд является одноименным выходом устройства, группа выходов логических условий регистра микрокоманд соединена с первой группой входов блока проверки условий, вторая группа входов которого является группой входов логических условий устройства, выход блока проверки условий соединен с управляющими входами с первого по ()-й блоков формирования адреса и коммутатора, выход К-го (1 f К п+О блока формирования адреса соединен с младшими разрядами адресных входов К-го блока памяти микрокоманд, i-й ( 1 б )

7I

выход группы выходов кода адреса которого соединен с К-м информационным входом (i+I)-ro блока формирования адреса (для всех значений ) и с (К-1)-м информационным входом i-ro блока формирования адреса (для всех значений i i К), первый выход коммута тора соединен с информационным входом регистра микрокоманд, отличающееся тем, что, с целью сокращения количества оборудования за счет сокращения разрядности адресной части микрокоманд, устройство содержит блок формирования адреса зоны, причем выход блока формирования адреса зоны соединен со старшими разрядами адресных входов с первого по (п+1)-й блоков памяти микрокоманд, выход кодов микроопераций, логических условий и признаков изменения адреса зоны К-го блока памяти микрокоманд соединен с К-м информационным входом коммутатора, второй выход которого соединен с первым управляющим входом блока формирования адреса зоны, второй управляющий вход которого соединен с выходом блока проверки условий, п+1 выходов группы выходов коза 15038

да адреса К-го блока памяти микрокоманд соединены соответственно с (п-|-1)-ми входами К-й группы информационных входов блока формирования адреса зоны.

соединен с информационным входом регистра, выход которого является выходом блока, i-я (I 6 i п) группа информационных входов К-го коммутатора соединена соответственио со всеми входами К-й группы информационных входов блока, кроме i-ro и(n+l)- го, управляющий вход К-го коммутатора соединен с (п+О-м входом К-й группы информационных входов блока,

вход разрешения записи регистра соединен с первым управляющим входом блока, второй управляющий вход которого соединен с управляющим входом (п+2)-го коммутатора.

gjus.Z

:

Д-.

л

it , J.Lj

QATSJ

:

Д-.

ФигУ

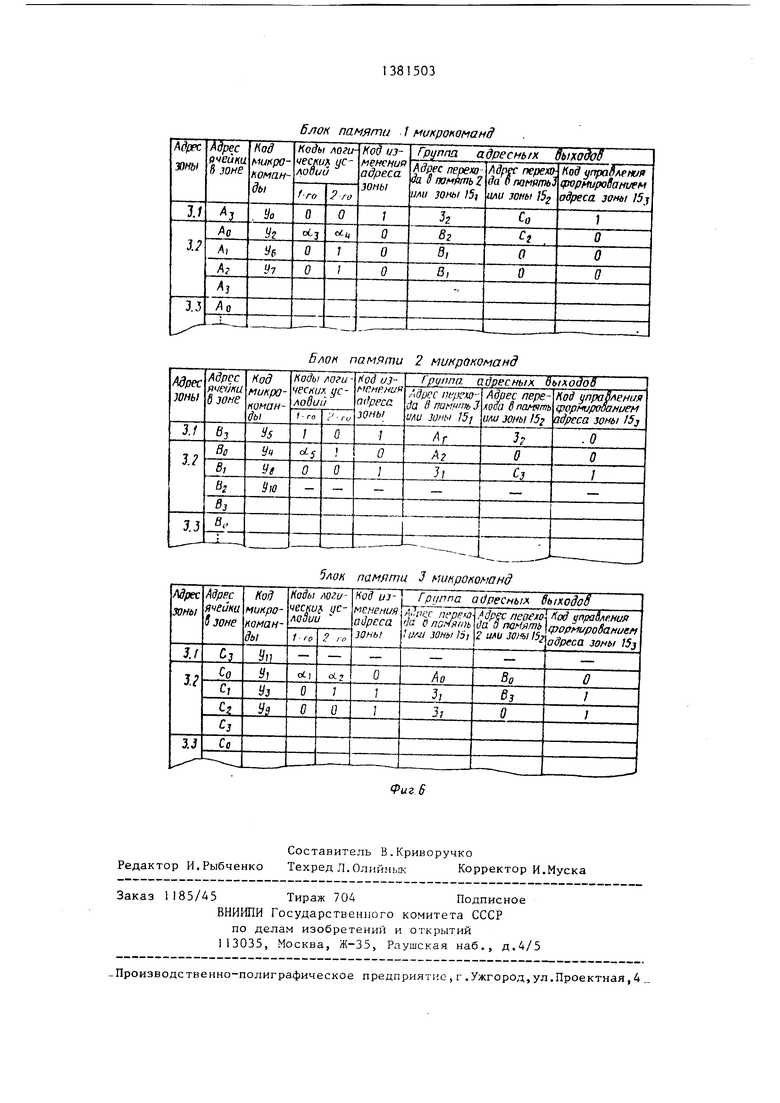

Блок памяти I t uKpoMHand

Блок памяти 2 микрокоманд

5лок памяти 3 микрокоманд

| 3975580/24-24 08.10.85 15.03.88 | |||

| Бюл | |||

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многопрограммное устройство управления | 1984 |

|

SU1231501A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-15—Публикация

1985-10-08—Подача