1 .1290303

Изобрете.ние относится к вычисли з

тельной технике,и может быть иС пользовано в арифметических устройствах универсалы-1ык и специализированных вычислителей, обрабатывающих двоично-десятичную информацию.

Цель изобретения - повышение быстродействия.

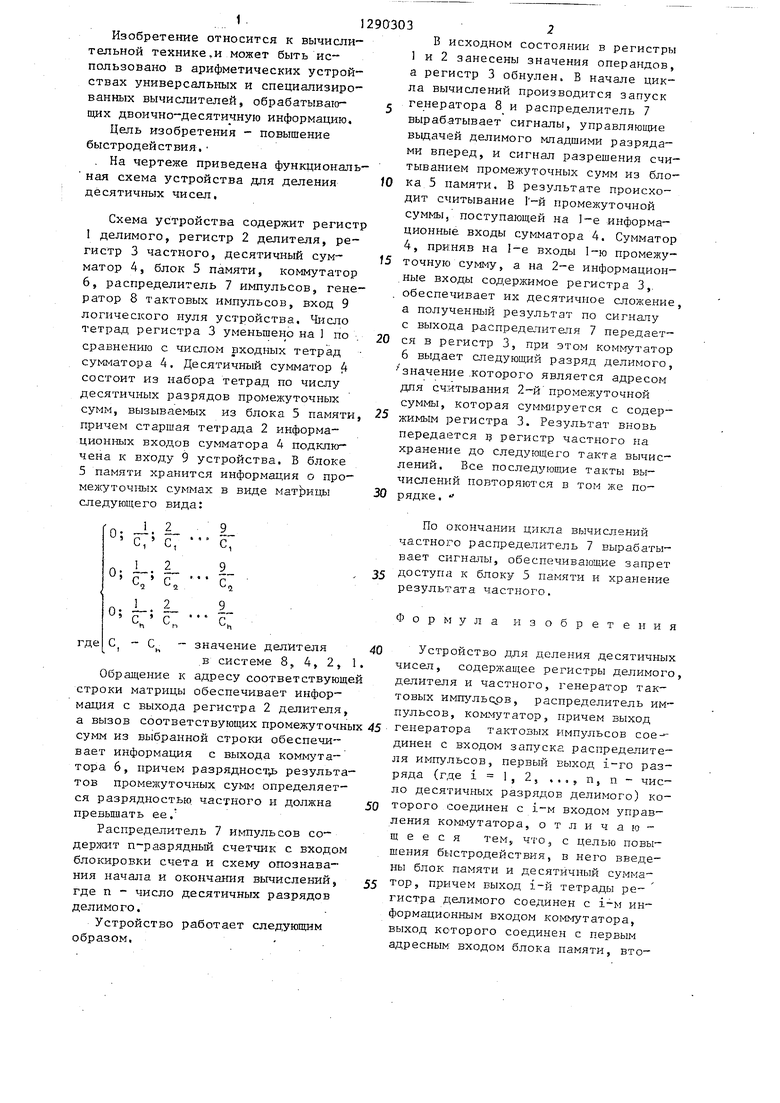

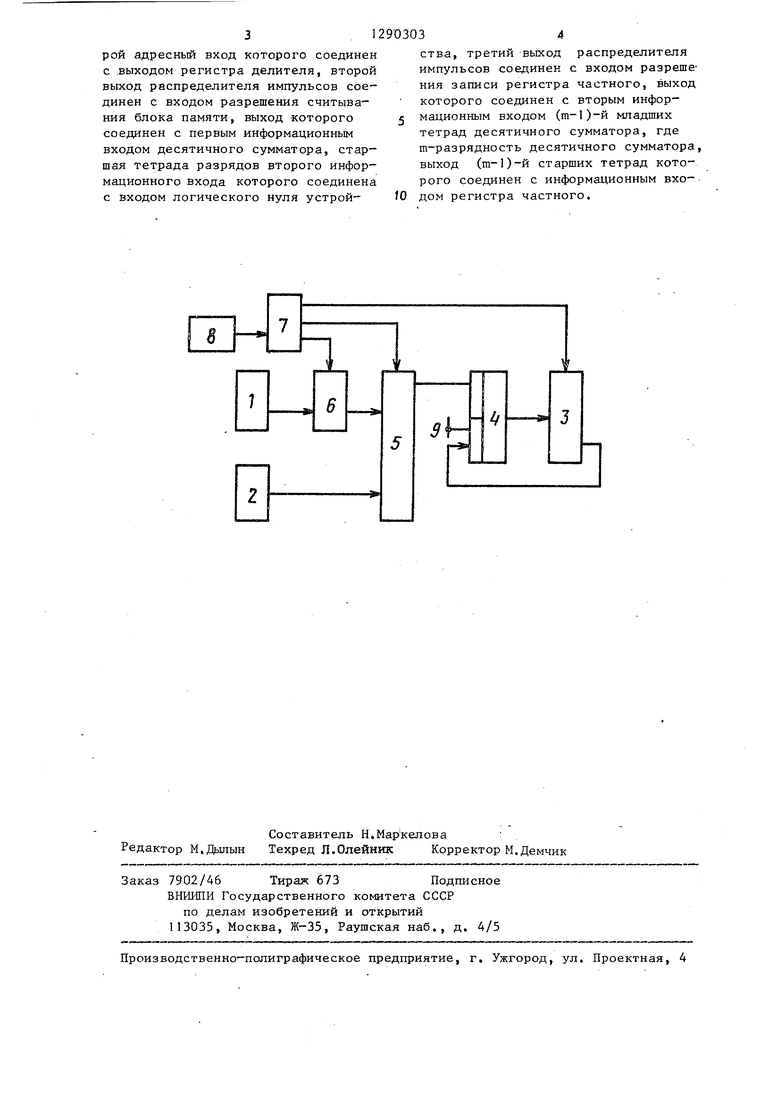

. На чертеже приведена функциональная схема устройства для деления десятичных чисел.

Схема устройства содержит регист I делимого, регистр 2 делителя, регистр 3 частного, десятичный сумматор 4, блок 5 памяти, коммутатор 6, распределитель 7 импульсов, генератор 8 тактовых импульсов, вход 9 логического нуля устройства. Число тетрад регистра 3 уменьшено на 1 по

сравнению с числом входных тетрад сумматора 4, Десятичный сумматор 4 состоит из набора тетрад по числу десятичных разрядов промежуточных сумм, вызываемых из блока 5 памяти причем старшая тетрада 2 информационных входов сумматора 4 подключена к входу 9 устройства. В блоке 5 памяти хранится информация о промежуточных суммах в виде мат|зицы следующего вида:

где

в системе 8., 4, 2, 1.

Обращение к адресу соответствующей строки матрицы обеспечивает информация с выхода регистра 2 делителя, а вызов соответствующих промежуточных сумм из выбранной строки обеспечивает информация с выхода тора 6, причем разрядности результатов промежуточных сумм определяется разрядностью, частного и должна превышать ее.

Распределитель 7 импульсов со- дерлдат п-раарядный счетчик с входом блокировки счета и схему опознавания начала и оконча шя вычислений, где п - число десятичных разрядов делимого.

Устройство работает следующим образом, .

5

0

5

0

5

В исходном состоянии в регистры 1 и 2 занесены значения операндов, а регистр 3 обнулен. В начале цикла вычислений производится запуск генератора 8 и распределитель 7 вырабатывает сигналы, управляющие вьщачей делимого младшими разрядами вперед, и сигнал разрешения считыванием промежуточных сумм из блока 5 памяти. В результате происходит считывание Г-й промежуточной суммы, поступающей на 1-е информационные входы сумматора 4. Сумматор 4, приняв на 1-е входы 1-ю промежуточную сумму, а на 2-е информационные входы содержимое регистра 3,. обеспечивает их десятичное сложение, а полученный результат по сигналу с выхода распределителя 7 передается в регистр 3, при этом коммутатор 6 выдает следующий разряд делимого, значение .которого является адресом для считывания 2-и промежуточной суммы, которая суммируется с содержимым регистра 3. Результат вновь передается в регистр частного на хранение до следующего такта вычислений. Все последующие такты вычислений повторяются в том же порядке .

По окончании цикла вычислений частного распределитель 7 вырабатывает сигналы, обеспечивающие запрет доступа к блоку 5 памяти и храпение результата частного.

Формула изобретен и

я

Устройство для деления десятичных чисел, содержащее регистры делимого, делителя и частного, генератор тактовых импульорв, распределитель импульсов, коммутатор, причем выход генератора тактовых импульсов сое-- динен с входом запуска распределителя импульсов, первый выход i-ro разряда (где i 1, 2, ..., п, п- число десятичных разрядов делимого) которого соединен с i-м входом управления коммутатора, отличающееся тем, чтоэ с целью повышения быстродействия, в него введены блок памяти и десятичный сумматор, причем выход i-й тетрады регистра делимого соединен с информационным входом кo c ryтaтopa, выход которого соединен с первым адресным входом блока памяти, вто3129D303

рой адресный вход которого соединен с .выходом регистра делителя, второй выход распределителя импульсов соединен с входом разрешения считывания блока памяти, выход которого 5 соединен с первым информационным входом десятичного сумматора, старшая тетрада разрядов второго информационного входа которого соединена с входом логического нуля устрой- О

ства, третий выход распределителя импульсов соединен с входом разрешения записи регистра частного, выход которого соединен с вторым информационным входом (т-1)-й младших тетрад десятичного сумматора, где т-разрядность десятичного сумматора выход (т-1)-й старших тетрад которого соединен с информационным входом регистра частного.

3

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для деления двоичных чисел | 1984 |

|

SU1233139A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Преобразователь двоичного кода смешанных чисел в двоично-десятичный код | 1975 |

|

SU577524A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU1048472A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для деления десятичных чисел | 1976 |

|

SU744562A1 |

| Устройство для деления на константу 2 @ - 1 | 1990 |

|

SU1714596A1 |

Изобретение относится к области вычислительной техники и может быть использовано в арифметических устройствах универсальных и специализированных вычислителей, обрабатываю щих двоично-десятичную информацию. Цель изобретения - повышение быстродействия устройства. Для достижения цели в устройство введены блок памяти, .коммутатор разрядов делимого, десятичный сумматор. Время вычисления частного уменьшается за счет того, что, имея в наличии результаты готовых промежуточных сумм, процесс вычисления частного представляет собой операцию сложения друг с другом тех результатов промежуточных сумм, .числители которых составляют делимое, причем количество сложений равно числу десятичных разрядов делимого независимо от требуемой точности вычисления частного, т.е. при т-разрядном делимом число операций сложения будет равно m независимо от разрядности частного. Число тетрад регистра частного уменьшено на 1 по сравнению с числом входных тетрад сумматора. Десятичный сумматор состоит из набора тетрад по числу десятичных разрядов промежуточных сумм, вызываемых из блока памяти, причем старшая тетрада вторых информационных входов сумматора подключена к шине логического нуля устройства, что обеспечивает порядок сложения промежуточный сумм, хранимых в нем в виде соответствующей матрицы. 1 ил. с (Л ;о о со о 00

| Устройство для деления десятичных чисел | 1978 |

|

SU656087A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Арифметическое устройство | 1978 |

|

SU746507A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-15—Публикация

1985-07-03—Подача