Изобретение относится к цифровой вычислительной технике и может быть использовано для построения цифровых вычислительных машин.

Целью изобретения является сокращение оборудования.

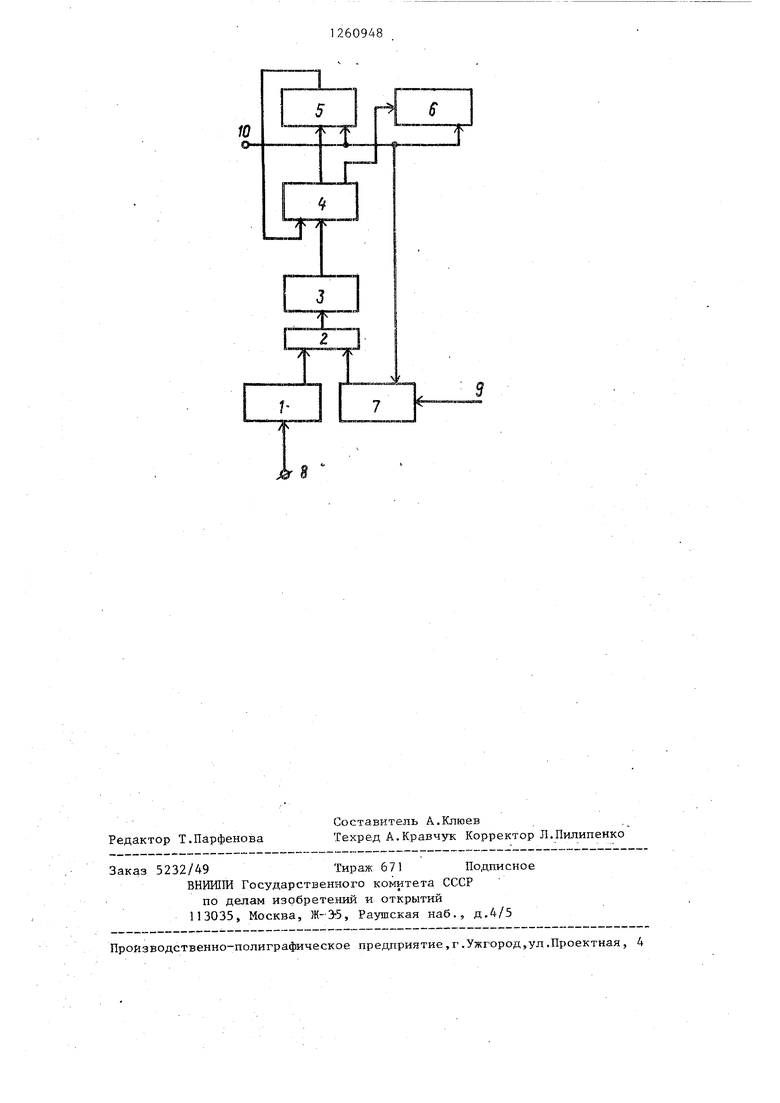

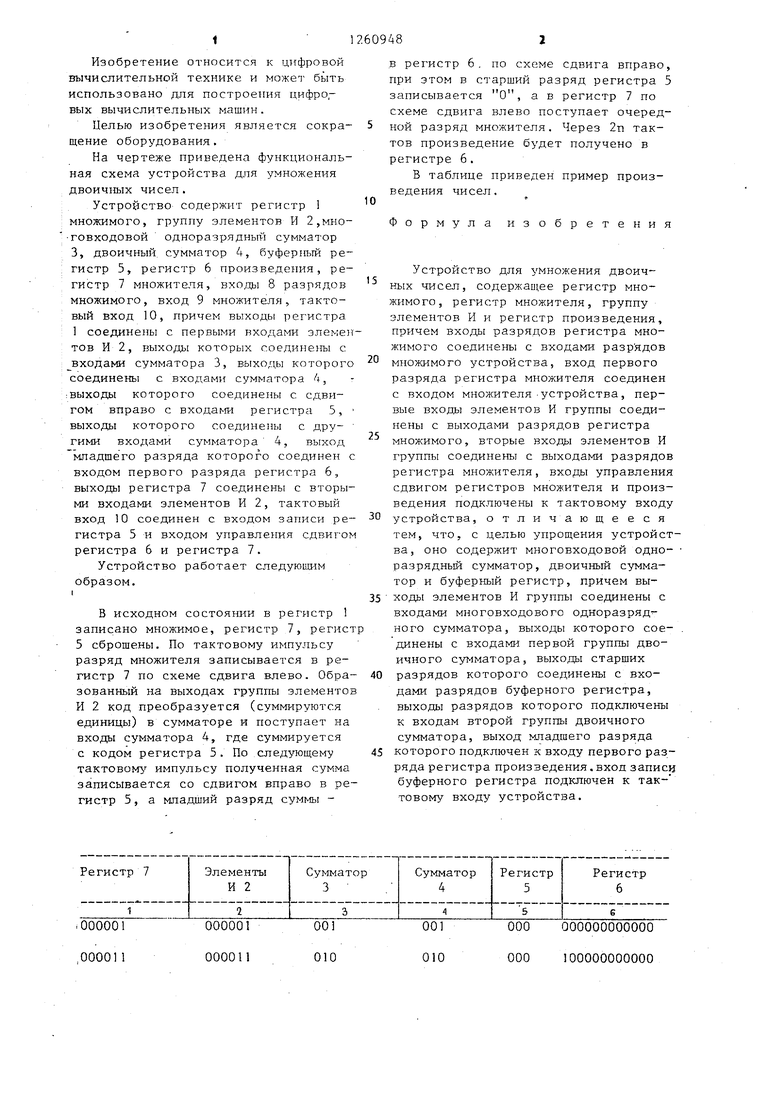

На чертеже приведена функциональная схема устройства для умножения двоичных чисел.

Устройство содержит регистр 1 множимого, группу элементов И 2,мно- говходовой одноразрядный сумматор 3, двоичный, сумматор 4, буферный регистр 5, регистр 6 произведения, регистр 7 множителя, входы 8 разрядов множимого, вход 9 множителя, тактовый вход 10, причем выходы регистра, 1 соединены с первыми входами элементов И 2, выходы которых соединены с входами сумматора 3, выходы которого соединены с входами сумматора 4, :Выходы которого соединены с сдвигом вправо с входами регистра 5, выходы которого соединены с другими входами сумматора 4, выход младшего разряда которого соединен с входом первого разряда регистра 6, выходы регистра 7 соединены с вторыми входами элементов И 2, тактовый вход 10 соединен с входом записи регистра 5 и входом управления сдвигом регистра 6 и регистра 7.

Устройство работает следующим

образом. I

В исходном состоянии в регистр 1 записано множимое, регистр 7, регист 5 сброшены. По тактовому импульсу разряд множителя записывается в регистр 7 по схеме сдвига влево. Образованный на выходах группы элементов И 2 код преобразуется (суммируются единицы) в сумматоре и поступает на входы сумматора 4, где суммируется с кодом регистра 5. По следующему тактовом -- импульсу полученная сумма записывается со сдвигом вправо в регистр 5, а младший разряд суммы

В регистр 6. по схеме сдвига вправо, при этом в старший разряд регистра 5 записывается О, а в регистр 7 по схеме сдвига влево поступает очередной разряд множителя. Через 2п тактов произведение будет получено в регистре 6.

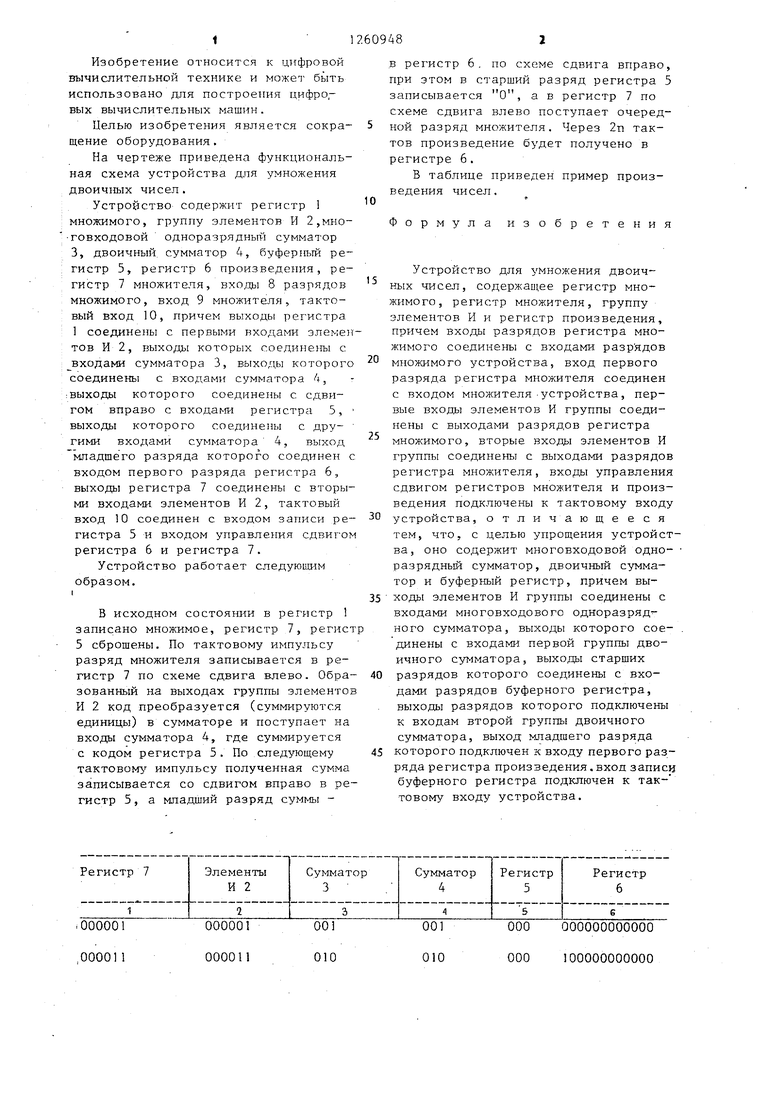

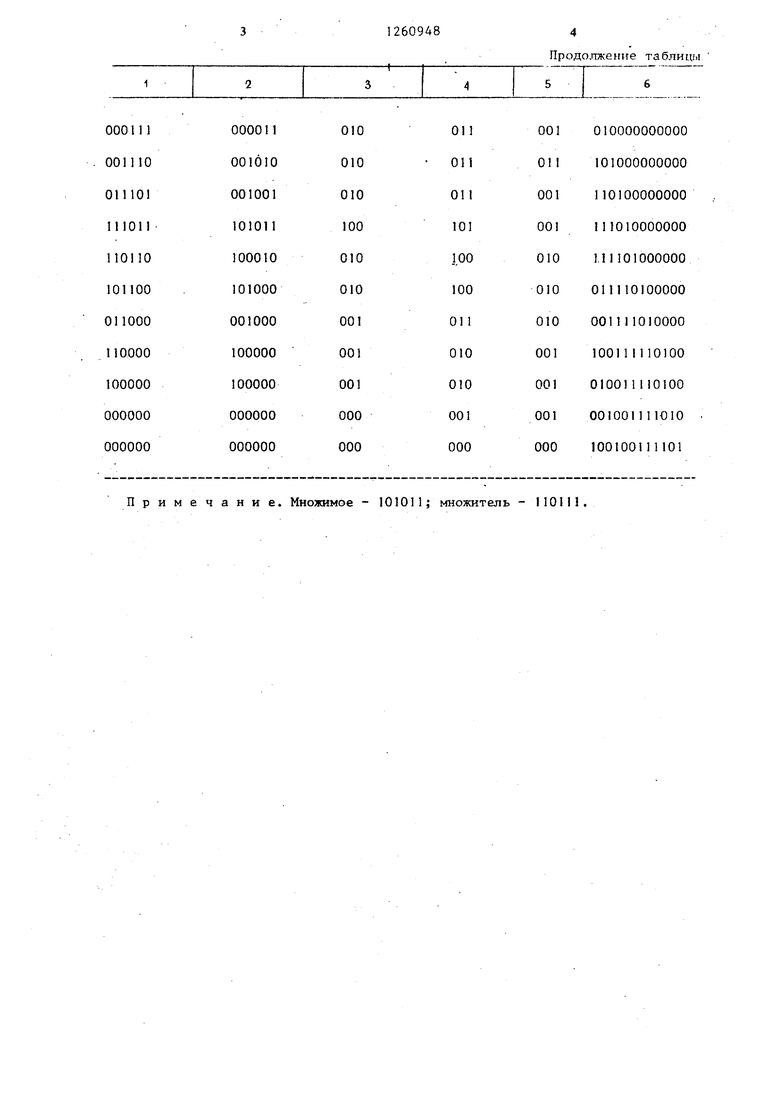

В таблице приведен пример произведения чисел.

Формула изобретения

Устройство для умножения двоичных чисел, содержацее регистр множимого, регистр множителя, группу элементов И и регистр произведения, причем входы разрядов регистра множимого соединены с входами разр ядов множимого устройства, вход первого разряда регистра множителя соединен с входом мнолштеля-устройства, первые входы элементов И группы соединены с выходами разрядов регистра множимого, вторые входы элементов И группы соединены с выходами разрядов регистра множителя, входы управления сдвигом регистров множителя и произведения подключены к тактовому входу устройства, о тличающе е ся тем, что, с целью упрощения устройства, оно содержит многовходовой одно- разрядный сумматор, двоичный сумматор и буферный регистр, причем выходы элементов И группы соединены с входами многовходового одноразряд ного сумматора, выходы которого сое- . динены с входами первой группы двоичного сумматора, выходы старших разрядов которого соединены с входами разрядов буферного регистра, выходы разрядов которого подключены к входам второй группы двоичного сумматора, выход младшего разряда которого подключен к входу первого разряда регистра произведения.вход записи буферного регистра подключен к так- товому входу устройства.

Примечание. Множимое - 101011; множитель - llOlli.

Продо.пжен11е таблицы

Редактор Т.Парфенова

Составитель А.Клюев,

Техред А.Кравчук Корректор Л.Пилипенко

Заказ 5232/49Тираж 671 Подписное

ВНИШ1И Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие,г.Ужгород,ул.Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения комплексных чисел | 1985 |

|

SU1283751A1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| Устройство для умножения | 1985 |

|

SU1254473A1 |

| Устройство для умножения | 1989 |

|

SU1672441A1 |

| Устройство для умножения | 1985 |

|

SU1305667A1 |

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

| Множительно-сдвиговое устройство | 1978 |

|

SU805307A1 |

| Устройство для умножения чисел | 1991 |

|

SU1797112A1 |

| Устройство для умножения | 1979 |

|

SU817701A1 |

| Устройство для умножения | 1981 |

|

SU1012245A1 |

Изобретение предназначено для умножения двоичных чисел разрядностью п и может быть использовано для построения цифровых вычислитель- ных машин . С целью сокращения оборудования при сохранении разрядности операндов устройство содержит регистр мнржимого, регистр множителя, регистр частных произведений, группу логических элементов И, регистр вспомогательный, комбинационный сумматор, преобразователь кода унитарного в двоичный, счетчик, дешифратор, генератор. Эффект сокращения оборудования достигается путем преобразования унитарного кода в двоичный. 1 ил., t табл. с (С (Л го О) о дЭ 4 (XI

| Гольденберг Л.М | |||

| Цифровые фильтры в электросвязи и радиотехнике | |||

| М.:Радио и связь, 1982, с | |||

| Транспортер для перевозки товарных вагонов по трамвайным путям | 1919 |

|

SU102A1 |

| Дроздов Е.А | |||

| и др | |||

| Электронные цифровые вычислительные машины (основы теории, принципы построения, элементы и устройства мапган) | |||

| М, 1968, с.406, рис | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| . | |||

Авторы

Даты

1986-09-30—Публикация

1985-03-18—Подача