Изобретение относится к вычислительной технике, в частности к устройствам для регистрации результатов испытаний программ в цифровы.с системах обработки данных.

Цель изобретения - повышение быстродействия устройства путем обеспечения возможности трассировки программ большого объема, регистрации последовательности выполнения команд в программах.

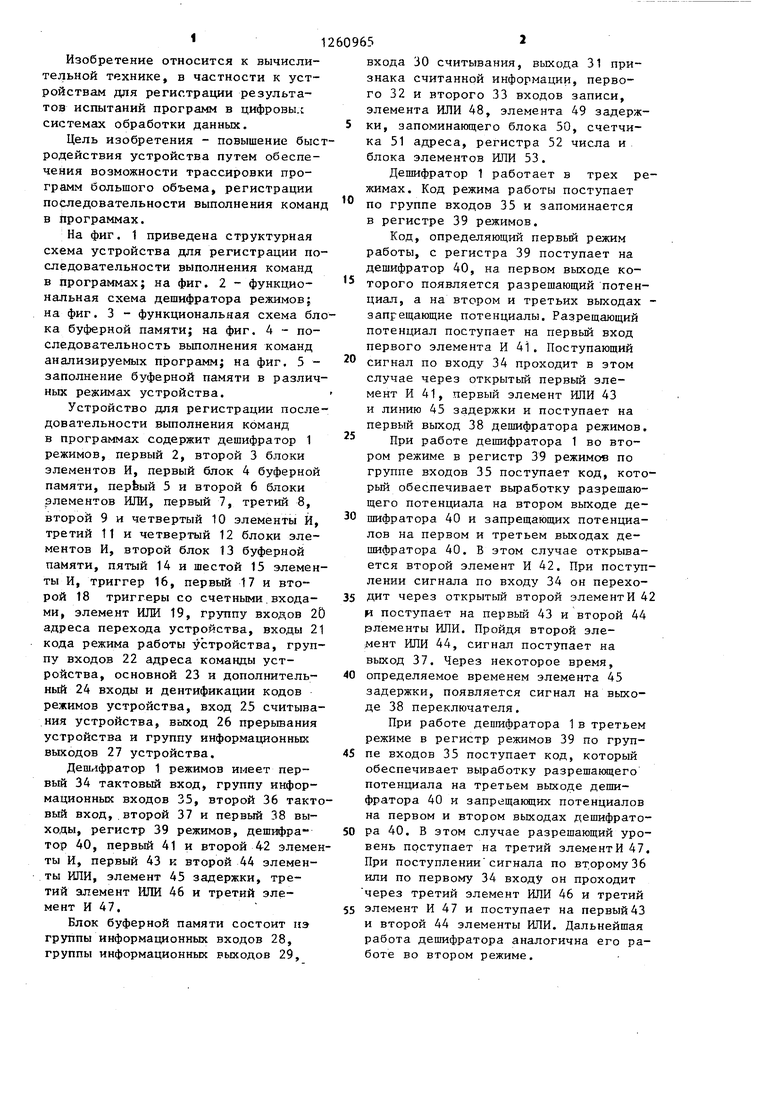

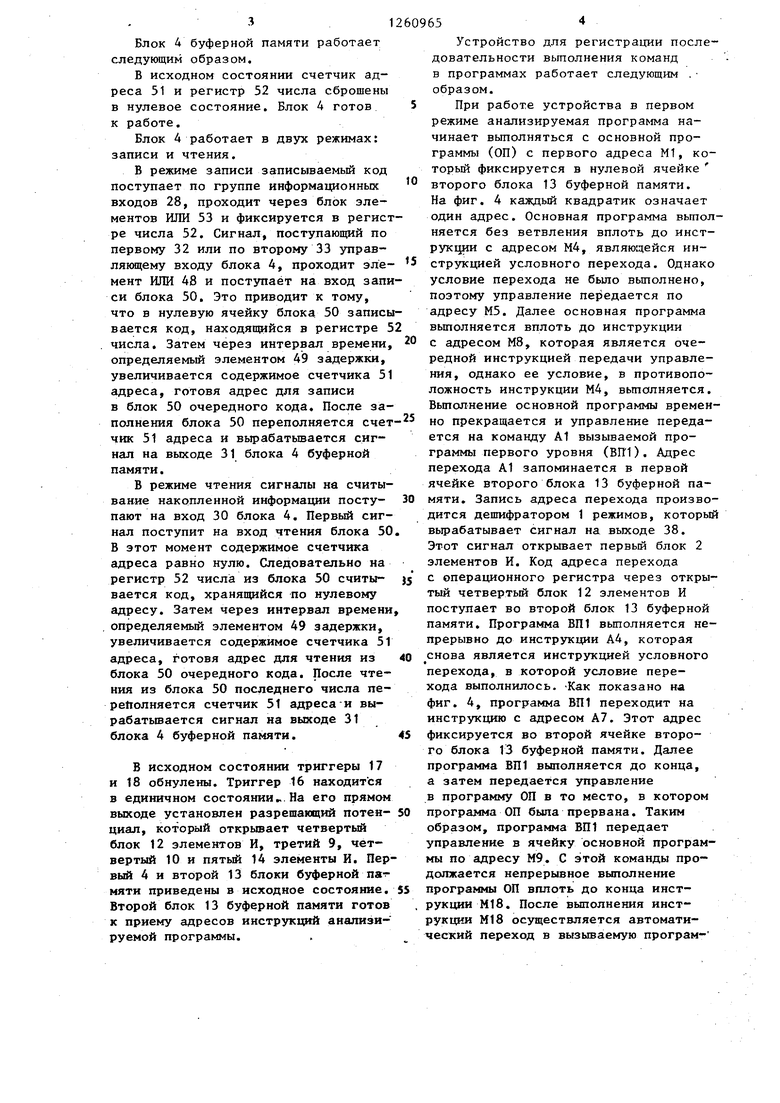

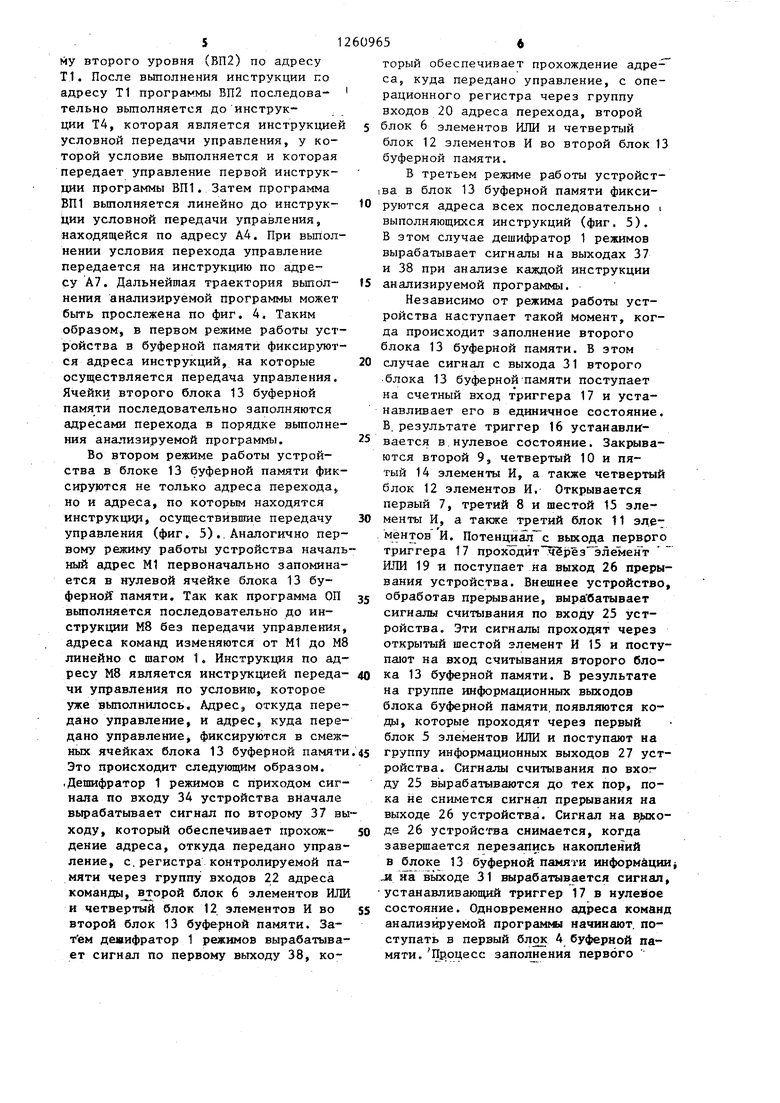

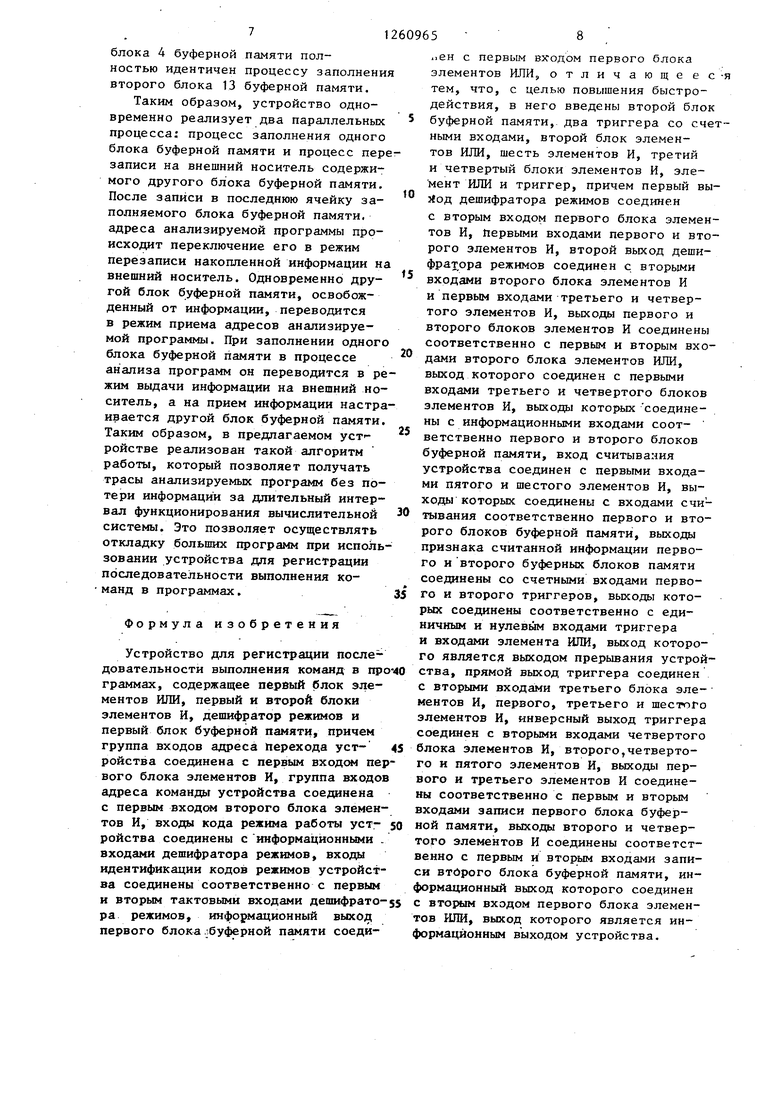

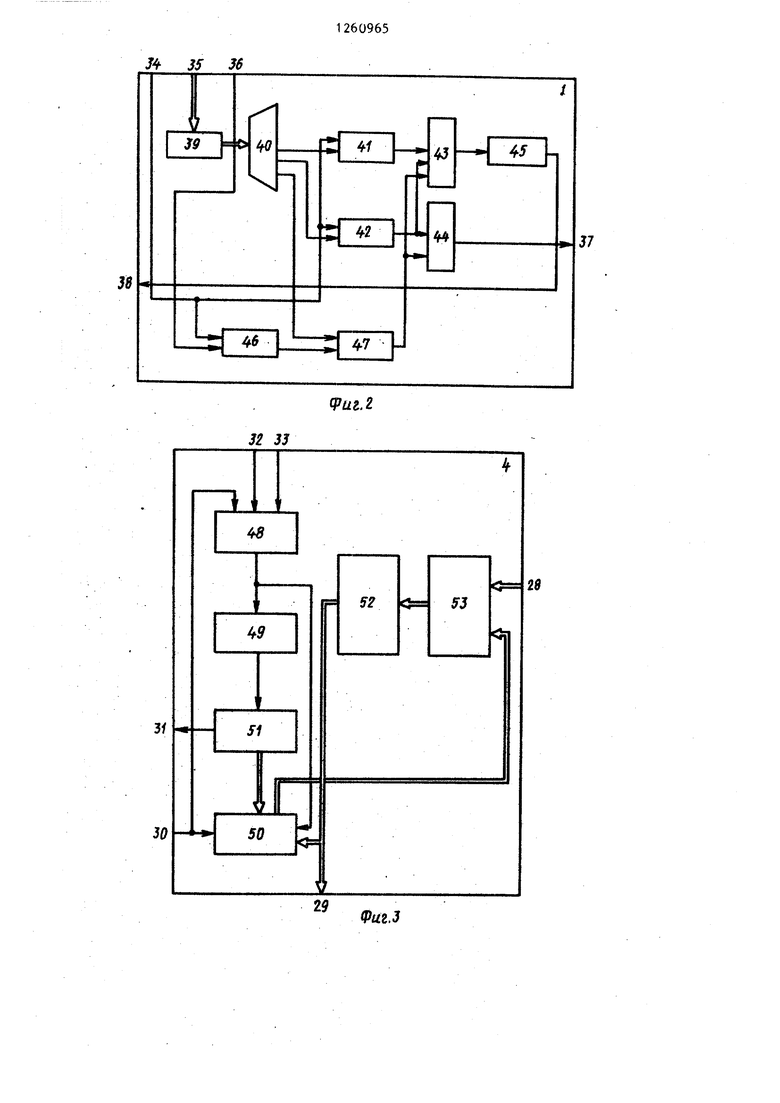

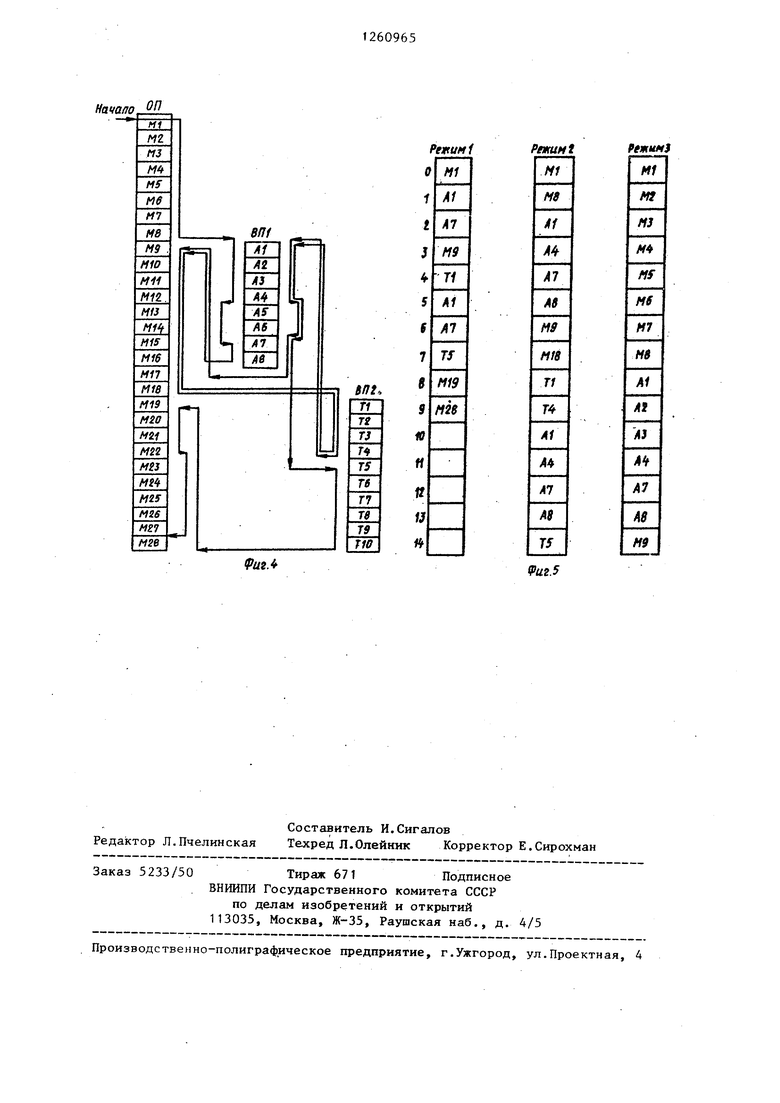

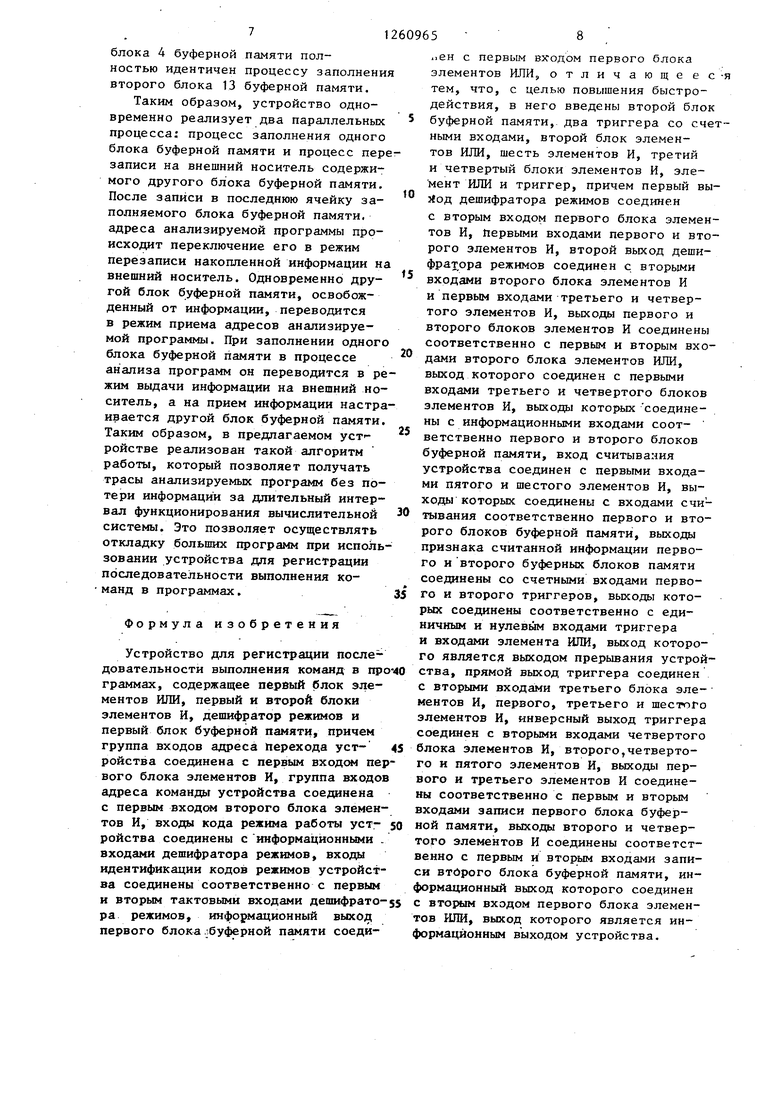

На фиг. 1 приведена структурная схема устройства для регистрации последовательности выполнения команд в программах; на фиг, 2 - функциональная схема дешифратора режимов; на фиг. 3 - функциональная схема блока буферной памяти; на фиг. 4 - последовательность вьшолнения команд анализируемых программ; на фиг. 5 - заполнение буферной памяти в различных режимах устройства.

Устройство для регистрации последовательности выполнения команд в программах содержит дешифратор 1 режимов, первый 2, второй 3 блоки элементов И, первый блок 4 буферной памяти, перЬый 5 и второй 6 блоки элементов ИЛИ, первый 7, третий 8, второй 9 и четвертый 10 элементы И, третий 11 и четвертый 12 блоки элементов И, второй блок 13 буферной памяти, пятый 14 и шестой 15 элементы И, триггер 16, первый 17 и второй 18 триггеры со счетными.входами, элемент ИЛИ 19, группу входов 25 адреса перехода устройства, входы 21 кода режима работы Устройства, группу входов 22 адреса команды устройства, основной 23 и дополнительный 24 входы и дентификации кодов режимов устройства, вход 25 считывания устройства, выход 26 прерьшания устройства и группу информационных выходов 27 устройства.

Дешифратор 1 режимов имеет первый 34 тактовый вход, группу информационных входов 35, второй 36 тактовый вход,.второй 37 и первый 38 выходы, регистр 39 режимов, дешифратор 40, первый 41 и второй 42 элементы И, первый 43 и второй 44 элементы ИЛИ, элемент 45 задержки, третий элемент ИЛИ 46 и третий элемент И 47,

Блок буферной памяти состоит иэ группы информационных входов 28, группы информационных выходов 29,

5

входа 30 считывания, выхода 31 признака считанной информации, первого 32 и второго 33 входов записи, элемента ИЛИ 48, элемента 49 задержки, запоминающего блока 50, счетчика 51 адреса, регистра 52 числа и блока элементов ИЛИ 53.

Дешифратор 1 работает в трех режимах. Код режима работы поступает по группе входов 35 и запоминается в регистре 39 режимов.

Код, определяющий первьй режим работы, с регистра 39 поступает на дешифратор 40, на первом выходе которого появляется разрешающий потенциал, а на втором и третьих выходах - запрещающие потенциалы. Разрещающий потенциал поступает на первьй вход первого элемента И 41. Поступающий сигнал по входу 34 проходит в этом случае через открытый первый элемент И 41, первый элемент ИЛИ 43 и линию 45 задержки и поступает на первый выход 38 дешифратора режимов. При работе дешифратора 1 во втором режиме в регистр 39 режимов по группе входов 35 поступает код, который обеспечивает выработку разрешающего потенциала на втором выходе дешифратора 40 и запрещающих потенциалов на первом и третьем выходах дешифратора 40. В этом случае открывается второй элемент И 42. При поступлении сигнала по входу 34 он перехо5 Дит через открытый второй элемент И 42 И поступает на первый 43 и второй 44 (элементы ИЛИ. Пройдя второй элемент ИЛИ 44, сигнал поступает на выход 37. Через некоторое время,

0 определяемое временем элемента 45 задержки, появляется сигнал на выходе 38 переключателя.

При работе дешифратора 1 в третьем режиме в регистр режимов 39 по груп5 пе входов 35 поступает код, который обеспечивает выработку разрешающего потенциала на третьем выходе дешифратора 40 и запрещающих потенциалов на первом и втором выходах дешифратора 40, В этом случае разрешающий уровень поступает на третий элемент И 47, При поступлении сигнала по вт.оромуЗб или по первому 34 входу он проходит через третий элемент ИЛИ 46 и третий элемент И 47 и поступает на первый43 и второй 44 элементы Ш1И. Дальнейшая работа дешифратора аналогична его работе во втором режиме.

0

0

5

to

20

Блок 4 буферной памяти работает следующим образом.

В исходном состоянии счетчик адреса 51 и регистр 52 числа сброшены в нулевое состояние. Блок 4 готов к работе.

Блок 4 работает в двух режимах: записи и чтения.

В режиме записи записываемьй код поступает по группе информационных входов 28, проходит через блок элементов ИЛИ 53 и фиксируется в регистре числа 52. Сигнал, поступающий по первому 32 или по второму 33 управляющему входу блока 4, проходит эле- 5 мент ИЛИ 48 и поступает на вход записи блока 50, Это приводит к тому, что в нулевую ячейку блока 50 записывается код, находящийся в регистре 52 числа. Затем через интервал времени, определяемый элементом 49 задержки, увеличивается содержимое счетчика 51 адреса, готовя адрес для записи в блок 50 очередного кода. После заполнения блока 50 переполняется счет чик 51 адреса и вьфабатываатся сигнал на выходе 31 блока 4 буферной памяти.

В режиме чтения сигналы на считывание накопленной информации поступают на вход 30 блока 4. Первый сигнал поступит на вход чтения блока 50. В этот момент содержимое счетчика адреса равно нулю. Следовательно на регистр 52 числ;а из блока 50 считы- J5 вается код, хранящийся по нулевому адресу. Затем через интервал времени, определяемый элементом 49 задержки, увеличивается содержимое счетчика 51 адреса, готовя адрес для чтения из блока 50 очередного кода. После чтения из блока 50 последнего числа переполняется счетчик 51 адреса-и вырабатывается сигнал на выходе 31 блока 4 буферной памяти.

30

40

45

В исходном состоянии триггеры 17 и 18 обнулены. Триггер 16 находится в единичном состоянии.,. На его прямом выходе установлен разрещающий потен- циал, который открывает четвертый блок 12 элементов И, третий 9, четвертый 10 и пятый 14 элементы И. Первый 4 и второй 13 блоки буферной мяти приведены в исходное состояние. Второй блок 13 буферной памяти готов к приему адресов инструкций анализи- руемой программы.

to

20

52

. J5

25

50 SS

2609654

Устройство для регистрации последовательности вьтолнения команд в программах работает следующим . образом.

При работе устройства в первом режиме анализируемая программа начинает вьтолняться с основной программы (СП) с первого адреса Ml, который фиксируется в нулевой ячейке второго блока 13 буферной памяти. На фиг. 4 каждый квадратик означает один адрес. Основная программа выполняется без ветвления вплоть до инструкции с ащресом М4, являющейся инструкцией условного перехода. Однако условие перехода не было вьтолнено, поэтому управление передается по адресу М5. Далее основная программа вьтолняется вплоть до инструкции с адресом М8, которая является очередной инструкцией передачи управления, однако ее условие, в противоположность инструкции М4, выполняется. Выполнение основной программы временно прекращается и управление передается на команду А1 вызываемой программы первого уровня (ЕП). Адрес перехода А1 запоминается в первой ячейке второго блока 13 буферной памяти. Запись адреса перехода производится дешифратором 1 режимов, который вырабатывает сигнал на выходе 38. Этот сигнал открывает первый блок 2 элементов И. Код адреса перехода с операционного регистра через открытый четвертый блок 12 элементов И поступает во второй блок 13 буферной памяти. Программа ВП1 вьшолняется непрерывно до инструкции А4, которая снова является инструкцией условного перехода, в которой условие перехода выполнилось. Как показано на фиг. 4, программа ВП1 переходит на инструкцию с адресом А7. Этот адрес фиксируется во второй ячейке второго блока 13 буферной памяти. Далее программа ВП1 выполняется до конца, а затем передается управление в программу ОП в то место, в котором программа ОП была прервана. Таким образом, программа ВП1 передает управление в ячейку основной программы по адресу М9. С этой команды продолжается непрерывное выполнение программы ОП вплоть до конца инструкции Ml 8. После выполнения инструкции Ml 8 осуществляется автоматический переход в вызываемую програм30

40

45

му второго уровня (ВП2) по адресу Т1. После вьшолнения инструкции по адресу Т1 программы ВП2 последова- тельно вьтолняется до инструкции Т4, которая является инструкцией условной передачи управления, у которой условие вьтолняется и которая передает управление первой инструк- даи программы ВП1. Затем программа ВП1 вьтолняется линейно до инструк- ции условной передачи управления, находящейся по адресу А4. При выполнении условия перехода управление передается на инструкцию по адресу А7. Дальнейшая траектория вьшол- нения анализируемой программы может быть прослежена по фиг. Д. Таким образом, в первом режиме работы устройства в буферной памяти фиксируются адреса инструкций, на которые осуществляется передача управления. Ячейки второго блока 13 буферной памяти последовательно заполняются адресами перехода в порядке вьшолне- ния анализируемой программы.

Во втором режиме работы устройства в блоке 13 буферной памяти фиксируются не только адреса перехода, но и адреса, по которым находятся инструкццр, осуществившие передачу упраеления (фиг. 5).. Аналогично первому режиму работы устройства начальный адрес Ml первоначально запоминается в нулевой ячейке блока 13 буферной памяти. Так как программа ОП вьтолняется последовательно до инструкции М8 без передачи управления, адреса команд изменяются от Ml до М8 линейно с шагом 1, Инструк1щя по адресу М8 является инструкцией переда- чи управления по условию, которое уже выполнилось. Адрес, откуда передано управление, и адрес, куда передано управление, фиксируются в смежных ячейках блока 13 буферной памяти Это происходит следующим образом. .Дешифратор 1 режимов с приходом сигнала по входу 34 устройства вначале вырабатывает сигнал по второму 37 выходу, который обеспечивает прохож- дение адреса, откуда передано управление, с.регистра контролируемой памяти через группу входов 22 адреса команды, второй блок 6 элементов ИЛИ и четвертый блок 12 элементов И во второй блок 13 буферной памяти. За- т ем дешифратор 1 режимов вырабатывает сигнал по первому выходу 38, который обеспечивает прохождение адре- са, куда передано управление, с операционного регистра через группу входов 20 адреса перехода, второй блок 6 элементов ИЛИ и четвертый блок 12 элементов И во второй блок 13 буферной памяти.

В третьем режиме работы устройст- 1ва в блок 13 буферной памяти фиксируются адреса всех последовательно i выполняющихся инструкций (фиг, 5). В этом случае дешифратор 1 режимов вырабатывает сигналы на выходах 37 и 38 при анализе каждой инструкции анализируемой программы.

Независимо от режима работы устройства наступает такой момент, когда происходит заполнение второго блока 13 буферной памяти. В этом случае сигнал с выхода 31 второго блока 13 буферной памяти поступает на счетный вход триггера 17 и устанавливает его в единичное состояние. В. результате триггер 16 устанавливается в.нулевое состояние. Закрываются второй 9, четвертый 10 и пятый 14 элементы И, а также четвертый блок 12 элементов И. Открывается первый 7, третий 8 и шестой 15 элементы И, а таюке третий блок 11 эде- ментов И. Потенциал с выхода первого триггера 17 прохЪдйт л1герез элемен т ИЛИ 19 и поступает на выход 26 прерывания устройства. Внешнее устройство обработав прерывание, выра батывает сигналы считывания по входу 25 устройства. Эти сигналы проходят через открытый шестой элемент И 15 и поступают на вход считывания второго блока 13 буферной памяти. В результате на группе информационных выходов блока буферной памяти, появляются коды, которые проходят через первый блок 5 элементов ИЛИ и поступают на группу информационных выходов 27 устройства. Сигналы считывания по входу 25 вырабатываются до тех пор, пока не снимется сигнал прерывания на выходе 26 устройства. Сигнал на в;лсо де 26 устройства снимается, когда завершается перезапись накоплений в блоке 13 буферной памяти информаци JS на вьпсоде 31 вырабатывается сигнал устанавливающий триггер 17 в нулевое состояние. Одновременно адреса коман анализируемой пpoгpaм вlI начинают, поступать в первый блок 4 буферной памяти. Процесс заполнения первого

to

ts

71260965

блока 4 буферной памяти полностью идентичен процессу заполнения второго блока 13 буферной памяти.

Таким образом, устройство одновременно реализует два параллельных процесса; процесс заполнения одного блока буферной памяти и процесс перезаписи на внешний носитель содержимого другого блока буферной памяти. После записи в последнюю ячейку заполняемого блока буферной памяти, адреса анализируемой программы происходит переключение его в режим перезаписи накопленной информации на внешний носитель. Одновременно другой блок буферной памяти, освобожденный от информации, переводится в режим приема адресов анализируемой программы. При заполнении одного блока буферной памяти в процессе анализа программ он переводится в режим выдачи информации на внешний носитель, а на прием информации настраивается другой блок буферной памяти. Таким образом, в предлагаемом уст-- ройстве реализован такой алгоритм работы, который позволяет получать трасы анализируемых программ без потери информации за длительный интервал функционирования вычислительной системы. Это позволяет осуществлять откладку больших программ при использовании устройства дпя регистрации последовательности выполнения ко- манд в программах.

20

25

30

35

э т н т и м Я

с то вх и то вт со да вы вх эл ны ве бу ус ми хо ты ро пр го со го ры ни и го ст с ме эл со бл го во ны вх но то ве си фо

Формула изобретения

Устройство для регистрации последовательности выполнения команд в про-40 граммах, содержащее первый блок элементов ИЛИ, первый и второй блоки элементов И, дешифратор режимов и первый блок буферной памяти причем группа входов адреса перехода уст- 45 ройства соединена с первым входом первого блока элементов И, группа входов адреса команды устройства соединена с первым входе второго блока элементов И, входы кода режима работы уст- 50 ройства соединены с информационными . входами дешифратора режимов, входы идентификации кодов режимов устройства соединены соответственно с первым

и вторым тактовыми входами дешифрато-55 с вторым входом первого блока элеменра режимов, информационный выхо( первого блока . буферной памяти соеди8ен с первым входом первого блока

to

s

0

5

0

5

0 5 0

элементов ИЛИ, отличающеес-я тем, что, с целью повышения быстродействия, в него введены второй блок буферной памяти, два триггера со счетными входами, второй блок элементов ИЛИ, шесть элементов И, третий и четвертый блоки элементов И, эле- мент ИЛИ и триггер, причем первый вы- Яод дешифратора режимов соединен

с вторым входом первого блока элементов И, Первыми входами первого и второго элементов И, второй выход дешифратора режимов соединен с вторыми входами второго блока элементов И и первым входами третьего и четвертого элементов И, выходы первого и второго блоков элементов И соединены соответственно с первым и вторым входами второго блока элементов РШИ, выход которого соединен с первыми входами третьего и четвертого блоков элементов И, выходы которых соединены с информационными входами соответственно первого и второго блоков буферной памяти, вход считывания устройства соединен с первыми входами пятого и шестого элементов И, выходы которых соединены с входами считывания соответственно первого и второго блоков буферной памяти, выходы признака считанной информации первого и второго буферных блоков памяти соединены со счетными входами первого и второго триггеров, выходы которых соединены соответственно с единичным и нулевым входами триггера и входами элемента ИЛИ, выход которого является выходом прерывания устройства, прямой выход триггера соединен с вторыми входами третьего блока элементов И, первого, третьего и шестого элементов И, инверсный выход триггера соединен с вторыми входами четвертого блока элементов И, второго,четвертого и пятого элементов И, выходы первого и третьего элементов И соединены соответственно с первым и вторым входами записи первого блока буферной памяти, выходы второго и четвертого элементов И соединены соответственно с первым И входами записи второго блока буферной памяти, информационный выход которого соединен

тов РШИ, выход которого является информационным выходом устройства.

J4 35 36

Фаг, 2

Jf л

1

3f

Jf

JO

50

29

52

55

Фиг.З

Havaffo,.L

1риг.

Редактор Л.Пчелинская

Составитель И.Сигалов

Техред Л.Олейник Корректор Е.Сирохман

Заказ 5233/50Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Режим 1

POKUMt

femuM)

til

Ml

MS

Mi

Л1

H3

M

H

A7

Mf

A8

Мб

Mff

H7

M18

MB

T1

A1

Г4

A

xr

A3

«4

Alt

X7

AJ

A9

M

Tf

H9

.5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1981 |

|

SU980096A1 |

| Устройство для отладки программ | 1985 |

|

SU1348840A1 |

| Устройство управления конвейерным вычислительным устройством | 1991 |

|

SU1751757A1 |

| УСТРОЙСТВО ДЛЯ ОТЛАДКИ ПРОГРАММ | 1991 |

|

RU2049349C1 |

| Мультипрограммное вычислительное устройство | 1990 |

|

SU1777147A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

| Устройство для обработки данных | 1980 |

|

SU896625A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для обработки информации датчиков | 1980 |

|

SU955093A1 |

Изобретение относится к вычислительной технике, в частности к устройствам для регистрации результатов испытаний программ в цифровых системах обработки данных. Целью изобретения является повышение быстродействия устройства. Устройство содержит дешифратор режимов 1, четыре блока 2, 3, 11, 12 элементов И, два блока 4, 13 буферной памяти, два блока 5, 6 элементов ИЛИ, шесть элементов 7 - 10, 14, 15 И, триггер 16, два триггера 17, 18 со счетными входами, элемент 19 ИЛИ. 5 ил. I (Л N9 Од СО Од сл г.1 а

| Патент Англии № 1436428, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

| Фарадисов В.А | |||

| и др | |||

| Комплекс аппаратных средств ЭВМ для отладки программ реального времени | |||

| - Управляющие системы и машины, 1980, № 1., с | |||

| Способ смешанной растительной и животной проклейки бумаги | 1922 |

|

SU49A1 |

| Устройство для оценки профессиональной пригодности операторов АСУ | 1987 |

|

SU1441444A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

Авторы

Даты

1986-09-30—Публикация

1983-02-17—Подача