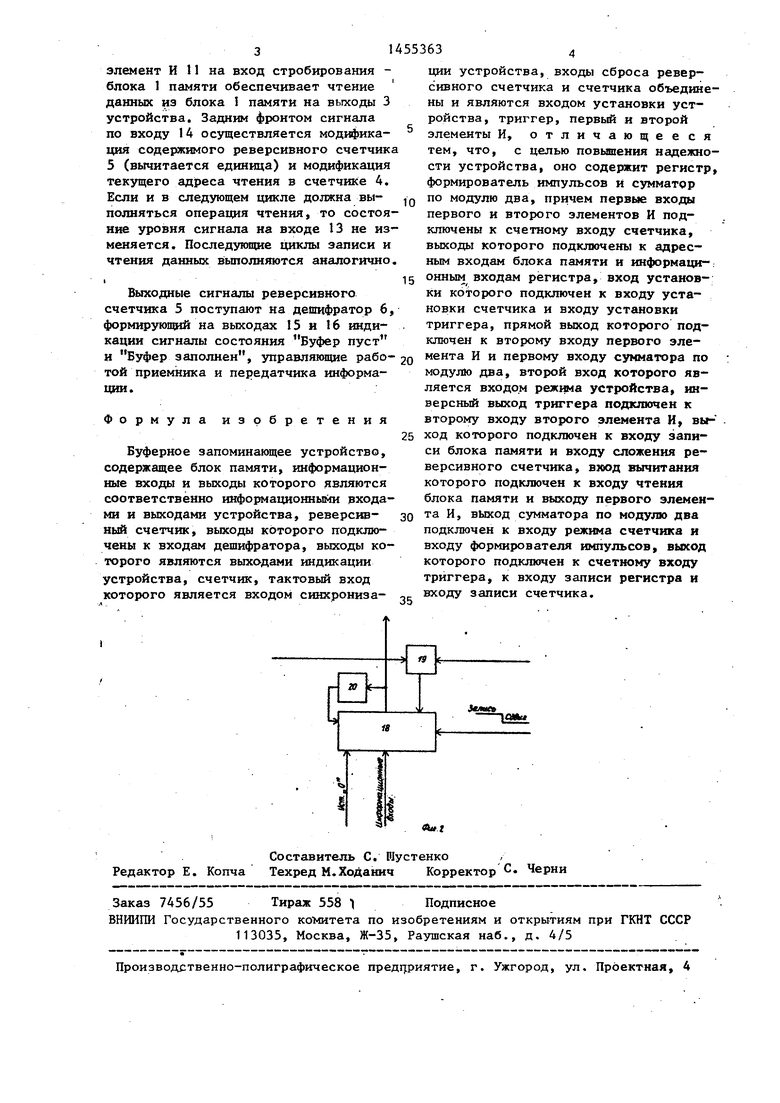

ta смены сигнала по входу 13 на вре- 45 Ч чтения данных из блока 1 памяти, Мя, достаточно равное для срабатыва- уровень сигнала на входе 13 меняется Ния триггера 8 по счетному входу, на высокий. При этом появляется высо- сумматора 9 по модулю два, формирова- кий уровень сигнала на выходе суммато- геля 10.

Если в момент поступления низкого уровня сигнала по входу 13 триггер 8 находится в единичном состоянии, г.е. в счетчике 4 хранится текущий адрес чтения, то на выходе сумматора 0 по модулю два появляется высокий уровень сигнала, по которому форми50

55

ра 9 по модулю два, по которому формируется импульс формирователе 10 и переписывается содержимое регистра 7 в счетчик 4, а содержимое счетчика 4 в регистр 7 и изменяется на противоположное состояние триггера 8„ Этим осуществляется подключение к адресным входам блока 1 памяти текущего адреса чтения. Поступающийс задержкой относительно смены уровня сигнала на входе 13 сигнал по входу 14 через

рователь 10 сформирует импульс, переписывающий содержимое регистра 7 1а счетчик 4, а содержимое счетчика

Ч чтения данных из блока 1 памяти, уровень сигнала на входе 13 меняется на высокий. При этом появляется высо- кий уровень сигнала на выходе суммато-

ра 9 по модулю два, по которому формируется импульс формирователе 10 и переписывается содержимое регистра 7 в счетчик 4, а содержимое счетчика 4 в регистр 7 и изменяется на противоположное состояние триггера 8„ Этим осуществляется подключение к адресным входам блока 1 памяти текущего адреса чтения. Поступающийс задержкой относительно смены уровня сигнала на входе 13 сигнал по входу 14 через

элемент И 11 на вход стробирования - блока 1 памяти обеспечивает чтение данных из блока 1 памяти на выходы 3 устройства. Задним фронтом сигнала по входу 14 осуществляется модификация содержимого реверсивного счетчика 5 (вычитается единица) и модификация текущего адреса чтения в счетчике 4. Если и в следующем цикле должна выполняться операция чтения, то состояние уровня сигнала на входе 13 не изменяется. Последующие циклы записи и чтения данных выполняются аналогично.

I

Выходные сигналы реверсивного счетчика 5 поступают на дешифратор 6, формирующий на выходах 5 и 16 индикации сигналы состояния Буфер пуст

ции устройства, входы сброса реверсивного счетчика и счетчика объединены и являются входом установки устройства, триггер, первый и второй элементы И, отличающееся тем, что, с целью повышения надежности устройства, оно содержит регистр формирователь импульсов и сумматор

IQ по модулю два, причем первые входы первого и второго элементов И подключены к счетному входу счетчика, выходы которого подключены к адресным входам блока памяти и информаци15 онным входам регистра, вход установки которого подключен к входу установки счетчика и входу установки триггера, прямой выход которого подключен к второму входу первого элеи Буфер заполнен, управляющие рабо- 2о мента И и первому входу сумматора по той приемника и передатчика информации.

Формула изобретения

модулю два, второй вход которого является входом режима устройства, инверсный выход триггера подключен к второму входу второго элемента И, выход которого подключен к входу записи блока памяти и входу сложения реверсивного счетчика, вход вычитания которого подключен к входу чтения блока памяти и выходу первого элемента И, выход сумматора по модулю два подключен к входу режима счетчика и входу формирователя импульсов, выход которого подключен к счетному входу триггера, к входу записи регистра и входу записи счетчика.

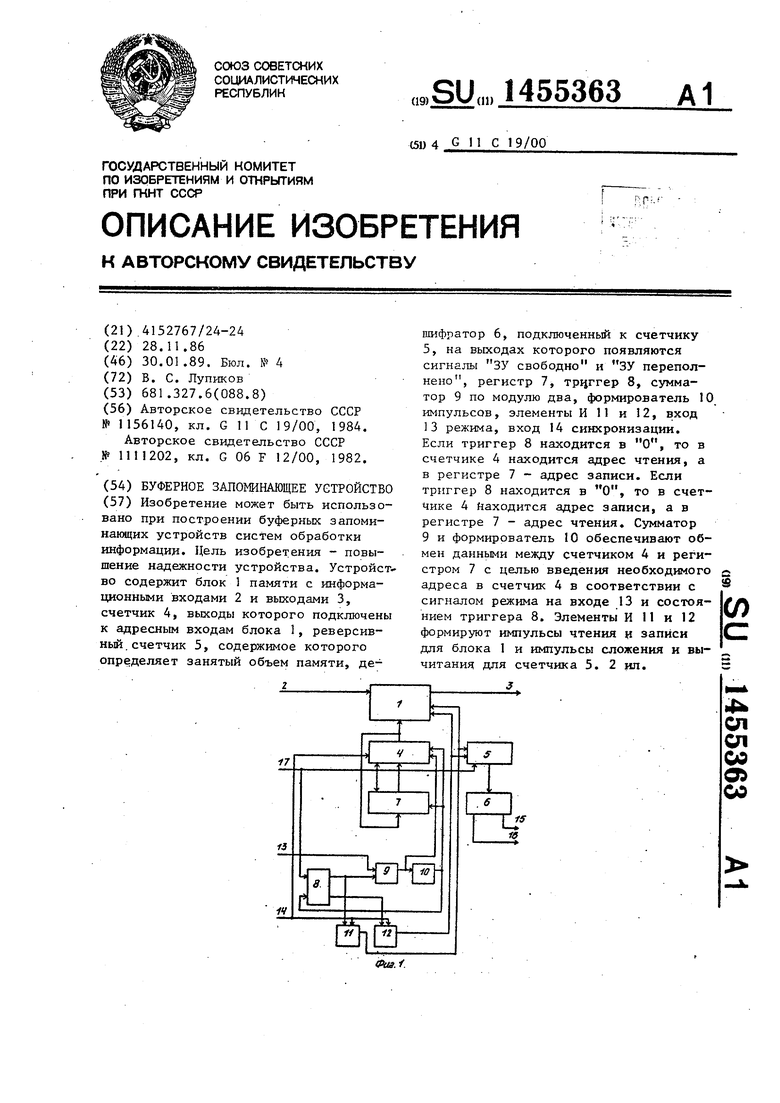

Буферное запоминающее устройство, содержащее блок памяти, информационные входы и выходы которого являются соответственио информационными входами и выходами устройства, реверсив- ный счетчик, выходы которого подключены к входам дешифратора, выходы которого являются выходами индикации устройства, счетчик, тактовый вход которого является входом синхрониза-

ции устройства, входы сброса реверсивного счетчика и счетчика объединены и являются входом установки устройства, триггер, первый и второй элементы И, отличающееся тем, что, с целью повышения надежности устройства, оно содержит регистр, формирователь импульсов и сумматор

по модулю два, причем первые входы первого и второго элементов И подключены к счетному входу счетчика, выходы которого подключены к адресным входам блока памяти и информационным входам регистра, вход установки которого подключен к входу установки счетчика и входу установки триггера, прямой выход которого подключен к второму входу первого элемента И и первому входу сумматора по

модулю два, второй вход которого является входом режима устройства, инверсный выход триггера подключен к второму входу второго элемента И, вы ход которого подключен к входу записи блока памяти и входу сложения реверсивного счетчика, вход вычитания которого подключен к входу чтения блока памяти и выходу первого элемента И, выход сумматора по модулю два подключен к входу режима счетчика и входу формирователя импульсов, выход которого подключен к счетному входу триггера, к входу записи регистра и входу записи счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

| Устройство для имитации информационных каналов | 1986 |

|

SU1386996A1 |

| Сигнатурный анализатор | 1986 |

|

SU1357961A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1261010A1 |

| Устройство для ввода информации | 1986 |

|

SU1363225A2 |

| Устройство для ввода информации | 1987 |

|

SU1442999A2 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439618A1 |

| Многоканальное устройство ввода информации | 1985 |

|

SU1273936A2 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

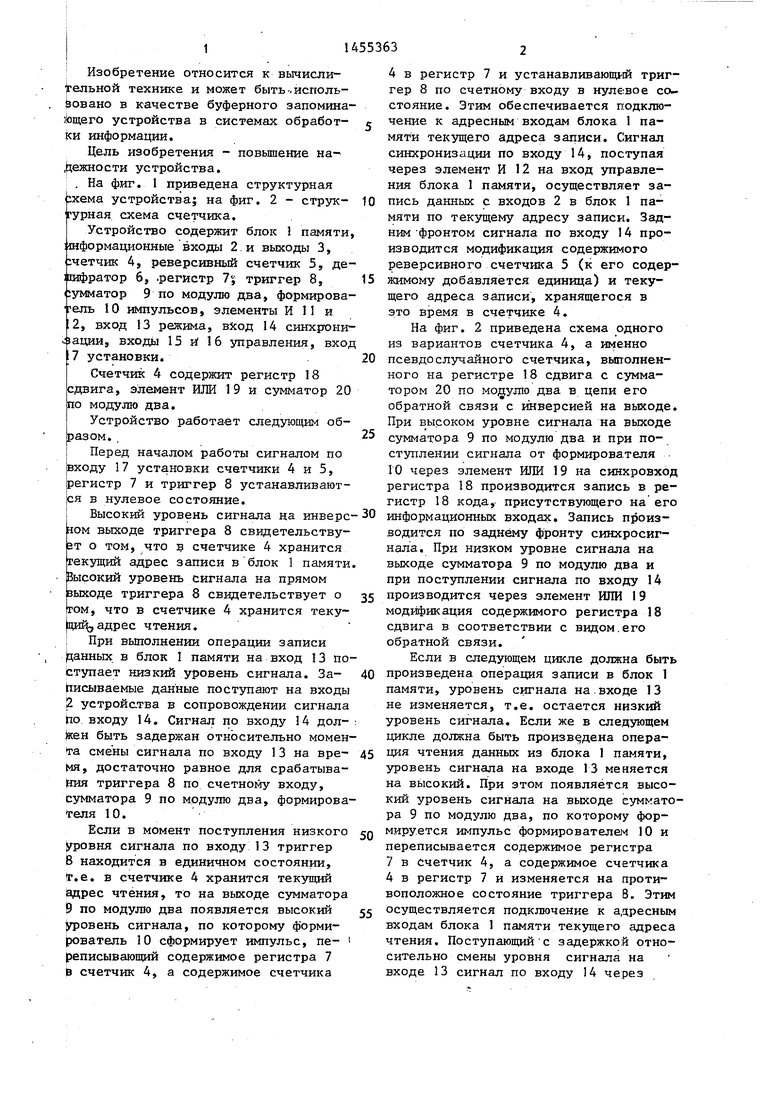

Изобретение может быть использовано при построении буферных запоминающих устройств систем обработки информации. Цель изобретения - повышение надежности устройства. Устройств во содержит блок 1 памяти с информационными входами 2 и выходами 3, счетчик 4, выходы которого подключены к адресным входам блока 1, реверсив- ньй.счетчик 5, содержимое которого определяет занятый объем памяти, дешифратор 6, подключенный к счетчику 5, на выходах которого появляются сигналы ЗУ свободно и ЗУ переполнено, регистр 7, триггер 8, сумматор 9 по модулю два, формирователь 10 импульсов, элементы И 11 и 12, вход 13 режима, вход 14 синхронизации. Если триггер 8 находится в О, то в счетчике 4 находится адрес чтения, а в регистре 7 - адрес записи. Если триггер 8 находится в О, то в счетчике 4 Находится адрес записи, а в регистре 7 - адрес чтения. Сумматор 9 и формирователь 10 обеспечивают обмен данными между счетчиком 4 и регистром 7 с целью введения необходимого адреса в счетчик 4 в соответствии с сигналом режима на входе 13 и состоянием триггера 8. Элементы И 11 и 12 формируют импульсы чтения и записи для блока 1 и импульсы сложения и вычитания для счетчика 5. 2 ил. (Л

Сю е- .«

| Буферное запоминающее устройство | 1984 |

|

SU1156140A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1111202A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-01-30—Публикация

1986-11-28—Подача