Изобретение относится к вычисли тельной технике и может быть исполь зовано при построении буферных запоминающих устройств каналов и уст ройств обмена. Известно буферное запоминающее устройство, содержащее блок памяти, блок формирования адреса и блок анализа степени заполнения объема Однако данное устройство обладает малой надежностью из-за возможности получения недостоверной информации. Наиболее близким к изобретению является буферное запоминающее устройство, содержсцдее накопитель,регистр числа, счетчики адресов записи и чтения, дешифратор, счетчик объема и блок управления 2. Недостатком этого .устройства является отсутствие контроля функциони рования управляющих схем, в частности счетчиков адресов записи и чтения и счетчика объема, что снижа ет надежность работы устройства. Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем что в устрюйство дополнительно введе мы сумматор, схема сравнения и блок анализа состояния накопителя, причем входы сумматора подключены к выходам счетчика адреса чтения и счетчика объема накопителя, а выход - к схеме сравнения, второй вход которой соединен со счетчиком адреса записи, первый вход блока анализа состояния накопителя подключен к блоку управления, а второй, третий и четвертый являются выходами схемы сравнения; блок анализа состояния накопителя содержит четыре логических элемента И, два инвертора и логический элемент ИЛИ, причем первые входы первого и второго логических элементов И подключены к первому входу блока анализа состояния накопителя, а первые входы третьего и четвертого логических элементов И соединены с выходом первого инвертора, вход которого подключен к первому входу блока анализа состояния накопителя, вторые входы логических элементов И. подключены к выходу второго инвертора, вход которого подключен ко второму входу блока анализа состояния накопителя,третьи входы первого и третьего элементов И соединены с третьим входом блока анализа состояния накопителя, третьи входы второго и четвертого элеентов И подключены к четвертому вхоу блока анализа состояния накопитея, выход первого логического элеента И соединен с первым вьлходом лока анализа состояния накопителя, ыход четвертого элемента И соединен о вторым.выходом блока анализа сотояния накопителя, а выходы второго третьего элементов И подключены к соответствующим входам элемента ИЛИ, выход которого является третьим выходом блока анализа состояния накопителя.

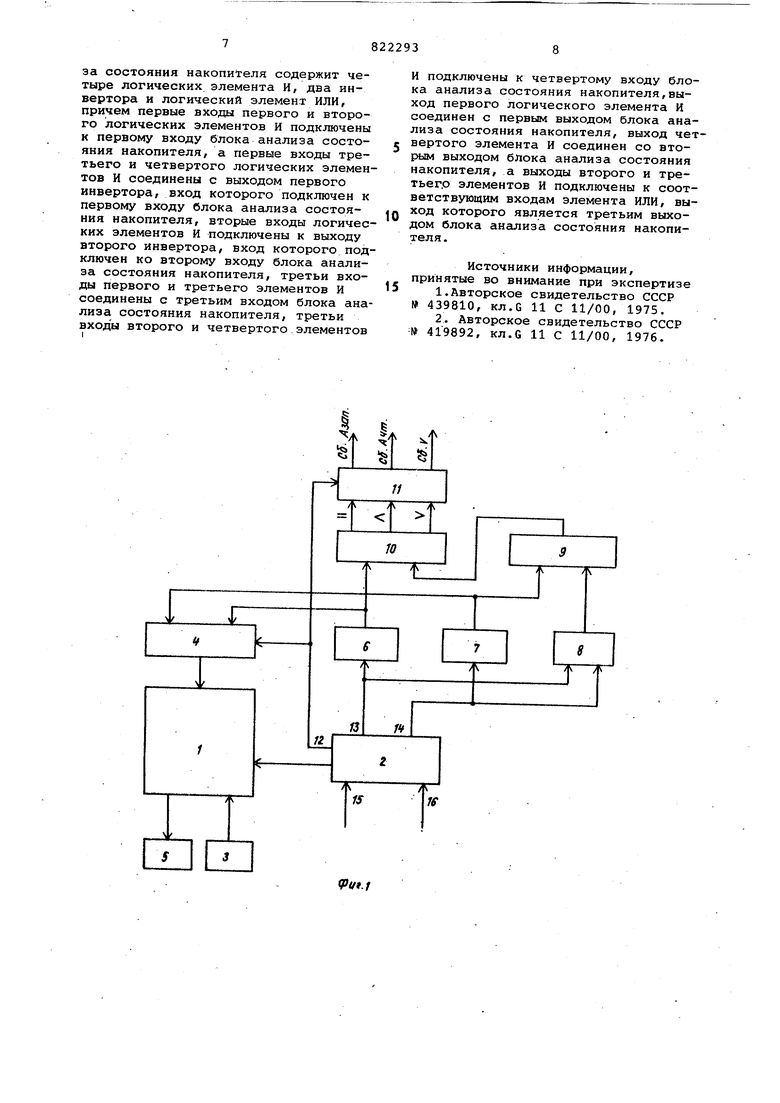

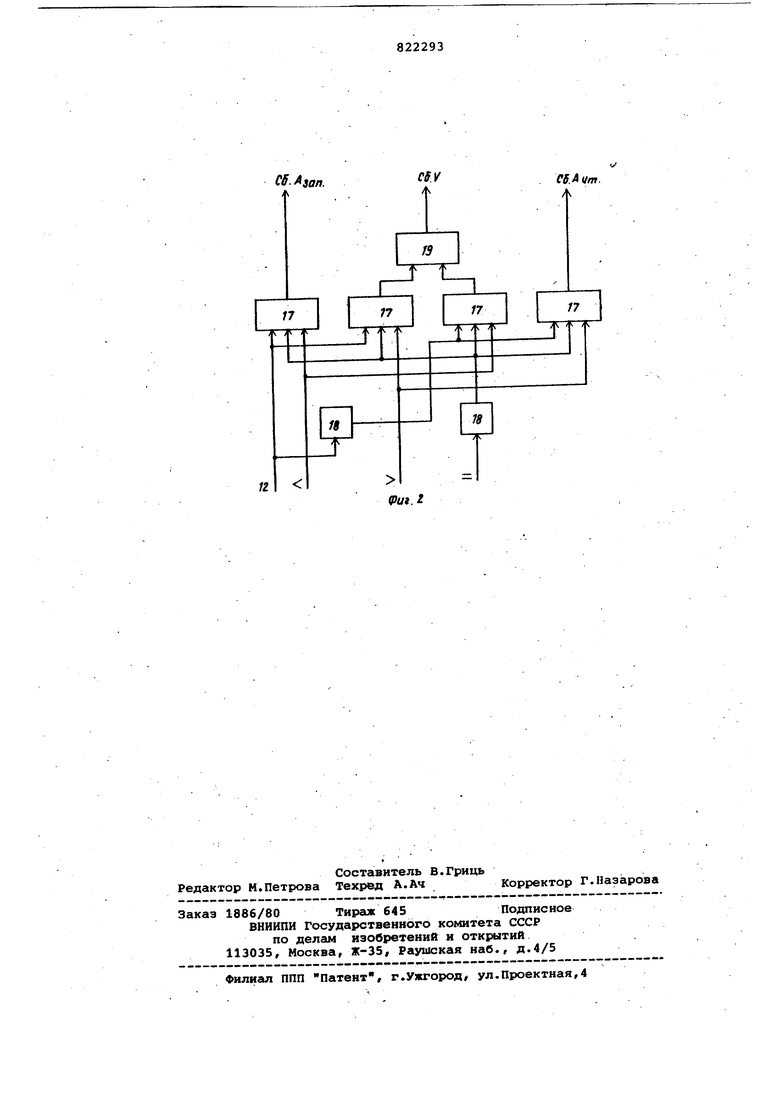

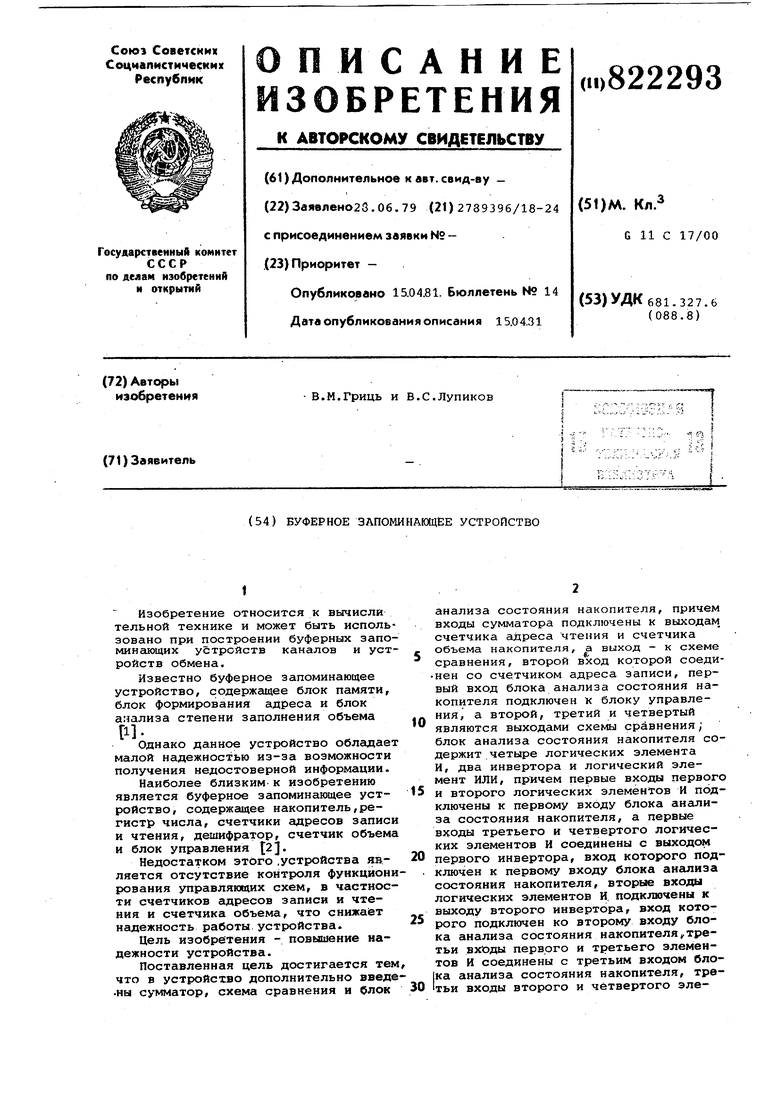

На фиг.1 изббражена структурная схема буферного запоминающего устройства; на фиг.2 - структурная схема блока анализа состояния накопителя.

Буферное запоминающее устройство содержит накопитель 1, входы которого подключены к одному из выходов блока 2 управления, выходу входного регистра 3 числа и выходу элементов 4 И-ИЛИ по числу разрядов в адресе, выход накопителя 1 подключен к входу выходного регистра 5 числа, входы элементов 4 И-ИЛИ подключены к в1ыходам счетчика 6 адреса записи и счетчика 7 адреса чтения, входы которых подключены к соответствующим выходам блока 2 управления и входам счетчика 8 объема накопителя. Выходы счетчика 7 адреса чтения и счетчика 8 объема накопителя подключены к соответствующим входам сумматора 9, выход которого соединен со входом схемы 10 сравнения, другой вход которой подключен к выходу счетчика 6 адреса записи. Первый вход блока 11 анализа состояния -накопителя через шину 12 признака операции (Пр.Оп. соединен с блоком 2 управления и другим входом элементов 4 И-ИЛИ, а второй, третий и четвертый входы блока 11 анализа состояния накопителя яв-ляются выходами схемы 10 сравнения. Блок 2 управления соединен с входом счетчика 6 адреса записи и первым (суммирующим) входом счетчика 8 объема накопителя шиной 13 модификации адреса записи, а шина 14 модификации адреса чтения подключает к блоку 2 управления вход счетчика 7 адреса чтения и второй (вычитающий) вход счетчика 8 объема накопителя. Входы блока 2 управления соединены с шиной 15 запроса записи и с шиной 16 запроса чтения соответственно.Блок 11 анализа состояния накопителя содержит четыре логических элемента 17 И, два инвертора 18 и логический элемент 19 ИЛИ, причем первые входы первого и второго логических элементов 17 И подключены к первому входу блока 11 анализа состояния накопителя, а первые входы третьего и четвертого логических элемента 17 И соединены с выходом первого инвертора 18, вход которого подключён к

первому входу блока 11 анализа состояния накопителя. Вторые входы логических элементов 17 И подключены к выходу второго инвертора 18,вход которого подключен ко второму входу блока /11 анализа состояния накопителя, третьи входы первого и третьего элементов 17 И соединены с третьим входом блока 11 анализа состояния накопителя, третьи входы второго и четвертого элементов 17 И подключены к четвертому входу блока 11 анализу состояния накопителя. Выход первого логического элемента 17 И соединен с первым выходом блока 11 анализа состояния накопителя, выход четвертого элемента 17 И соединен со вторым выходом блока 11 а.нализа состояния накопителя, а выходы- второго и третьего элементов 17 И подключены к соответствующим входам элемента 19 ИЛИ, выход которого является третьим выходом блока 11 анализа состояния накопителя.Причем второй, третий, и четвертый входы блока 11 анализа состояния накопителя соответственно подключены к выходам равно, меньше, больше схемы 10 сравнения.

Устройство работает следующим образом.

W. При выполнении операции записи данных (наличие сигнала на шине 15 запроса записи) блок 2 управления через элементы 4 И-ИЛИ подключает к адресным входам накопителя 1 выходы счетчика 6 адреса записи и осуществляет запись данных из входного регистра 3 числа в накопитель 1. По окончании записи блок 2 управления

0 по шине 13 модификации адреса записи увеличивает, на единицу содержимое счетчика 6 адреса записи и счетчика 8 объема накопителя. При выполнении операции чтения данных (наличие сигнала на шине 16 запроса чтения) блок 2 управления через элементы 4 И-ИЛИ подключает к адресным входам накопителя 1 выходы счетчика 7 ещраса чтения и осуществляет запись в выходной регистр 5 числа данных, считанных из накопителя 1. По окончании чтения блок 2 управления по шине 14 модификации адреса чтения увеличивает на единицу содержимое счетчика 7 адреса чтения и уменьшает на единицу содержимое счетчика 8 объема накопителя.

Повышение надежности, устройства осуществляется ведением постоянного контроля за выполнением равенства Аэст- Чт+ V(1)

Q где AjQ - содержимое счетчика б адреса записи;

А - содержимое счетчика 7 адреса чтения;

V - содержимое счетчика 8 обт i5ема накопителя. По окончании операции записи (чтения) блок 11 анализа состояния накопителя анализирует правильность выполнения модификации содержимого счетчика 6 адреса записи, счетчика 7 адреса ч:тения и счетчика 8 объема накопителя и, в случае сбоя, локали зует место неисправности. Для этого сумматор 9 суммирует с держимое счетчика 7 адреса чтения и счетчика В объема накопителя. Полученная сумма поступает на один из входов схемы 10 сравнения, где она сравнивается с содержимым счетчика 6 адреса записи. Сх«ма 10 сравнения формирует сигналы равно, больше и меньше. Сигнал равно выдается при условии выполнения равенства (1 Возникновение сигнала равно свиде тельствует о правильной работе контролируемых счетчиков и, воздействуя на второй инвертор 18 блока 11 анализа состояния накопителя, блокирует срабатывание логических элементов 17 И. Сигнал меньше формируется, если А А„, -f- V эап чт а сигнал больше вырабатывается, если (3) Формирование сигналов больше или меньше свидетельствует о сбоях контролируемых счетчиков. Блок 11 анализа состояния накопителя формирует сигнал сбоя счетчика б адреса записи Сб.Адцп, если при выполнении операции записи (Пр.Оп.1, т.е. при единичном уровне на шине 12 признака операции) схема 10 сравнения выдгша сигнал меньше, т.е. )np.On рав«о При этом на первом и третьем входах блока 11 анализа .состояния накопителя присутствуют единичные уровни сиг налов, а на его втором и четвертом входах - нулевые уровни сигналов, ко торые, воздействуя на входы первого логического элемента 17 И, вызовут появления на его выходе сигнгша Сб.Аза„. Аналогично сигнал сбоя счетчика 7 адреса чтения при выполнении операци чтения (Пр.Оп, 0) формируется блоком 11 анешиза состояния накопителя, если содержимое счетчика 6 адреса «эа писи больше выходной суммы сумматора 9. т.е. . рр-Оп.- .тПри этом на всех входах, за исклю четвертого , блока 11 анализа состояния накопителя присутствует (5) нулевой уровень сигналов. Эта комбинация сигналов, воздействуя на входы четвертого логического элемента 17 И, вызывает появление на его выходе сигнала Сб.Ац. Сбой счетчика 8 объема накопителя фиксируется, если при выполнении операции записи выполняется неравенство (3) или при выполнении операции чтения выполняется неравенство (2), т. е. ( 4Nan.A fjnpon.l При этом на первом и четвертом входах или же на третьем входе блока 11 анализа состояния накопителя будут присутствовать единичные уровни сигналов, которые, воздействуя соответственно на второй или третий логические элементы 17 И, вызовут появление на их выходах, а .следовательно, и на выходе логического элемента 19 ИЛИ сигнала C6.V. Таким образом значительно повышаются показатели надежности устройст.ва за счет сокращения времени поиска и локализации неисправности. Если же выполнение равенства (1) нарушается в результате одиночного сбоя, то наличие информации о месте возникновения сбоя позволяет.принять необходимые меры для устранения ошибок, возникающих в результате сбоя. Формула изобретения 1. Буферное запоминающее устройство, содержащее накопитель, входы которого подключены к одному из выходов блока управления, выходу входного регистра числа и выходу элемента И-ИЛИ, выход накопителя подключен к входу выходного регистра числа, входы элемента И-ИЛИ подключены к выходам счетчиков адреса записи и чтения, входы которых подключены к соответствующим выходам блока управления и вход счетчика объема накопителя, отличающееся тем, что, с целью повышения надежности устройства, оно содержит сумматор, схему сравнения и блок ансшиза состояния накопителя, причем входы сумматора подключены к выходам счетчика гщреса чтения и счетчика объема накопителя, а выход - к схеме сравнения, второй вход которой соединен со счетчиком адреса записи, первый вход блока анализа состояния накопителя одключен к блоку управления, а второй, третий и четвертый являются выходами схемы сравнения. 2. Устройство по П.1, от л и ающееся тем, что блок ангшиза состояния накопителя содержит четыре логических элемента И, два инвертора и логический элемент ИЛИ, причем первые входы первого и второго логических элементов И подключены к первому входу блока анализа состояния накопителя, а первые входы третьего и четвертого логических элементов И соединены с выходом первого инвертора, вход которого подключен к первому входу блока анализа состояния накопителя, вторые входы логических элементов И подключены к выходу второго инвертора, вход которого подключен ко второму входу блока анализа состояния накопителя, третьи входы первого и третьего элементов И соединены с третьим входом блока анализа состояния накопителя, третьи входы второго и четвертого элементов

И подключены к четвертому входу блока анализа состояния накопителя,выход первого логического элемента И соединен с первым выходом блока анализа состояния накопителя, выход четвертого элемента И соединен со вторым выходом блока анализа состояния накопителя, а выходы второго и третьегр элементов И подключены к соответствующим входам элемента ИЛИ, выход которого является третьим выходом блока анализа состояния накопителя.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 439810, кл.С 11 С 11/00, 1975.

2. Авторское свидетельство СССР I 419892, кл.С 11 С 11/00, 1976.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1987 |

|

SU1495851A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1297115A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1278979A2 |

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1381530A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1444893A1 |

| Устройство для цифровой магнитной записи | 1989 |

|

SU1647634A2 |

| Буферное запоминающее устройство | 1985 |

|

SU1261012A1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Буферное запоминающее устройство | 1981 |

|

SU982095A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1124379A1 |

iJLl

I .

/ VМ/

CS.A

зап.

К

CdV

СВ. A If т.

i

rf Ь.

Авторы

Даты

1981-04-15—Публикация

1979-06-28—Подача