to

Од

ю

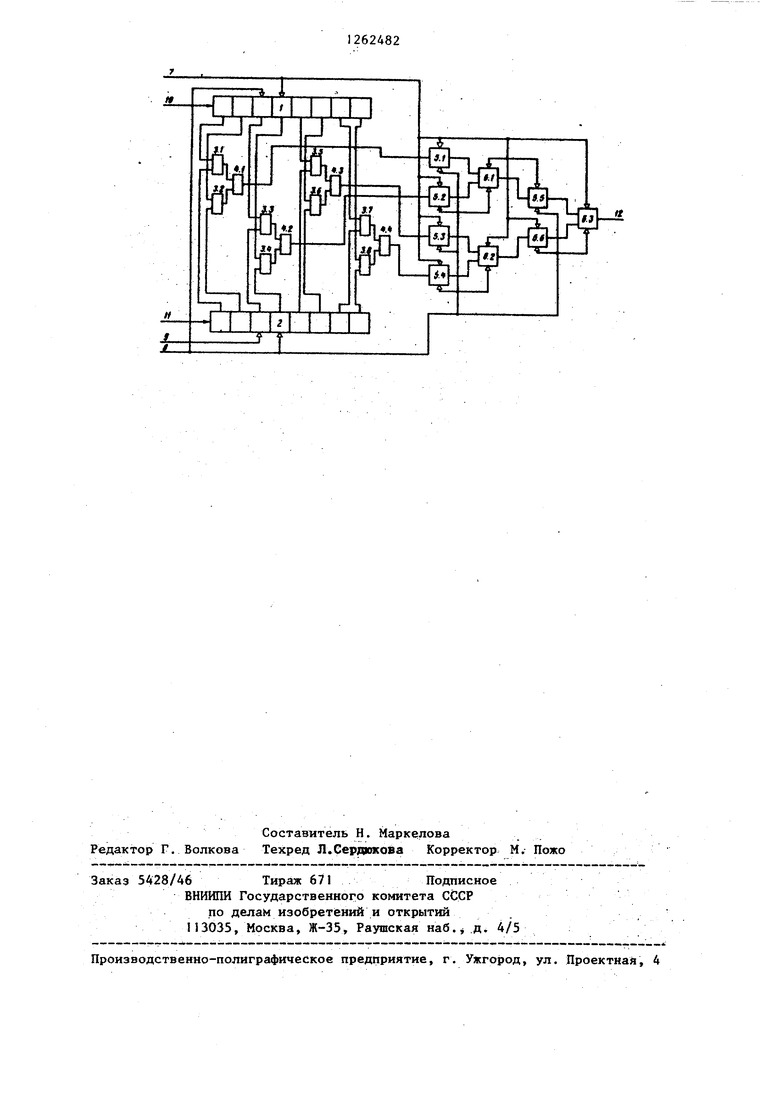

U 00 1ч9 Изобретение относится к вычислительной технике и может быть исполь зовано при построении цифровых вычи лительных машин последовательного действия. Цель изобретения - упрощение уст ройства. На чертеже представлена функциональная схема восьмиразрядного посл довательного устройства для умножения. Устройство содержит динамический регистр 1 множимого, статический ре гистр 2 последовательного приближения множителя, восемь элементов И 3,1-3.8, четыре элемента ИЛИ 4.14.4, шесть триггеров 5.1-5.6, три последовательных сумматора 6.1-6.3, первый установочный вход 7, тактирующий вход 8 устройства, второй установочный вход 9, вход 10 множим го устройства, вход II множителя ус ройства, выход 12 устройства. Код золотой пропорции из множе ства всех возможных форм представления одного и того же числа имеет одну форму, в которой после каждой единицы может быть не менее одного нуля, т.е. минимальную форму представления 12. Два соседних разряда множителя, представленного в-коде золотой пр порции, не могут одновременно равняться единице, т.е. Q, где а,-аь. i+1 раз i-ro и - значения 1 141 рядов кода множителя На выходе i-ro элемента И получается частичное произведение П| i-ro разряда кода множителя .на посл довательньп код множимого . В, где В - последовательный код множим На выходе j-ro элемента ИЛИ формируется частичное произведение IIj ri.a2,.,BVa,jj-B. Результат умножения получается п сложении сумматорами последовательных кодов частичных произведений П 1-2 П г: П;, J-1 где п - разрядность кода множителя Рассмотрим работу последовательн го устроства для умножения на приме умножения двух кодов золотой пропор ции с разрядностью кодов множимого и множителя равной восьми: код множ теля А 01001001; код множимого В 10110010. Нулевой потенциал с первого установочного входа 7 поступает на входы обнуления динамического регистра 1 множимого, триггеров 5.1-5.6 и последовательных сумматоров 6.1-6.3 и устанавливает их в нулевое состояние. Одновременно нулевой потенциал с второго установочного входа 9 поступает на вход начальной установки статического регистра 2 последовательного приближения множителя и положительный перепад с тактирующего входа 8 устройства поступает на входы синхронизации динамического регистра 1 множимого, статического регистра 2 последовательного приближения множителя, триггеров 5.1-5.6, последовательных сумматоров 6.1-6.3 и устанавливает регистр 2 последовательного приближения множителя в начальное состояние. С приходом второго положительного перепада на тактирующий вход 8 устройства (при этом на первом установочном входе 7 и втором установочном .) входе 9 присутствуют потенциалы логической единицы) в первый разряд динамического регистра 1 множимого записывается старщий разряд кода множимого, в нащем примере записывается единица, а в первый разряд статического регистра 2 последовательного приближения множителя записывается старший разряд кода множителя, в нашем примере записывается ноль, в триггера 5.1-5.6 и последовательные сумматоры 6.1-6.3 записываются нули. С приходом третьего положительного перепада на тактирующий вход 8 устройства содержимое динамического регистра I множителя сдвигается на один разряд вправо, а в первый его разряд записывается значение второго. разряда кода множимого, в нашем примере записывается ноль, во второй разряд статического регистра 2 последовательного приближения множителя записывается значение второго разряда кода множителя, в нашем примере записывается единица, в триггера 5.1-5.6 и последовательные сумматоры записываются нули, при этом на выходе элементов И 3.2 и ИЛИ 4.I формируется единичный потенциал. С приходом четвертого положительного перепада на тактирующий вход 8 устройства содержимое динамического регистра 1 множимого сдвигается на один разряд вправо, а в первый его разряд записывается значение третье го разряда кода множимого, в нашем примере записывается единица, в третий разряд статического регистра 2 последовательного приближения множителя записывается значение третьего разряда кода множителя, в нашем примере записывается ноль, в триггер 5.1 записывается единица, в триггера 5.2-5.6 и последовательные сумматоры записываются нули. С приходом пятого положительного перепада на тактирующий вход 8 устройства содержимое динамического регистра 1 множимого сдвигается на один разряд вправо, в первый его раз ряд записывается значение четвертого разряда кода множимого, в нашем примере записывается единица, в четвертый разряд статического регистра 2 последовательного приближения множителя записывается значение четвертог разряда кода множителя, в нашем примере записывается ноль, в триггера 5.1-5.6 записываются нули, в последо вательный сумматор 6.1 записывается единица, в последовательные сумммато ры 6.2 и 6,3 записываются нули, на выходах элементов И 3.2 и ИЛИ 4.1 формируется единичный потенциал. Формула, изобретения Последовательное устройство для умножения, содержащее динамический регистр множимого, статический регистр последовательного приближения множителя, п-элементов И, где п разрядность множителя, р - последовательных сумматоров, где 1 р п, причем информационный вход динамичес кого регистра множимого соединен с входом множимого устройства, информационный вход статического регистра последовательного приближения множи(теля соединен с входом множителя уст ройства, входы синхронизации динамического регистра множимого и статического регистра последовательного 2 4 приближения множителя соединены с тактирующим входом устройства, первые входы элементов И соединены с выходами соответствующих разрядов динамического регистра множимого, вторые входы элементов И соединены с выходами соответствующих разрядов статического регистра последовательного приближения множителя, о т л ичающееся тем, что, с целью его упрощения, оно содержит п/2 элементов ИЛИ, 2р-триггеров, причем рпоследовательных сумматоров и 2ртриггеров разбиты на К-групп, где K 1log2(n/2), где Ц - округление до большего целого,1-е группы последо1:ательных сумматоров и триггеров содержат соответственно М,; сумматоров и 2 Мг-триггеров, где I, , - число последовательных сумматоров (1-1)- и групЬы, число последовательных сумматоров первой групМ равно п/4, , первые и вторые входы j-ro элемента ИЛИ соединены соответственно с выходами (2j-l)-ro и 2j-ro элементов И, выход j-ro элемента ИЛИ соединен с информационным входом j-ro триггера первой группы,информационные входы i-ro последовательного сумматора 1-ой группы соединены соответственно с выходами 2i-ro и (21-1)-го триггера 1-й группы, информационные входы триггеров 1-й группы соединены с выходами последовательных сумматоров (1-1)-и группы, входы синхронизации последовательных сумматоров соединены с входами синхронизации Триггеров и тактирующим входом устройства, входы обнуления динамического регистра множимого соединены с входами обнуления триггеров, с входами обиуления последовательных сумматоров и соединены с первьтм установочным входом устройства, вход начальной установки статического регистра последовательного приближения множителя соединен с вторым установочным входом устройства, выход последовательного сумматора К-ой группы является выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательное устройство для умножения | 1987 |

|

SU1444754A1 |

| Устройство для умножения целых чисел в р-кодах Фибоначчи | 1986 |

|

SU1345190A1 |

| Устройство для умножения | 1989 |

|

SU1612295A1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1117655A1 |

| Последовательное множительное устройство | 1981 |

|

SU987620A1 |

| Устройство для умножения двоичных чисел | 1988 |

|

SU1587498A1 |

| Устройство для умножения двоичных чисел | 1990 |

|

SU1711152A1 |

| Последовательное множительное устройство | 1980 |

|

SU888110A1 |

| Устройство для умножения | 1985 |

|

SU1254473A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

Изобретеиие отиосится к вычислительной технике и может быть использовано для умножения последовательных кодов золдтой пропорции, поступающих старшими разрядами вперед. Цель изобретения - упрощение устройства. Это достигается путем представления кода множителя минимальной формой, одновременного умножения на два разряда кода множителя и получеиия результата умножения старшими разрядами вперед. Производится умножение п-разрядиого кода множителя, представленного в минимальной форме, g на код множимого произвольной разряд(Л ности, представленного как в минимальной , так и в иемишшальиой форс мах. I ил.

| Последовательное множительное устройство | 1981 |

|

SU987620A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Стахов А.П | |||

| Коды золотой пропорции | |||

| - М.: Радио и связь, 1984 | |||

| Дроздов Е.А | |||

| и Пятибратов А.П | |||

| Основания устройства электронных цифровых вычислительных машин | |||

| - М., 1959, с | |||

| 336-338, рис | |||

| Переносный кухонный очаг | 1919 |

|

SU180A1 |

Авторы

Даты

1986-10-07—Публикация

1985-03-01—Подача