ФигЛ

Изобретение относится к вычисли- тельной технике и может быть исноль- зовано для выполнения арифметических действий.

Цель изобретения - сокращение ан- наратурных затрат.

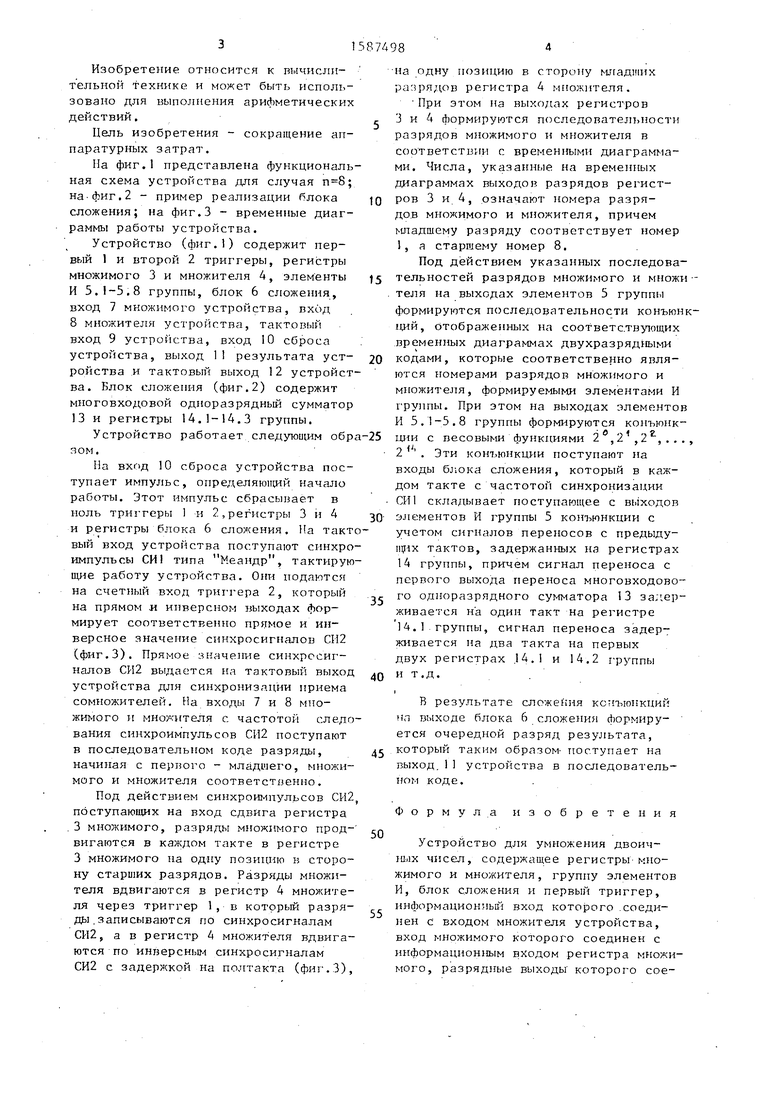

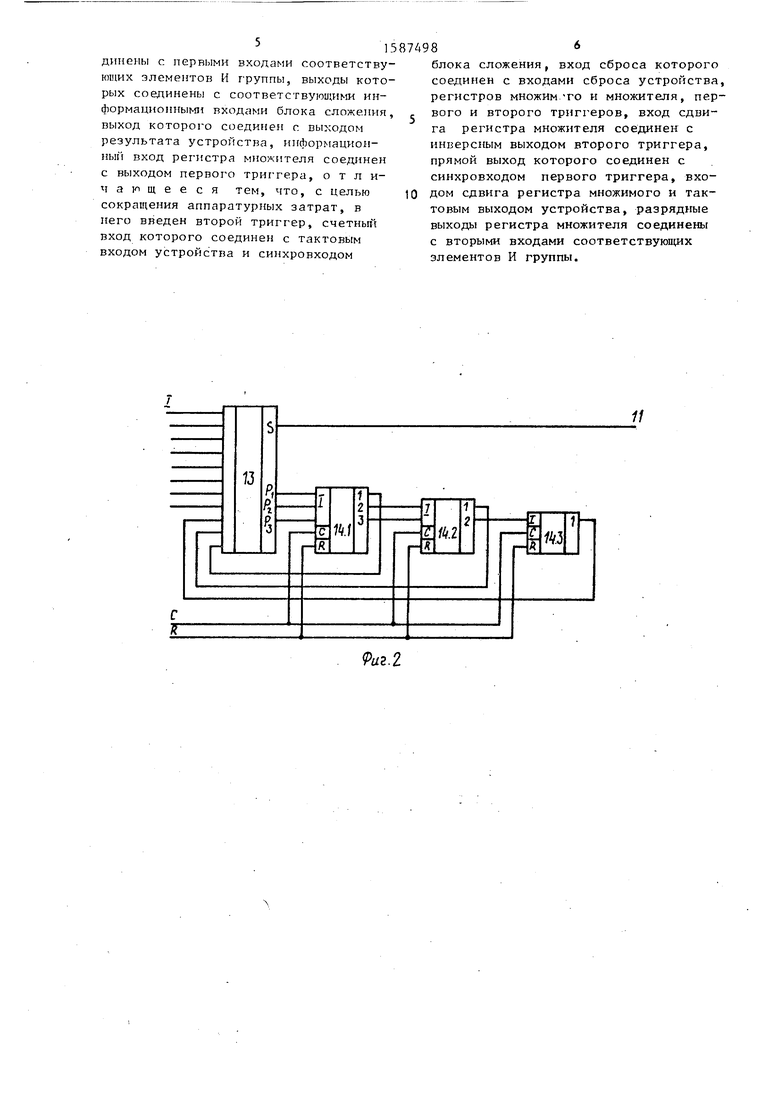

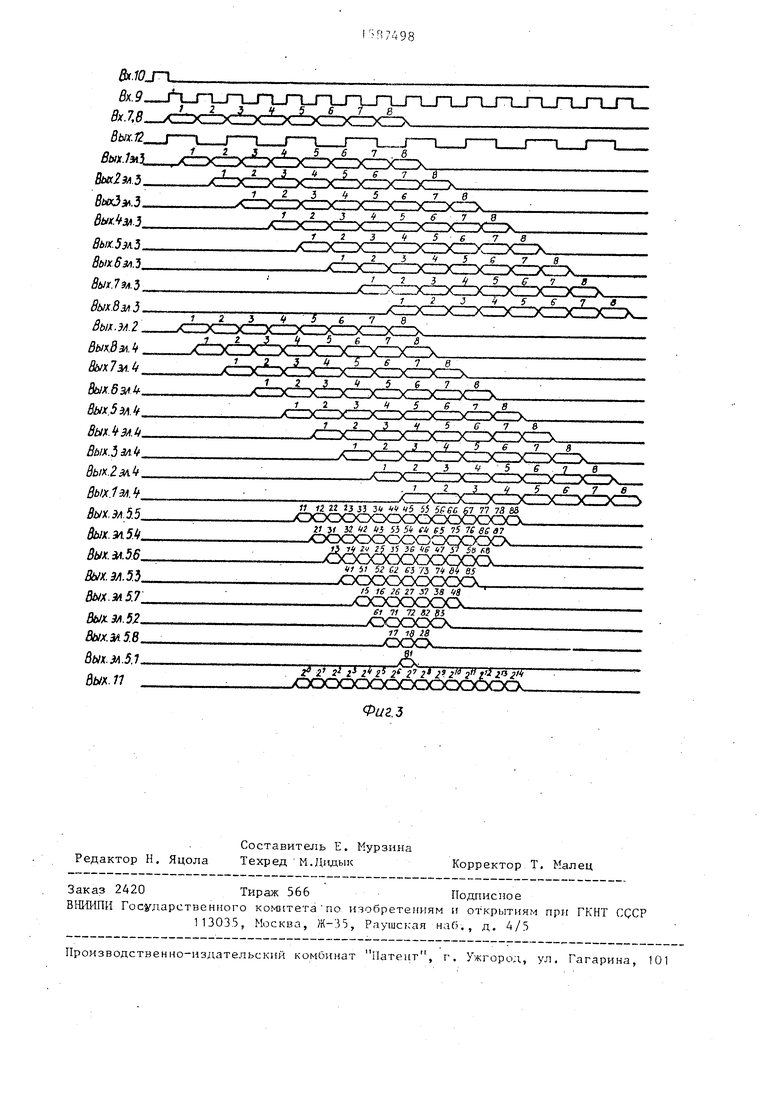

На фиг.1 нредставлена функциональная схема устройства для случая на-фиг.2 - пример реализации блока сложения; на фиг.З - временные диаграммы работы устройства.

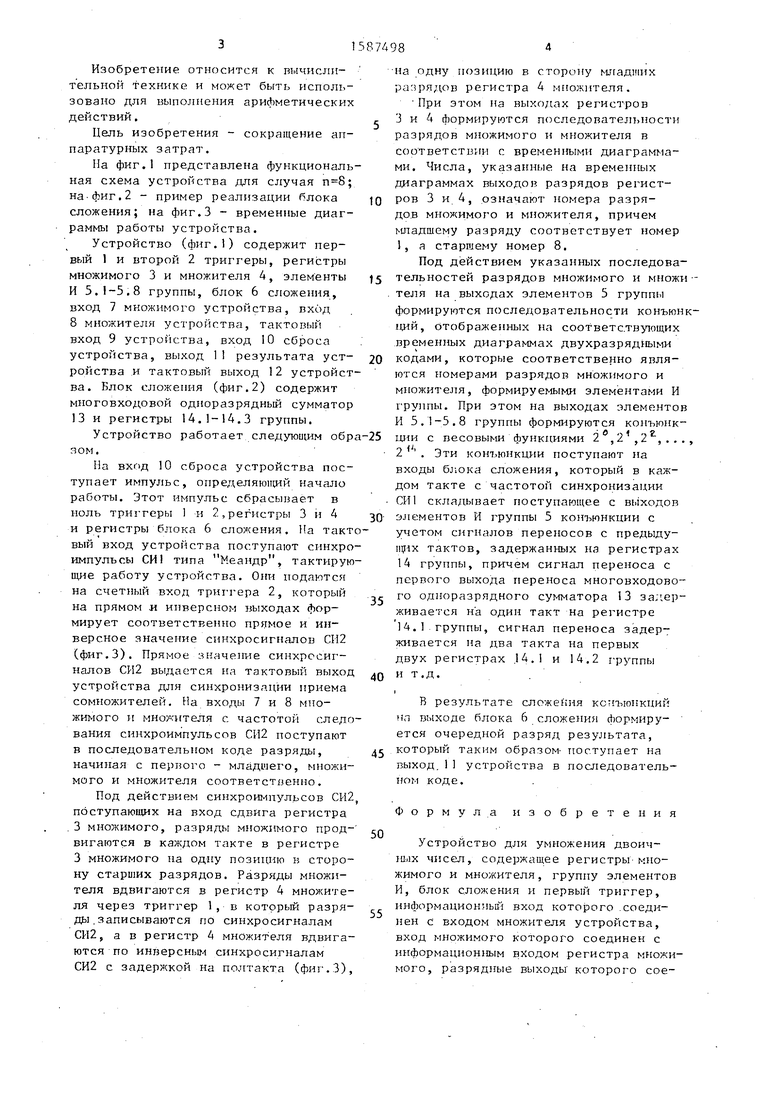

Устройство (фиг.1) содержит первый 1 и второй 2 триггеры, регистры множимого 3 и множителя 4, элем енты И 5.1-5.8 группы, блок 6 сложения, вход 7 множимого устройства, вход 8 множителя устройства, тактовый вход 9 устройства, вход 10 сброса устройства, выход 1 результата уст- ройства .и тактовый выход 12 устройст- ва. Блок сложения (фиг.2) содержит многовходовой одноразрядный сумматор J3 и регистры 14.1-14.3 группы.

Устройство работает следующим обра зом.

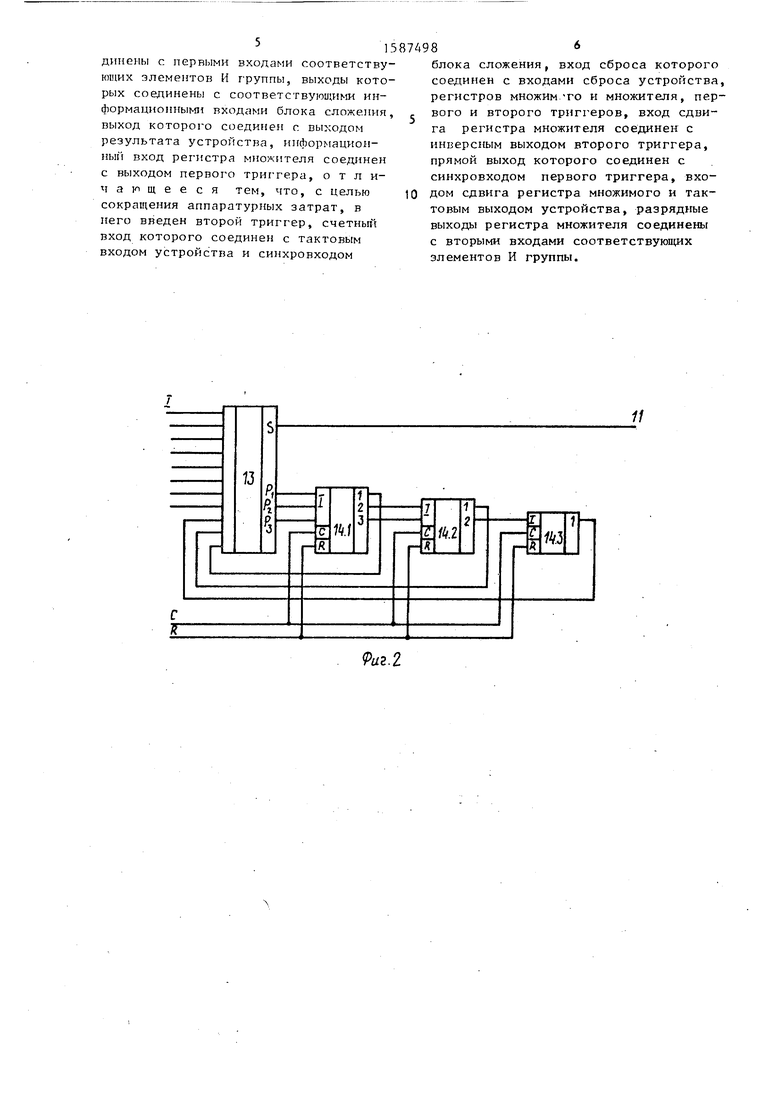

На вхг)д 10 сброса устройства поступает импульс, определяюп ий начало работы. Этот имнульс сбрасывает в ноль триггеры 1 и 2,регистры 3 и 4 и регистры блока 6 сложения. На тактовый вход устройства поступают синхроимпульсы СИ типа Меандр, тактирую- щле работу устройства. Они подаются на счетный вход трнттера 2, который на прямом и инверсном выходах формирует соответственно прямое и инверсное значение синхросигналов СН2 (фиг.З). Прямое значение синхросигналов СИ2 выдается на тактовый выход устройства для синхронизации нрнема сомножителей. На входы 7 и 8 множимого н множителя с частотой следования синхроимпульсов СИ2 поступают в последовательном коде разряды, начиная с первого - младшего, множимого и множителя соответственно.

Под действием синхрошипульсов СИ2, поступающих на вход сдвига регистра

. 3 множимого, разряды М1 ОЖИМОГО ПРОД-

вигаются в каждом такте в регистре 3 множимого на одну позицию в сторону старших разрядов. Разряды множителя вдвигаются в регистр 4 множителя через триггер 1, в котррьй разряды .записываются по синхросигналам СИ2, а в регистр 4 множителя вдвигаются по инверсньм синхросигналам СИ2 с задержкой на полтакта (фиг.З),

Q

5 0

5

0 Q 5

п

5

на одну позицию в cTopo}iy М1гад1 1их разрядов регистра 4 мЕшжителя.

При этом На выходах регистров 3 и 4 формируются последовател1 ности разрядов множимого и множителя в соответствии с временными диаграммами. Числа, указанные на временных диаграммах выходов разрядов регистров 3 и 4, означают }1омера разрядов множимого и множителя, причем младшему разряду соответствует номер 1, а старшему номер 8.

Под действием указанных последовательностей разрядов множимого и множи - теля на выходах элементов 5 rpynnt i формируются последовательности конъюнк- нмй, отображенных на соответствующих временных диаграммах двухразряд№1ми кодами, которые соответственно являются номерами разрядов множимого и множителя, формируемыми элементами И группы. При этом на выходах элементов И 5.1-5.8 группы формируются конъюнкции с вecoвы и функциями 2,, ..., 2 . Эти конъюнкции поступают на входы блока сложения, который в каждом такте с частотой синхронизации СИ1 складывает поступающее с выходов элементов И группы 5 конъюнкции с учетом сигналов переносов с предыдущих тактов, задержанных на регистрах 14 группы, причем сигнал нереноса с первого выхода переноса многовходово- го одноразрядного сумматора 13 за;;ер- живается на один такт на регистре 14.1-группы, сигнал переноса задерживается на два такта на первых двух регистрах .14.1 и 14.2 г-руппы и т.д.

I

В результате сложения конъюнкций ил выходе блока 6 сложения формируется очередной разряд результата, который таким образом- поступает на выход,I1 устройства в последовательном коде.

Формула изобретения

Устройство для умножения двоич- itt.ix чис€У1, содержащее регистры-множимого и множителя, группу элементов И, блок сложения и первый триггер, информационный вход которого .соединен с входом множителя устройства, вход множимого которого соединен с информационным входом регистра множимого, разряд1гые выходы которого соединены с первыми входами соответству юших элементов И группы, выходы кото рых соединены с соответствующими информационными входами блока сложения выход которого соединен с выходом результата устройства, информационный вход регистра множителя соединен с выходом первого триггера, отличающееся тем, что, с целью сокращения аппаратурных затрат, в него введен второй триггер, счетный вход которого соединен с тактовым входом устройства и синхровходом

5874986

-блока сложения, вход сброса которого

-соединен с входами сброса устройства регистров множим го и множителя, пер, с вого и второго триггеров, вход сдвига регистра множителя соединен с инверсным выходом второго триггера, прямой выход которого соединен с синхровходом первого триггера, вхо- 10 дом сдвига регистра множимого и тактовым выходом устройства, разрядные выходы регистра множителя соединены с вторыми входами соответствующих элементов И группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения двоичных чисел | 1990 |

|

SU1711152A1 |

| Устройство для умножения двоичных чисел | 1988 |

|

SU1532918A1 |

| Устройство для умножения двоичных чисел | 1987 |

|

SU1439579A1 |

| Устройство для умножения двоичных чисел | 1990 |

|

SU1765839A1 |

| Устройство для умножения двоичных чисел | 1988 |

|

SU1509877A1 |

| Устройство для вычисления полиномов | 1986 |

|

SU1432509A1 |

| Устройство для умножения по модулю 2 @ -1 @ | 1985 |

|

SU1304018A1 |

| Устройство для умножения чисел с контролем | 1988 |

|

SU1621033A1 |

| Устройство для умножения комплексных чисел | 1990 |

|

SU1751748A1 |

| Арифметическое устройство | 1985 |

|

SU1287144A1 |

Изобретение относится к вычислительной технике и позволяет выполнить умножение чисел в последовательном коде. Цель изобретения - сокращение аппаратурных затрат. В предлагаемое устройство, содержащее регистры множимого 3 и множителя 4, группу элементов И 5, блок сложения 6 и триггер 1, введен триггер 2, что позволяет использовать вместо двух групп элементов И одну и записывать разряды множителя в регистр множителя с задержкой в полтакта, а не такт, что в свою очередь повышает быстродействие устройства. 3 ил.

.66666666S68556&. .66 6ввё6вЛ555ч.

А: 0 fo

11 6/ SZ С2 е} 73 7« а es

.XXDOOOOCXXX

/5 fS 26 27 SI за Ча

-XDOCXDCXDCX

o5(3cS6s

П ТВ 18

OCXDs

.5&SfifKf S Sl

Фиг.5

| Устройство для возведения в степень | 1976 |

|

SU656056A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1972 |

|

SU441563A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-08-23—Публикация

1988-04-21—Подача