чающееся тем, что, с целью повышения быстродействия, сумматоры выполнены в избыточной знакоразрядной системе счисления, в блок анализа состояния введены узел приоритета и шифратор, причем выходы первого и второго регистров соединены с первыми информационными входами четвертого и пятого сумматоров, вторые информационные входы которых соединены с выходами соответственно первого и второго сумматоров, выходы четвертого и пятого сумматоров подключены к информационным входам соответственно второго и первого сдвигателей, выход коммутатор блока анализа состояния соединен с входом узла приоритета блока анализа состояния, информационный выход которого подключен к входу шифратора блока анализа состояния, выход которого соединен с информационным входом узла буферной памяти блока анализа состояния, второй выход которого подключен к второму адресному входу одноразрядного узла памяти блока анализа состояния, управляющий выход узла приоритета блока анализа состояния подключен к информационному входу триггера блока анализа состояния, выход которого соединен с вторым входом элемента И-НЕ и информационным входом триггера блока управления, второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ блока анализа состояния соединен с адресной шиной устройства, дополнительный выход регистра кода операции блока управления подключен к стробирующему входу блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1980 |

|

SU1130861A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU940155A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Универсальный цифровой преобразователь координат | 1980 |

|

SU924701A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Параллельный процессор | 1985 |

|

SU1315989A1 |

| Устройство для вычисления функции | 1984 |

|

SU1180884A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1035604A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1837305A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЭЛЕМЕНТАРНЫХ-ФУНКЦИЙ, содержащее три регистра, два сдвигателя, пять сумматоров, блок памяти, блок управления и блок анализа/состояния, причем первые информационные входы регистров соединены с информационной шиной устройства, выходы первого, второго и третьего сумматоров соединены с соответствующими выходами устройства и с вторыми информационными входами соответствующих регистров, первые информационные входы первого, второго и третьего сумматоров соединены соответственно с выходами первого и второго сдвигателей и выходом третьего регистра, второй информационный вход третьего сумматора соединен с вьЕходом блока памяти, при этом блок управления содержит регистр кода операции, генератор импульсов, триггер, элементы И-НЕ, блок анализа состояния содержит коммутатор, одноразрядный узел памяти, триггер, узел буферной памяти и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, при этом информационный вход регистра кода операции блока управления соединен с шиной кода операции устройства, информационный выход регистра кода операции блока управления соединен с первым адресным входом одноразрядного узла памяти блока анализа состояния и управляющим входом коммутатора блока анализа состояния, информационные входы которого соединены с выходами первого, второго и третьего сумматоров, запускающий вход устройства соединен с .управляющим входом регистра кода операции блока управления, входом запуска генератора импульсов блока управления и установочными § входами триггера блока управления и триггера блока анализа состояния, (Л выход генератора импульсов блока управления соединен с синхровходами регистров узла буферной памяти блока анализа состояния, триггера блока уп-; равления и триггера блока анализа состояния, выход элемента И-НЕ блока управления соединен с управляющими входами регистров, выход узла памяти блока анализа состояния соединен с первым входом элемента ИСЮТЮЧАЩЕЕ ИЛИ блока анализа состояния, выходы узла памяти и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ блока анализа состояния подключены к управляющим входам первого, вто-.рого и третьего сумматоров, первый вход элемента И-НЕ блока управления .. соединен с выходом триггера блока управления, первый выход узла буферной памяти блока анализа состояния соединен с адресной шиной устройства, управляемые входы сдвигателей и адресный вход блока памяти соединены с адресной шиной устройства, о т л и

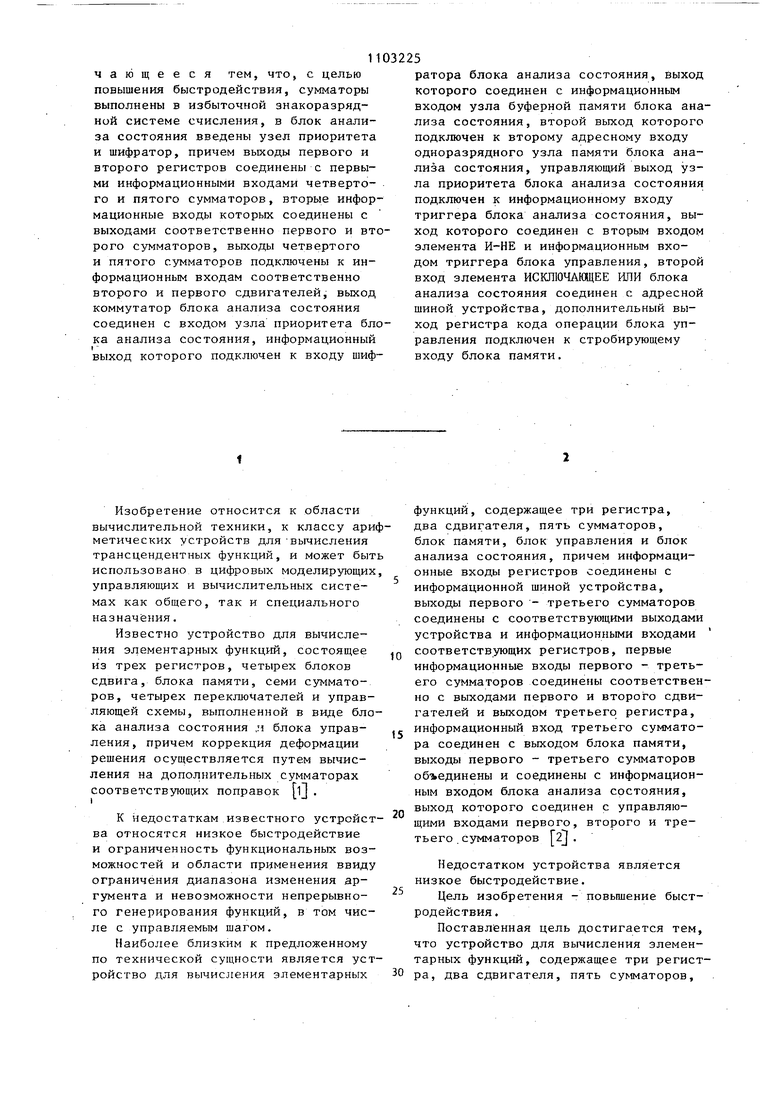

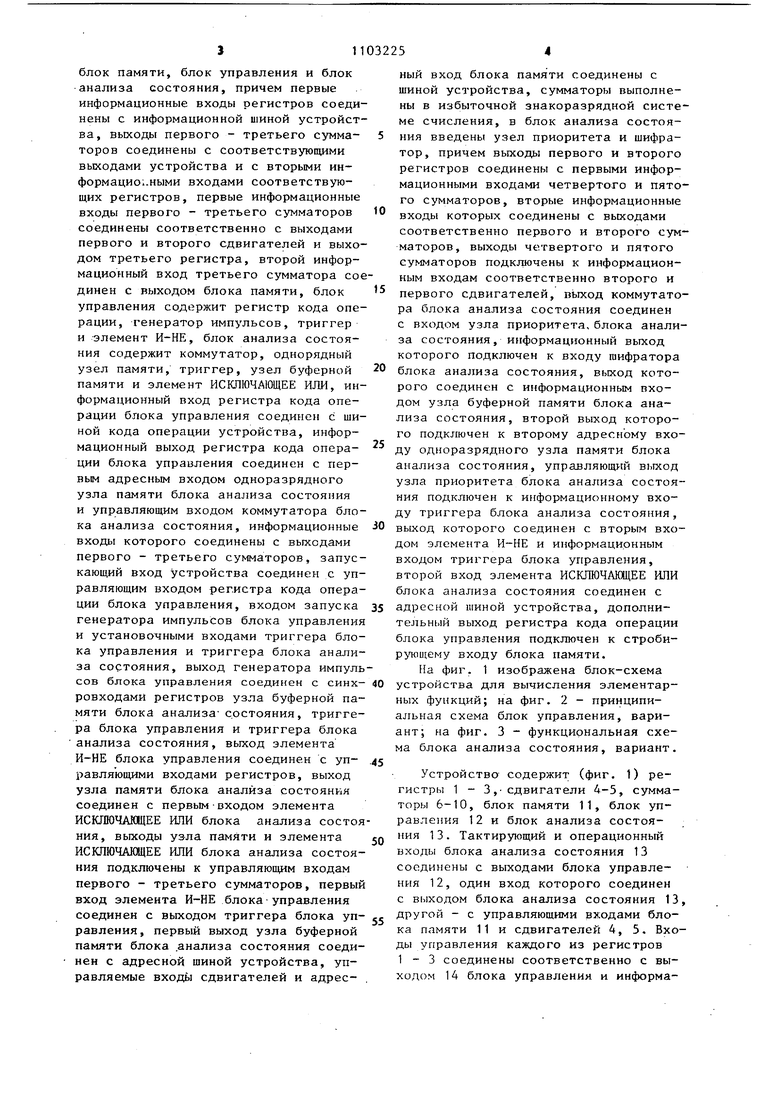

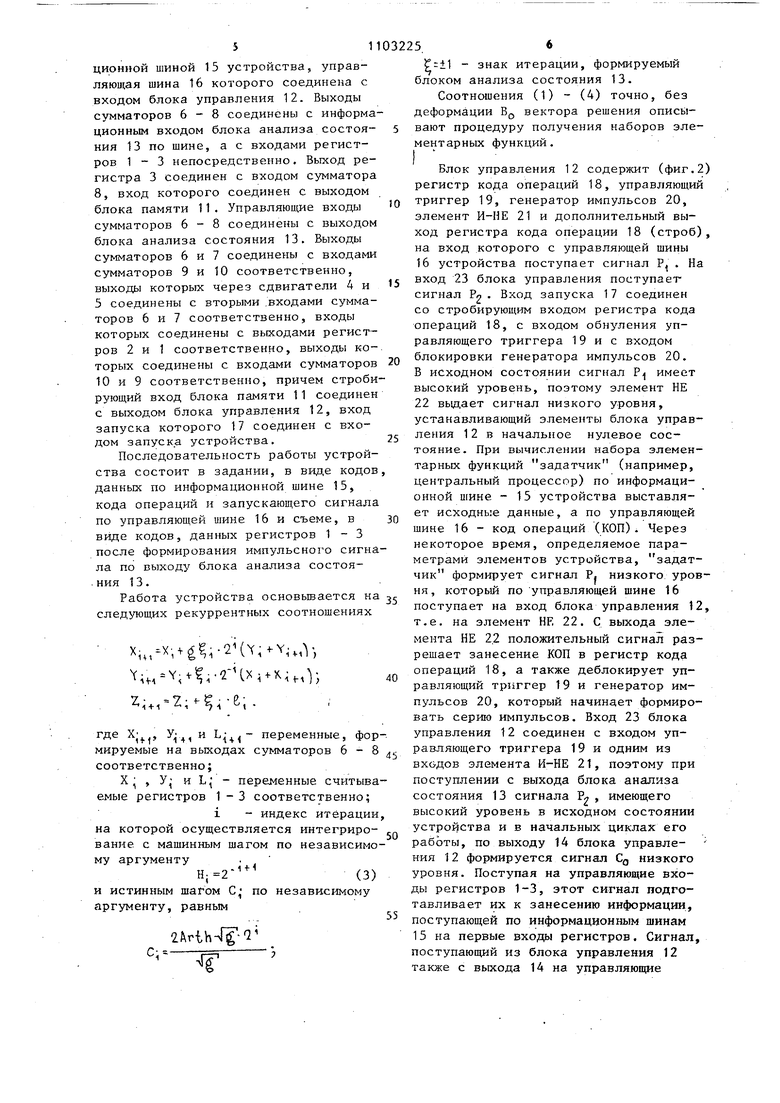

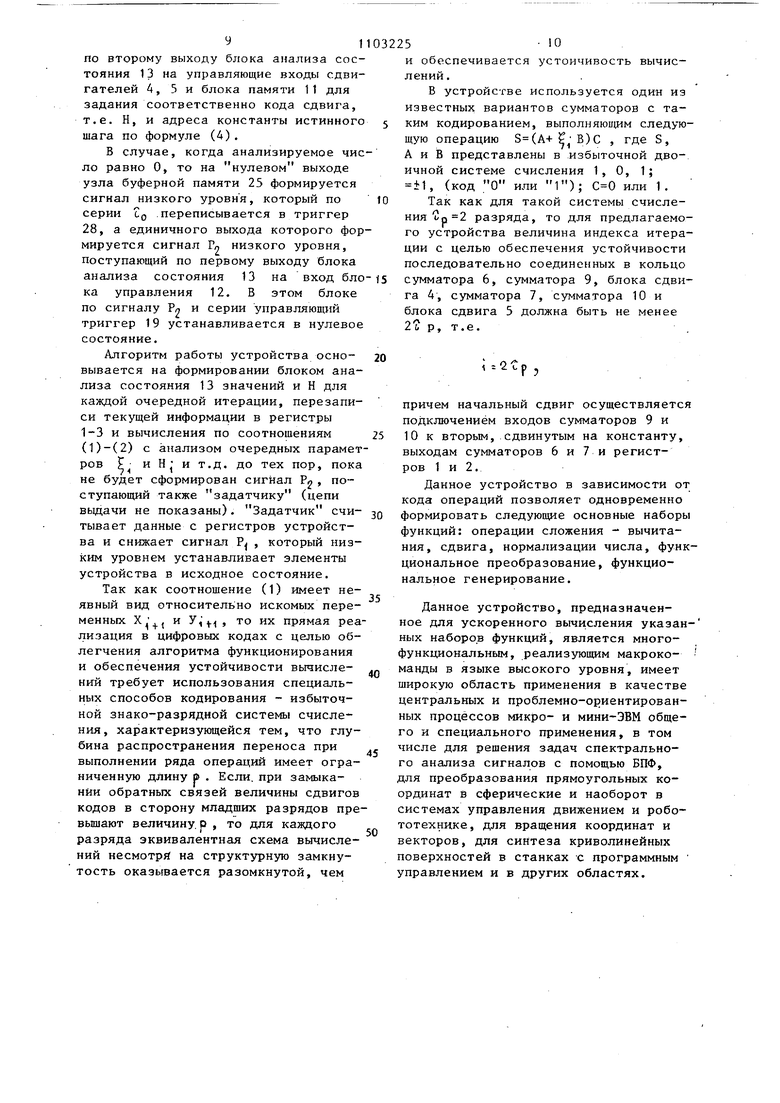

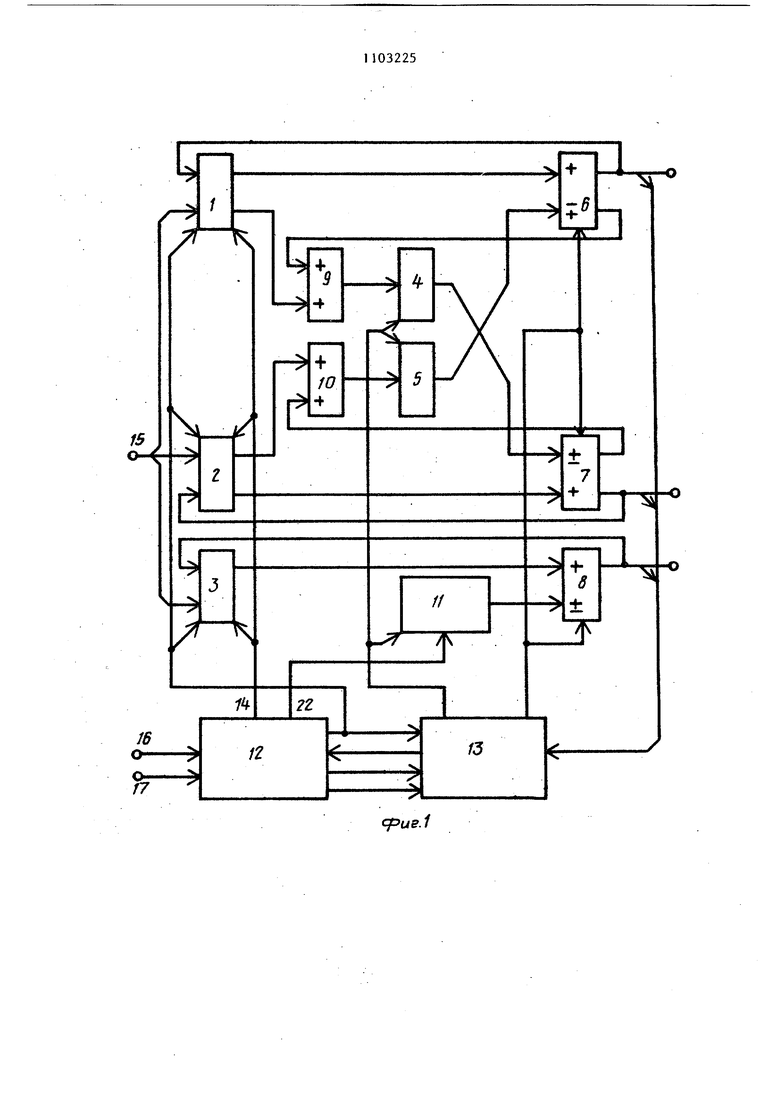

Изобретение относится к области вычислительной техники, к классу ари метических устройств длявычисления трансцендентных функций, и может быт использовано в цифровых моделирующих управляющих и вычислительных системах как общего, так и специального назначения. Известно устройство для вычисления элементарных функций, состоящее из трех регистров, четырех блоков сдвига, блока памяти, семи сумматоров, четырех переключателей и управляющей схемы, выполненной в виде бло ка анализа состояния ,.м блока управления, причем коррекция деформации решения осуществляется путем вычисления на дополнительных сумматорах соответствующих поправок н, i1-1 К недостаткам известного устройст ва относятся низкое быстродействие и ограниченность функциональных возможностей и области применения ввиду ограничения диапазона изменения аргумента и невозможности непрерывного генерирования функций, в том числе с управляемым шагом. Наиболее близким к предложенному по технической сущности является уст ройство для вычисления элементарных функций, содержащее три регистра, два сдвигателя, пять сумматоров, блок памяти, блок управления и блок анализа состояния, причем информационные входы регистров соединены с информационной шиной устройства, выходы первого - третьего сумматоров соединены с соответствующими выходами устройства и информационными входами соответствующих регистров, первые информационные входы первого - третьего сумматоров соединены соответственно с выходами первого и второго сдвигателей и выходом третьего регистра, информационный вход третьего сумматора соединен с выходом блока памяти, выходы первого - третьего сумматоров объединены и соединены с информационным входом блока анализа состояния, выход которого соединен с управляющими входами первого, второго и третьего . сумматоров 2 , Недостатком устройства является низкое быстродействие. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем, что устройство для вычисления элементарных функций, содержащее три регистра, два сдвигателя, пять сумматоров. блок памяти, блок управления и блок анализа состояния, причем первые информационные входы регистров соединены с информационной шиной устройства, выходы первого - третьего сумматоров соединены с соответствующими выходами устройства и с вторыми информационными входами соответствующих регистров, первые информационные входы первого - третьего сумматоров соединены соответственно с выходами первого и второго сдвигателей и выходом третьего регистра, второй информационный вход третьего сумматора сое динен с выходом блока памяти, блок управления содержит регистр кода операции, генератор импульсов, триггер и элемент И-НЕ, блок анализа состояния содержит коммутатор, однорядный узел памяти, триггер, узел буферной памяти и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, информационный вход регистра кода операции блока управления соединен с шиной кода операции устройства, информационный выход регистра кода операции блока управления соединен с первым адресным входом одноразрядного узла памяти блока анализа состояния и управляющим входом коммутатора блока анализа состояния, информационные входы которого соединены с выходами первого - третьего сумматоров, запускающий вход устройства соединен с управляющим входом регистра кода операции блока управления, входом запуска генератора импульсов блока управления и установочными входами триггера блока управления и триггера блока анализа состояния, выход генератора импуль сов блока управления соединен с синх- ровходами регистров узла буферной памяти блока анализа состояния, триггера блока управления и триггера блока анализа состояния, выход элемента И-НЕ блока управления соединен с управляющими входами регистров, выход узла памяти блока анализа состояния соединен с первым-входом элемента ИСКГГОЧАЩЕЕ ИЛИ блока анализа состоя ния, выходы уэла памяти и элемента ИСКЛЮЧАЩЕЕ ИЛИ блока анализа состояния подключены к управляющим входам первого - третьего сумматоров, первый вход элемента И-НЕ блока управления соединен с выходом триггера блока управления, первый выход узла буферной памяти блока .анализа состояния соединен с адресной щиной устройства, управляемые входь сдвигателей и адресный вход блока памяти соединены с шиной устройства, сумматоры выполнены в избыточной знакоразрядной системе счисления, в блок анализа состояния введены узел приоритета и шифратор, причем выходы первого и второго регистров соединены с первыми информационными входами четвертого и пятого сумматоров, вторые информационные входы которых соединены с выходами соответственно первого и второго сумматоров, выходы четвертого и пятого сумматоров подключены к информационным входам соответственно второго и первого сдвигателей, вьгход коммутатора блока анализа состояния соединен с входом узла приоритета,блока анализа состояния, информационный выход которого подключен к входу шифратора блока анализа состояния, выход которого соединен с информационным входом узла буферной памяти блока анализа состояния, второй выход которого подключен к второму адресному входу одноразрядного узла памяти блока анализа состояния, управляющий выход узла приоритета блока анализа состояния подключен к информационному входу триггера блока анализа состояния, выход которого соединен с вторым входом элемента VI-HE и информационным входом триггера блока управления, второй вход элемента ИСКЛЮЧАЩЕЕ ИЛИ блока анализа состояния соединен с адресной шиной устройства, дополнительный выход регистра кода операции блока управления подключен к стробирующему входу блока памяти. На фиг. 1 изображена блок-схема устройства для вычисления элементарных функций; на фиг. 2 - принципиальная схема блок управления, вариант; на фиг. 3 - функциональная схема блока анализа состояния, вариант. Устройство содержит (фиг. 1) регистры 1 - 3, сдвигатели -5, сумматоры 6-10, блок памяти 11, блок управления 12 и блок анализа состояния 13. Тактирующий и операционный входы блока анализа состояния 13 соединены с выходами блока управления 12, один вход которого соединен с в 1ходом блока анализа состояния 13, другой - с управляющими входами блока памяти 11 и сдвигателей 4, 5. Входы управления каждого из регистров 1 - 3 соединены соответственно с выходом 14 блока управления и информационной шиной 15 устройства, управляющая шина 16 которого соединена с входом блока управления 12. Выходы сумматоров 6-8 соединены с информа ционным входом блока анализа состоякия 13 по шине, а с входами регистров 1 - 3 непосредственно. Выход регистра 3 соединен с входом сумматора 8, вход которого соединен с выходом блока памяти 11, Управляющие входы сумматоров 6-8 соединены с выходом блока анализа состояния 13. Выходы сумматоров 6 и 7 соединены с входами сумматоров 9 и 10 соответственно, выходы которых через сдвигатели 4 и 5 соединены с вторыми .входами сумматоров 6 и 7 соответственно, входы которых соединены с вькодами регистров 2 и 1 соответственно, выходы которых соединены с входами сумматоров 10 и 9 соответственно, причем строби рующий вход блока памяти 11 соединен с выходом блока управления 12, вход запуска которого 17 соединен с входом запуска устройства. Последовательность работы устройства состоит в задании, в вир,е кодов данных по информадионной шине 15, кода операций и запускающего сигнала по управляющей щине 16 и съеме, в виде кодов, данных регистров 1 - 3 после формирования импульсного сигна ла по выходу блока анализа состоя.ния 13. Работа устройства основьюается на следующих рекуррентных соотношениях x,,x-,.g,-24,v.,,V, 4;,,Y,t,-2-4x i UO; , .. ,. где Xj, У, и переменные, фор мируемые на выходах сумматоров 6 - 8 соответственно; X , У и L, - переменные считыва емые регистров 1 - 3 соответственно; i - индекс итерации на которой осуществляется интегрирование с машинным шагом по независимо му аргументу (3) и истинным шагом С, по независимому аргументу, равным 2ЛНЬ4 2 -±1 - знак итерации, формируемый блоком анализа состояния 13. Соотношения (1) - (4) точно, без деформации В вектора решения описывают процедуру получения наборов элементарных функций. Блок управления 12 содержит (фиг.2) регистр кода операций 18, управляющий триггер 19, генератор импульсов 20, элемент И-НЕ 21 и дополнительный выход регистра кода операции 18 (строб), на вход которого с управляющей шины 16 устройства поступает сигнал Р . На вход 23 блока управления поступает сигнал Рл . Вход запуска 17 соединен со стробирующим входом регистра кода операций 18, с входом обнуления управляющего триггера 19 и с входом блокировки генератора импульсов 20. В исходном состоянии сигнал Р;| имеет высокий уровень, поэтому элемент НЕ 22 выдает сигнал низкого уровня, устанавливающий элементы блока управления 12 в начальное нулевое состояние. При вычислении набора элементарных функций задатчик (например, центральный процессор) по информационной щине - 15 устройства выставляет исходные данные, а по управляющей щине 16 - код операций (КОП). Через некоторое время, определяемое параметрами элементов устройства, задатчик формирует сигнал Р. низкого уровня , который по управляющей шине 16 поступает на вход блока управления 12, т.е. на элемент НЕ 22. С выхода элемента НЕ 2.2 положительный сигнал разрещает занесение КОП в регистр кода операций 18, а также деблокирует управляющий триггер 19 и генератор импульсов 20, который начинает формировать серию импульсов. Вход 23 блока управления 12 соединен с входом управляющего триггера 19 и одним из входов элемента И-НЕ 21, поэтому при поступлении с выхода блока анализа состояния 13 сигнала Р , имеющего высокий уровень в исходном состоянии устройства и в начальных циклах его работы, по выходу 14 блока управле- ния 12 формируется сигнал Сд низкого уровня. Поступая на управляющие входы регистров 1-3, этот сигнал подготавливает их к занесению информации, поступающей по информационным шинам 15 на первые входы регистров. Сигнал, поступающий из блока управления 12 также с выхода 14 на управляющие

(стробирующие) входы регистров , положительным фронтом (окончанием импульса) разрешает занесение информации в эти регистры из информационной шины 15. Этим же фронтом управляющий триггер 19 блока управления 12 переводится в единичное состояние (так как Рл имеет высокий уровень) , формируя сигнал Сд высокого уровня, который, поступая на управляющие входы регистров 1-3, обеспечивает с приходом каждого положительного фронта серии занесение информации по BTopbw входам регистров.

С одного из выходов регистра кода операций 18 блока управления 12 снимается сигнал С, который, поступая с выхода блока управления 12 на стробирующий вход блока памяти 11, разрешает или запрещает считывание из него информации с константах С (4), что необходимо для организации режима непрерывного генерирования функций с дискретно управляемым щагом.

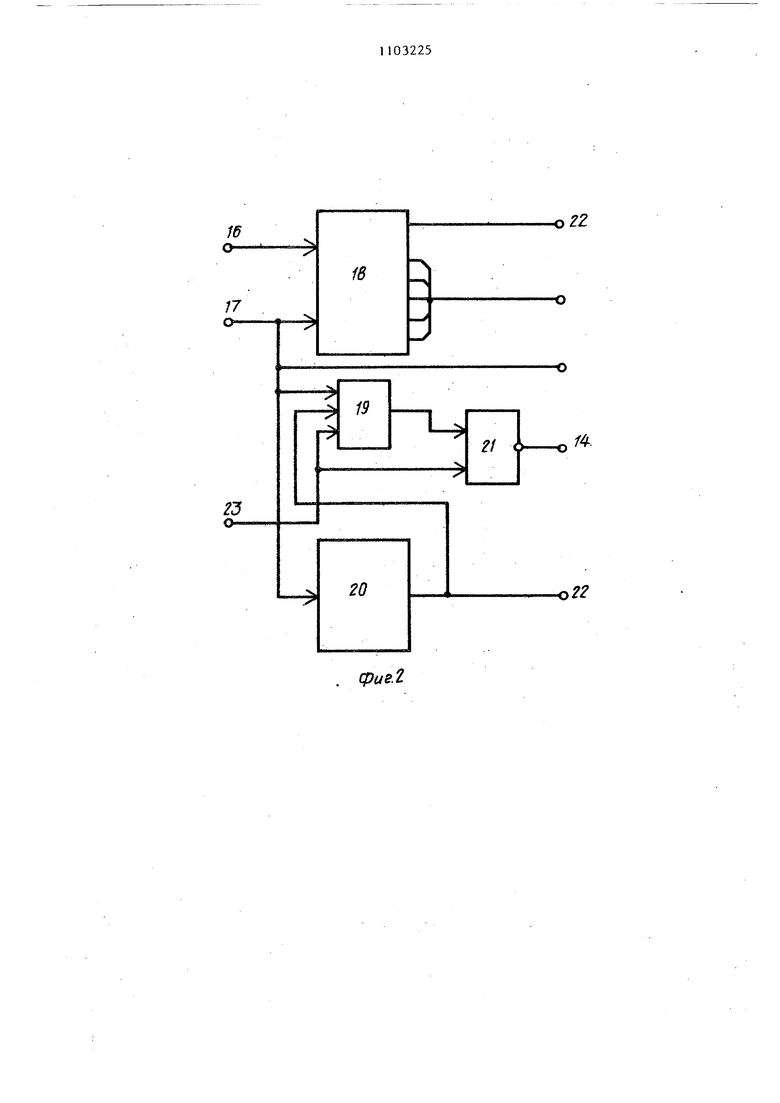

Блок анализа состояния 13 содержит (фиг, 3) коммутатор 24, узел буферной памяти 25, одноразрядный узел памяти 26, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 27, триггер 28, узел приоритета 29 и шифратор 30. Выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 27 является выходом блока анализа состояния, тактирующий вход которого соединен с синхронизирующими входами узла буферной памяти 25 и триггера 28, информационный вход которого соединен с выходом нуля узла буферной памяти 25, выход младших разрядов которого соединен с одним адресным входом одноразрядного узла памяти 26, другой адресный вход которого соединен с адресным входом коммутатора 24 и -операционным входом блока анализа состояния 13, информационный вход 17 которого соединен с информационными входами коммутатора 24, выход которого соединен с информационным входом узла буферной памяти 25, выходы старших разрядов которого соединены с выходом блока анализа состояния 13, соединенным с операционным входом блока анализа состояния и одним входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 27, другой вход которого соединен с выходом одноразрядного узла памяти 26 и выходом блока анализа состояния 13, по шине соединенным с выходом, элемента ИСКПЮЧАКЩЕЕ ИЖ 27. Выход коммутатора 24 подключен к вхо3225

.ду узла приоритета .29, информационный выход которого подключен к входу шифратора 30, выход которого подключен к входу узла буферной памяти 25, 5 управляющий выход узла приоритета 29 подключен к дополнительному информационному входу триггера 28. КОП с регистра кода операций 18 блока управления 12 вместе с инверсным сигналом to PJ через выход поступает по операционному входу в блок анализа состояния 13, в котором в соответствии с КОП выбирается канал коммутатора 24. Кроме того, сигналы КОП являются час5 тью адреса одноразрядного узла памяти

26,а один из разрядов КОП (-qu) кодирующий величину q( для тригонометрических функций, - для гиперболических функ0 ций, а также экспоненциальных), поступает на элемент ИСКЛЮЧАЮЩЕЕ ИЛИ

27,с выхода которого через выход блока анализа состояния 13 выдается сигнал на сумматор 6 для управления

5 знаком операции - сложение или вычитание. Кроме того, разряд КОП через выход блока анализа состояния 13 поступает на управляющий вход блока памяти 11 в качестве части адреса для выQ бора типа константы (4). Инверсный сигнал Р, подается на установочный вход триггера 28 для сброса в исходное состояние после окончания вычислений .

С выходов коммутатора 24 на вход узла буферной памяти 25 поступают данные с первого выхода одного из сумматоров 6-8. Узел 25 осуществляет формирование знака числа и адреса

,. старшего единичного разряда. Так как каждый разряд сумматоров для двоичного избыточного кодирования (1, О, 1) представлен в виде двух разрядов (1 -1-код 10; 00; +1код 01), то при подсоединении этих кодов к узлу 25 по приоритету, начиная от старших разрядов, выходной код этого элемента будет содержать младший разряд, фиксирующий знак анализируемого числа, и старшие разря-

ды, представляющие код номера значащего разряда, т.е. двоичный порядок числа. Знак анализируемого числа поступает в одноразрядный узел памяти 26 для формирования , , обеспечивая

5 сходимость процессов вьгчислений в различных квадрантах пространства допустимых областей определения функций . Старшие разряды , поступают по второму выходу блока анализа сос тояния 13 на управляющие входы сдви гателей 4, 5 и блока памяти 11 для задания соответственно кода сдвига, т.е. Н, и адреса константы истинного шага по формуле (4). В случае, когда анализируемое чис ло равно О, то на нулевом выходе узла буферной памяти 25 формируется сигнал низкого уровня, который по серии Со .переписывается в триггер 28, а единичного выхода которого фор мируется сигнал Рл низкого уровня. Поступающий по первому выходу блока анализа состояния 13 на вход бло ка управления 12. В этом блоке по сигналу Рл и серии управляющий триггер 19 устанавливается в нулевое состояние. Алгоритм работы устройства основывается на формировании блоком анализа состояния 13 значений и Н для каждой очередной итерации, перезаписи текущей информации в регистры 1-3 и вычисления по соотношениям (1)-(2) с анализом очередных парамет ров Г и Н и т.д. до тех пор, пока не будет сформирован сигнал Pg, поступающий также задатчику (цепи выдачи не показаны). Задатчик считывает данные с регистров устройства и снижает сигнал Р , который низким уровнем устанавливает элементы устройства в исходное состояние. Так как соотношение (1) имеет неявный вид относительно искомых переменных X , и У, , то их прямая реа лизация в цифровых кодак с целью облегчения алгоритма функционирования и обеспечения устойчивости вычислений требует использования специальных способов кодирования - избыточной знако-разрядной системы счисления, характериззпощейся тем, что глубина распространения переноса при выполнении ряда операций имеет ограниченную длину р. Если, при замыкании обратных связей величины сдвигов кодов в сторону младших разрядов пре вышают величину, р , то для каждого разряда эквивалентная схема вычислений несмотрй на структурную замкнутость оказывается разомкнутой, чем и обеспечивается устойчивость вычислений. В устройстве используется один из известных вариантов сумматоров с таким кодированием, выполияюиц1м следующую операцию S()C , где S, А и В представлены в избыточной двоичной системе счисления 1, О, 1; i1, (код О или 1); или 1. Так как для такой системы счисления разряда, то для предлагаемого устройства величина индекса итерации с целью обеспечения устойчивости последовательно соединенных в кольцо сумматора 6, сумматора 9, блока сдвига 4, сумматора 7, сумматора 10 и блока сдвига 3 должна быть не менее 2л ь р, т.е. причем начальный сдвиг осуществляется подключением входов сумматоров 9 и 10 к вторым, сдвинутым на константу, выходам сумматоров 6 и 7 и регистров 1 и 2. Данное устройство в зависимости от кода операций позволяет одновременно формировать следуюа№1е основные наборы функций: операции сложения - вычитания, сдвига, нормализации числа, функциональное преобразование, функциональное генерирование. Данное устройство, предназначенное для ускоренного вычисления указанных наборо.в функций, является многоункциональньгм, реализующим макроко- манды в языке высокого уровня, имеет широкую область применения в качестве центральных и проблемно-ориентированных процессов микро- и мини-ЭВМ общего и специального применения, в том числе для решения задач спектрального анализа сигналов с помощью БПФ, ля преобразования прямоугольных координат в сферические и наоборот в системах управления движением и робототехнике, для вращения координат и векторов, для синтеза криволинейных оверхностей в станках с программным правлением и в других областях.

cpue.1

16

О

/7 о-

. срие.2

4)2

/4.

f/

ю

cpus.3

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления тригонометрических функций | 1974 |

|

SU519717A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 2877479, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-15—Публикация

1980-06-26—Подача