Изобретение относится к вычислительной технике, в частности к устойствам тестового контроля логических схем и диагностики неисправностей, и является усовершенствованием известного устройства, описанного в авт. св. № 746553.

Целью изобретения является повышение достоверности контроля.

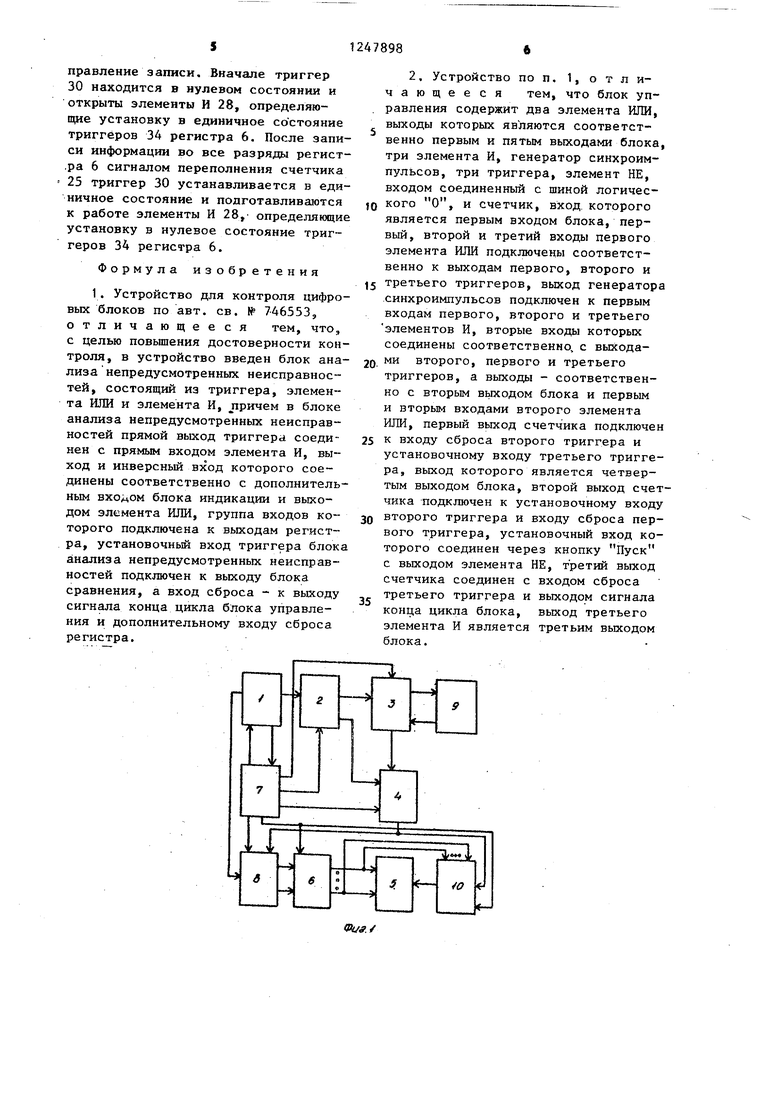

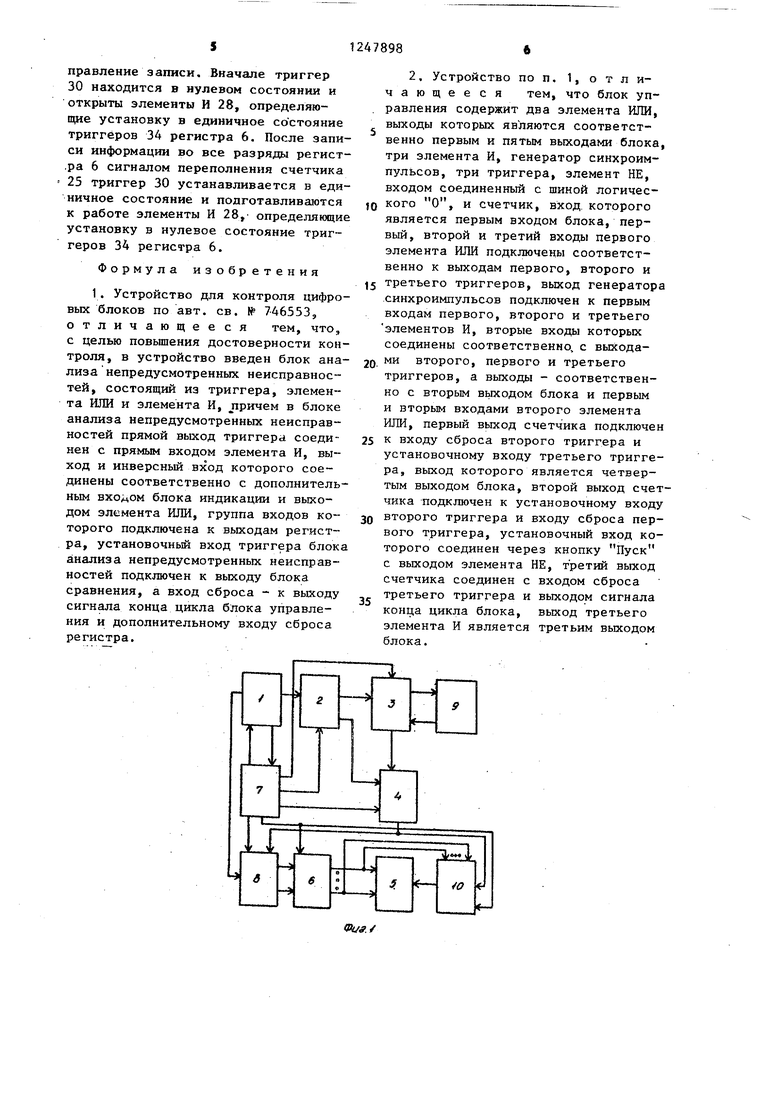

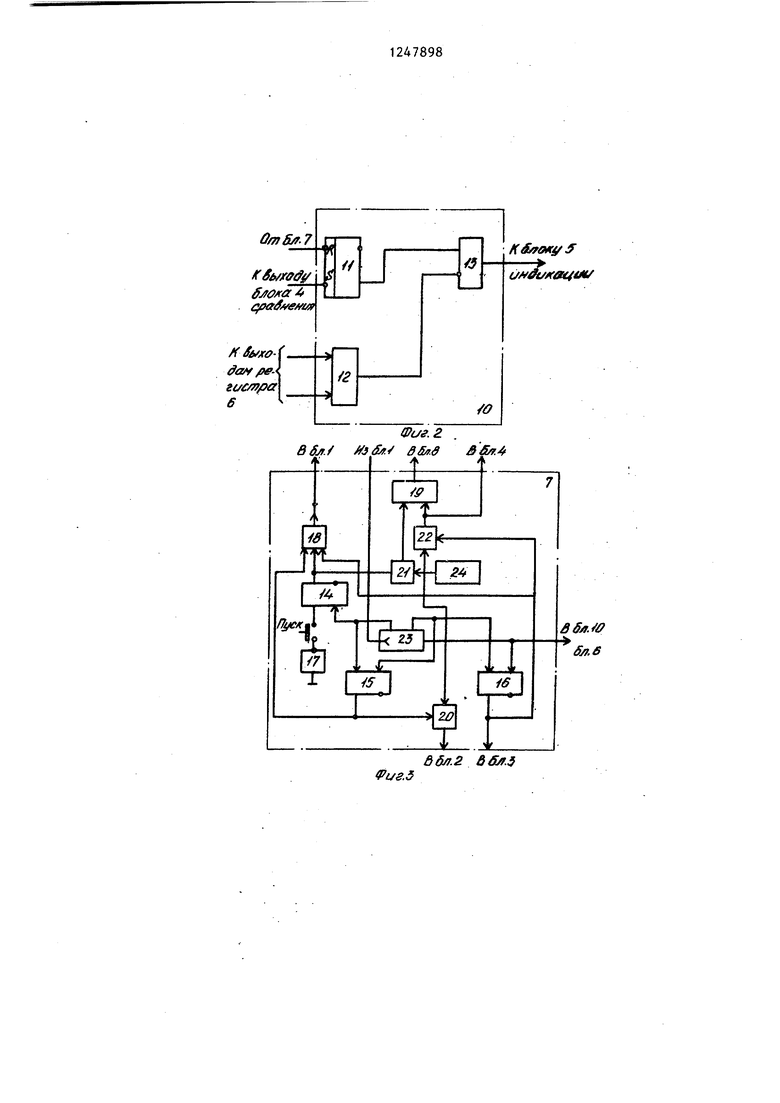

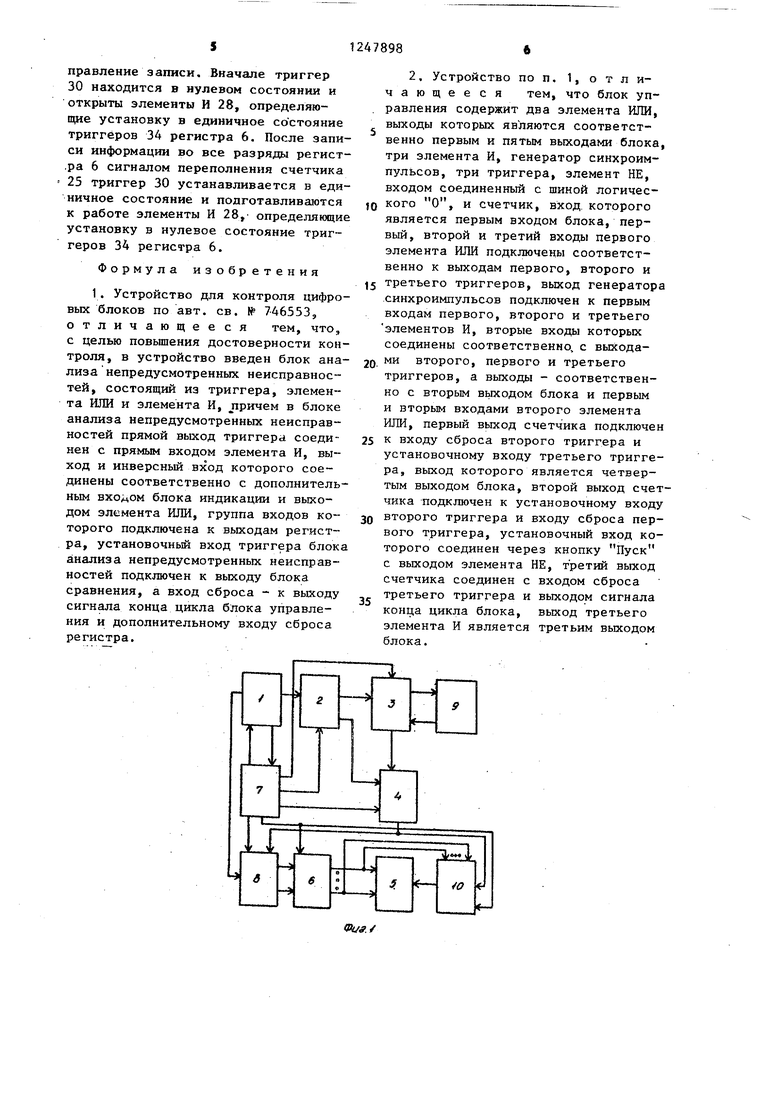

На фиг. 1 представлена функциональная схема устройства на фиг.2 - функциональная схема блока анализа непредусмотренных неисправностей; , на фиг. 3 - функциональная схема блока управления; на фиг. 4 - функциональная схема блока переключения; на фиг. 5 - функциональная схема блока сравнения; на фиг. 6 - функциональная схема регистра.

1

Устройство (фиг. 1) содержит блок ввода, блок 2 памяти, коммутатор 3,

блок 4 сравнения, регистр 6, блок 7

блок 5 индикации, управления, блок 8

переключения, контролируемый блок 9 и блок 10 анализа непредусмотренных неисправностей.

Блок 10 анализа непредусмотренных неисправностей (фиг, 2) содержит тригер 11, элемент ШШ 12, элемент И 13 Блок 7 управления (фиг. 3) содержит триггеры 14 - 16, элемент НЕ 17, элементы ИЛИ 18 и 19, элементы И 20-22, счетчик 23 и генератор 24 синхроимпульсов.

Блок 8 переключения (фиг. 4) содержит счетчик 25, дешифратор 26, элементы И 27, 28, элемент НЕ 29, триггер 30.

Блок 4 сравнения (фиг, 5) содержит схемы сравнения 31, элемент ИЛИ 32, элемент И 33.

Регистр 6 (фиг. 6) содержит триггеры 34.

Блок 1 ввода предназначен для ввода с перфоленты тестовой информации, информации о входных (выходных) контактах, информации о проверяемых неисправностях (перечень проверяемых неисправностей), диагностической информации (номера неисправностей, пров-еряемых в каждом тесте) и командной информации.

Блок 2 памяти предназначен для хранения и выдачи тестовой информации через коммутатор 3 на блок 9. Коммутатор 3 предназначен для коммутации внешних контактов блока 9, при этом входные контакты подключаются к выходам блока 2 памяти (к той части, где хранятся стимулы), выходные контакты подключаются ко входам блока 4 сравнения.

индикации предназначен для индикации номера неисправности и непредусмотренной неисправности. В регистре 6 фиксируются номера обнаруженных неисправностей. Блок 8 переключения

переключает диагностическую информацию на нулевые или единичные входы регистра 6.

Блок 10 анализа непредусмотренных неисправностей вырабатывает сигнал

5 1 при наличии в устройстве непредусмотренной неисправности (фиг. 2). Триггер 11 фиксирует факт появления низкого потенциала на выходе блока

4сравнения хотя бы на одном тесто- 0 вом наборе, элемент ИЛИ 12 суммируетсигнал с выходов регистра 6, элемент И 13 формирует сигнал на блок

5индикации.

Устройство работает следующим об- 5 разом.

В исходном состоянии блок 2 памяти, регистр 6 и триггер 11 по командам с блока 7 установлены в нулевое состояние (цепи сброса не показаны) . Вначале после установки триггера 14 блока 7 в единичное состояние с блока 1 вводится информация о проверяемых неисправностях и по командам с блока 7 с выхода эле- 5 мента ШШ 19 синхронно с вводом через блок 8 записывается в регистр 6.Информация о проверяемых неисправностях является перечнем неисправностей, проверяемых в блоке 9. Раз- рядность регистра 6 равна максимальному количеству проверяемых неисправностей блоков 9. При вводе информации о проверяемых неисправнос- -тях каждый разряд регистра 6 уста- 5 навливаетс я в -1, если соответст- вул)щая ему неисправность проверяется в данном объекте контроля.После подготовки регистра 6 по командам с блока 7 тестовая информация (стимулы 5® и эталоны) записывается в блок 2. Стимулы из блока 2 поступают через коммутатор 3 на входы блока 9, а эталоны - на. первые выходы блока 4 сравнения. Управление работой ком- 55 мутатора 3 осуществляется по сигналам из блока 7. По результатам сравнения, если контролируемый блок 9 исправен, появляется высокий потенциал на выходе блока 4 сравнения. Если на данном тестовом наборе на выходе контролируемого блока 9 неправильное значение, то на выходе блока 4 сравнения появляется низкий потенциал. При этом прямой выход триггера 11 устанавливается в 1 и поддерживается в таком состоянии до конца проверки независимо от последующих значений на выходе блока 4. После подачи на входы блока 9 очередного набора по команде из блока 7 из блока 1 вводится диагностическая информация, которая через блок 8 поступает на установку в О разрядов регистра 6. Диагностическая информация представляет позиционный код, длина которого (разрядность) равна общему количеству проверяемых неисправностей. Каждому номеру неисправности из списка неисправностей соответствует один разряд позиционного кода, причем только в разрядах позиционного кода, соответствующих веряемым в данном тесте неисправностям, записаны 1. Каждому тестовому набору соответствует своя диагностическая информация. Если в очередном тесте не обнаружены неисправности (на выходе блока сравнения - Г ), то разряды регистра 6, соответствующие коду диагностической информации данного теста, устанавливаются в О Сигнал на выходе блока 4 сравнения разрешает запись диагностической информации в регистр 6, Если в очередном тесте обнаружена, неисправность, то установление в О разрядов регистра 6 не происходит.

После ввода диагностической информации по командам с блока 7 управления в блок 2 памяти вводится следующий тест, который поступает затем на входы блока 9, и начинается ввод диагностической информации.

После подачи всех тестовых наборов в регистре 6 будут установлены в 1 разряды, соответствующие неисправностям, проверяемым на всех тех наборах, на которых получены неправильные выходные сигналы контролируемого блока 9. Значения разрядов регистра 6 суммируются на элементе ИЛИ 12. Сигнал с выхода ИЛИ 12 поступает далее на инвертирующий вход элемента И 13. Если, по крайней мере, на одном тестовом наборе получено неправильное значение, а все разряды регистра 6 установились

Д78984

в О, то на прямом выходе триггера 11 установится 1, а на выходе элемента ИЛИ 12 - значение О. Соответственно на выходе элемента И 13 J тогда появляется сигнал 1, свидетельствующий о наличии непредусмотренной неисправности. С выхода элемента И 13 сигнал поступает для отображения в блок 5 индикации. На

(О выходе элемента И 13 будет О, если контролируемый блок 9 исправен (т.е. на прямом выходе триггера 10 значение О) либо имеет место не- Hcnp feHocTb из заданного списка

)5 (т.е. по крайней мере, один разряд регистра 6 установлен в 1).

Устройство работает поэтапно, в начале работы устанавливается в единичное состояние триггер 14 блока

20 7, после ввода информации о проверяемых неисправностях сигналом Конец ввода из блока 1 через сметчик

23триггер 14 устанавливается в нулевое состояние, а триггер 15 - в

25 единичное. Тем самым определяется начало ввода тестовой информации в блок 2 памяти. Сигналы с генератора

24в первом случае через элемент И 21 и элемент ИЛИ 19 поступают в блок 8 на счетчик 25, а во втором через элемент И 20 - в блок 4 на элемент И 33, таким обра зом осуществляется пошаговая запись информации в регистр бив блок 2. После окончания ввода тестовой информации сиг налом Конец ввода из блока 1 через счетчик 23 (второй его выход), триггер 15 устанавливается в нулевое состояние, а триггер 16 в единичное, тем самым определяется начало третьего этапа в контроле блока 9. Триггер 16 дает раз1 ешение в коммутатор 3 на выдачу тестовых воздействий из блока 2 в блок 9 и реакций с блока 9 на схему 31 сравнения блока 4. Одновременно вводится диагностичест кая информация из блока 1, которая поступает на элементы И 28 блока 8. Сигналы с генератора 24 через элемент И 22 и элемент ИЛИ 19 поступа ют на счетчик 25 блока 8, синхронизируя тем самым работу устройства. Счетчик 25 и дешифратор 26 управляют записью на регистр 6 информации о проверяемых неисправностях и ди55 агностической информации (на еди- ничное и нулевое плечо триггеров соответственно). Триггер 30, элемент И 27,элемент НЕ 29 определяют направление записи. Вначале триггер 30 находится в нулевом состоянии и открыты элементы И 28, определяющие установку в единичное со стояние триггеров 34 регистра 6. После записи информации во все разряды регист- ,ра 6 сигналом переполнения счетчика 25 триггер 30 устанавливается в единичное состояние и подготавливаются к работе элементы И 28, определякяцие установку в нулевое состояние триггеров 34 регистра 6.

Формула изобретения

1. Устройство для контроля цифровых блоков по авт. св. № 746553,, отличающееся тем, что., с целью повьшения достоверности контроля, в устройство введен блок анализа непредусмотренных неисправностей, состоящий из триггера, элемента ИЛИ и элемента И, причем в блоке анализа непредусмотренных неисправностей прямой выход триггера соединен с прямым входом элемента И, выход и инверсный вход которого соединены соответственно с дополнительным входом блока индикации и выходом элемента ИЛИ, группа входов которого подключена к выходам регистра, установочньй вход триггера блок анализа непредусмотренных неисправностей подключен к выходу блока сравнения, а вход сброса - к выходу сигнала конца цикла блока управления и дополнительному входу сброса регистра.

2. Устройство по п. 1, отличающееся тем, что блок управления содержит два элемента ШШ, выходы которых являются соответст- венно первым и пятым выходами блока, три элемента И, генератор синхроимпульсов, три триггера, элемент НЕ, входом соединенный с шиной логичес- ,0 кого О, и счетчик, вход которого является первым входом блока, первый, второй и третий входы первого элемента ШШ подключены соответственно к выходам первого, второго и ,5 третьего триггеров, выход генератора синхроимпульсов подключен к первым входам первого, второго и третьего элементов И, вторые входы которых соединены соответственно, с выхода- 20 ми второго, первого и третьего

триггеров, а выходы - соответственно с вторым выходом блока и первым и вторым входами второго элемента ИЛИ, первый вьшод счетчика подключен 25 к входу сброса второго триггера и установочному входу третьего триггера, выход которого является четвертым выходом блока, второй выход счетчика подключен к установочному входу второго триггера и входу сброса первого триггера, установочный вход которого соединен через кнопку Пуск с выходом элемента НЕ, третий выход счетчика соединен с входом сброса третьего триггера и выходом сигнала конца цикла блока, выход третьего элемента И является третьим выходом блока.

30

35

Фаг. 2 Вёл/ /ti&r. e5ff.S SSff.4

В5л.& ff.e

Фие.д

дбп.г es.i

If36j7.7

От &Л7 (Ри. 6

Фиг.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики дискретных блоков | 1985 |

|

SU1254488A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1012263A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для диагностики логических блоков | 1988 |

|

SU1672452A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1608672A1 |

| Устройство для обнаружения и локализации неисправностей цифровых блоков | 1982 |

|

SU1067507A1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Устройство для диагностики блоков электронных вычислительных машин | 1978 |

|

SU746556A1 |

Изобретение относится к области вьиислительной техники, может быть использовано для тестового контроля цифровых блоков, логических схем и диагностики неисправностей и является усовершенствованием устройства по авт.св. № 746553. Целью изобретения является повышение достоверности контроля. Поставленная цель достигается тем, что в известное устройство по авт. св. № 746553 введен блок анализа непредусмотренных неисправностей, содержащий триггер, элемент ИЛИ и элемент И. 1 а.п. ф-лы, 6 ил. (Л с sl 00 со 00

бл

B.S

| Устройство для контроля цифровых блоков | 1978 |

|

SU746553A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-30—Публикация

1985-02-28—Подача