Ю

0д

4ii

to

tC

i4

Устройство относится к автоматике и может найти применение в системах автоматического управления, передачи телеметрической информации, а также в системах связи, использующих многопозиционные многоуровневые составные сигналы,

Целью изобретения является повышение Информативности устройства путем исключения избыточности преобразования .

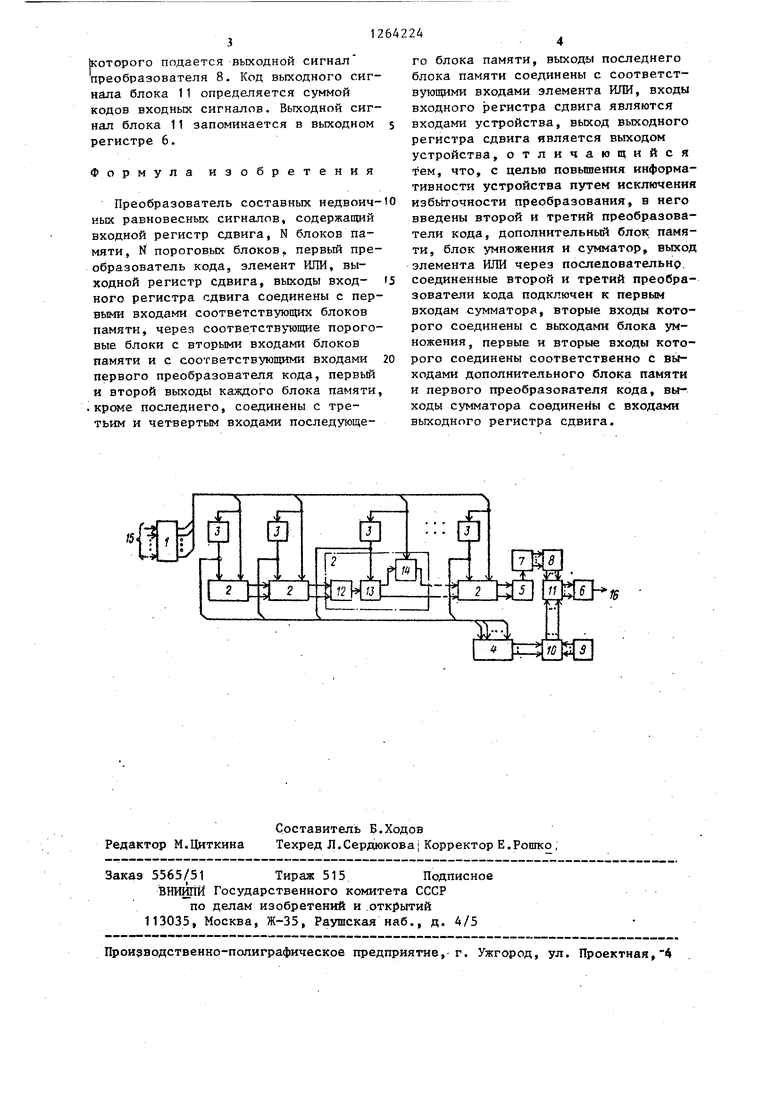

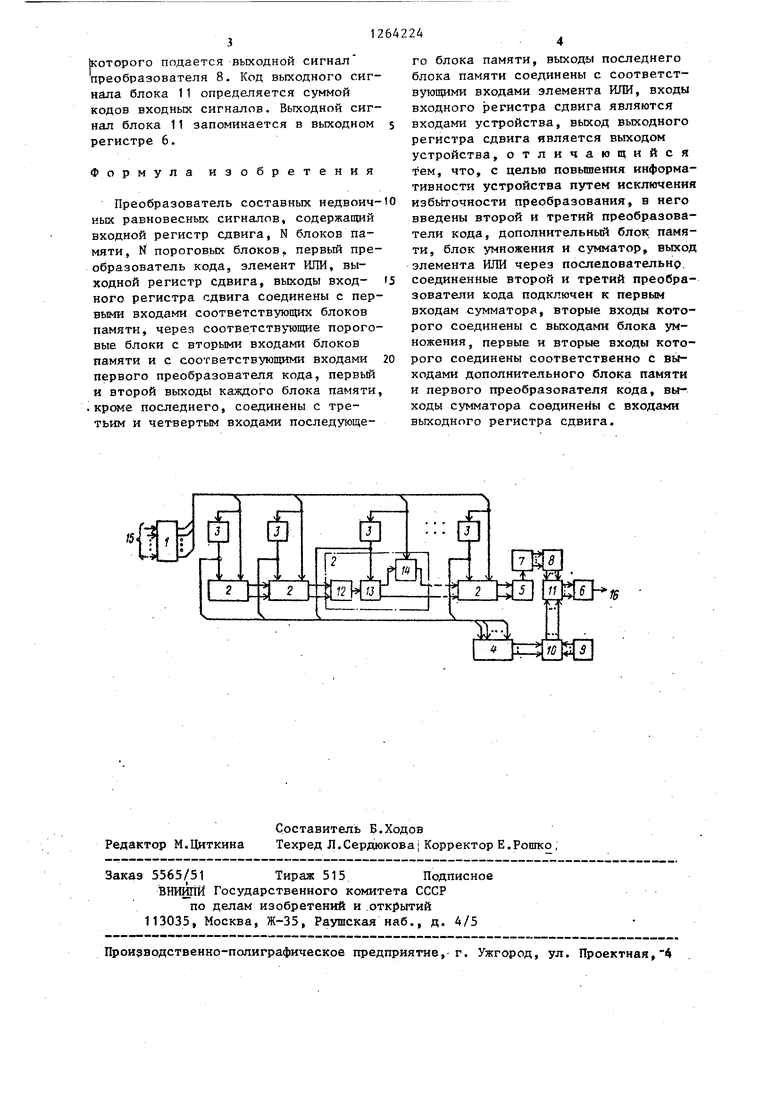

Ца чертеже представлена функциональная схема устройства.

Устройство содержит входной регистр 1 сдвига, N блоков 2 памяти, N пороговых блоков 3, первый преобразователь 4 кода, элемент ИЛИ 5, выходной регистр 6 сдвига, второй и третий преобразователи 7 и 8 кода, дополнительньй блок 9 памяти, блок 10 умножения, сумматор 11, каждый блок 2 памяти состоит из элемента i-UlH 12, переключателя 13 и регистра 14 памяти, входы входного регистра 1 являются входами 15 устройства, выход ВБ1ХОДНОГО регистра 6 является выходом 16 устройства./

Устройство работает следующим образом.

Подлежащий преобразованию исходны составной недвоичньй сигнал вводится ,в регистр 1. Сложный сигнал из регистра 1 подается ца совокупность блоков 2 памяти и на совокупность пороговьк блоков 3. Исходный сигнал преобразуется в п-злементный двоичный составной сигнал с постоянным весом Р (в данном случае постоян-ный вес постоянное количество единичных сигналов) по правилу: если входной сигнал соответствующего порогового блока 3 нулевой, то и на выходе его также нулевой сигнал, в противном случае (вхЬдной сигнал - ненулевой) на выходе этого порогового блока единичный сигнал.

Выходной сигнал порогового блока 3 подается на второй вход соответствующего блока 2 памяти, на один из входов преобразователя 4 кода.

Выходной сигнал порогового блока 3 является управляющим для переключателя 13 J нулевой управляющий сигна соединяет вход переключателя 13 с соответствующим выходом порогового блока .3, единичный управляющий сигнал соединяет вход переключателя 13 .с соответствующим входом регистра

14 памяти (этот вход последовательный). Таким образом, нулевой управляющий сигнал как бы закорачивает регистр 14 памяти, т.е. информация

5 из предьиущего блока 2 памяти через элемент ИЖ 12, переключатель 13 поступает сразу же, минуя регистр 14 памяти, на вход элемента ИЛИ 12 следующего блока памяти. После такой

5 коммутации в Р блоках 2 памяти, соедиренных с теми выходами регистра 1, по которым вьщаются нулевые сигналы, вход соединен с выходом. В остальных же п-р блоках 2 памяти вход соединя5 ется с входом регистра 14 памяти, выход которого подключается к выходу блока 2 памяти.

В результате такой конструкции формируется динамический (по номерам

0 регистров 14 памяти) регистр сдвига, в регистры 14 памяти которого записаны соответствующие ненулевые сигналы исходного сигнала. В целом можно заключить, что в блоках 2 хранит5 ся составной сигнал, состоящий из элементарных сигналов, каждьй из которых может принимать одно.из га значений. Этот сигнал поэлементно выводится через элемент ИЛИ 5 на

0 вход преобразователя 7 кода, в котором из последовательного сигнала преобразуется в параллельный. Этот параллельный сигнал в преобразователе 8 кода так преобразуется, что

5 на его выходе формируется двоичный параллельный сигнал, код которого соответствует коду входного недвоичного сигнала. В преобразователе 4 кода входной двоичный составной сигнал (равновесный) преобразуют в двоичный сигнал.

В преобразователе 4 кода происходит, преобразование кода постоянного веса в полный двоичный код- В преобразователе 7 кода происходит преобразование двоичного последовательного кода в двоичньй параллельньй код. В преобразователе 8 недвоичный код преобразуется в двоичньй.

Этот сигнал подается на одни входы блока 10 умножения, на другие входы которого из дополнительного блока 9 памяти подается соответствующий сигнал. Код выходного сигнала 5 блока 10 определяется произведением кодов входных сигналов. Выходной 1сигнал блока.10 подается на одни Ьходы сумматора 11, на другие входы которого подается выходной сигнал преобразователя 8. Код выходного сигнала блока 11 определяется суммой кодов входных сигналов. Выходной сигнал блока 11 запоминается в выходном регистре 6. е т е н и я Формула изо Преобразователь составных недвоич кых равновесных сигналов, содержащий входной регистр сдвига, N блоков памяти, N пороговых блоков, первый преобразователь кода, элемент ИЛИ, выходной регистр сдвига, выходы входного регистра сдвига соединены с пер выми входами соответствующих блоков памяти, через соответствующие порого вые блоки с вторьми входами блоков памяти и с соответствующими входами первого преобразователя кода, первый и второй выходы каждого блока памяти .кроме последнего, соединены с третьим и четвертым входами последующего блока памяти, выходы последнего блока памяти соединены с соответствующими входами элемента ИЛИ, входы входного регистра сдвига являются входами устройства, выход выходного регистра сдвига является выходом устройства, отличающийся тем, что, с целью повьшения информативности устройства путем исключения избьггочности преобразования, в него введены второй и третий преобразователи кода, дополнительный блок памяти, блок умножения и сумматор, выход элемента ИЛИ через послеповательнр. соединенные второй и третий преобразователи кода подключен к первым входам сумматора, вторые входы которого соединены с выходами блока умножения, первые и вторые входы которого соединены соответственно с выходами дополнительного блока памяти и первого преобразователя кода, выходы сумматора соединены с входами выходного регистра сдвига.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема избыточной информации | 1982 |

|

SU1032470A1 |

| Устройство для преобразования кодов в системе передачи данных | 1982 |

|

SU1086449A1 |

| Устройство для приема и градиентного декодирования избыточных сигналов | 1983 |

|

SU1152016A1 |

| Устройство для приема и преобразования двоичного равновесного кода | 1985 |

|

SU1317661A1 |

| Устройство для преобразования двоичного равновесного кода в полный двоичный код | 1985 |

|

SU1596463A1 |

| Устройство для приема избыточной информации | 1984 |

|

SU1167638A1 |

| Устройство для приема и обработки избыточных сигналов | 1982 |

|

SU1078455A1 |

| Адаптивное устройство для приема избыточной информации | 1981 |

|

SU1012310A1 |

| Устройство для передачи кодовых комбинаций постоянного веса | 1981 |

|

SU982055A1 |

| Устройство распознавания одиночных и групповых составных импульсных сигналов | 1984 |

|

SU1247775A1 |

Устройство относится к автоматике и может найти применение в системах автоматического управления, системах передачи телеметрической информации, а также в системах связи, использующих многопозиционные многоуровневые составные сигналы. В процессе преобразования составных недвоичных равновесных сигналов, в устройстве исключается избыточность преобразованной информации, чем достигается повышение его информативности. Устройство содержит входной регистр сдвига, N блоков памяти, N пороговых блоков, три преобразователя кода, элемент ИЛИ, выходной регистр сдвига, дополнительньш блок памяти, блок умножения и сумматор. Каждый из блоков памяти содержит элемент ИЛИ, переключатель и регистр памяти. 1 ил. (Л с

| .Бородин Л.Ф | |||

| Введение в теорию помехоустойчивого кодирования | |||

| М | |||

| : Сов | |||

| радио, 1968, с,192 | |||

| Устройство для приема кодовых комбинаций постоянного веса | 1981 |

|

SU982054A1 |

Авторы

Даты

1986-10-15—Публикация

1985-01-02—Подача