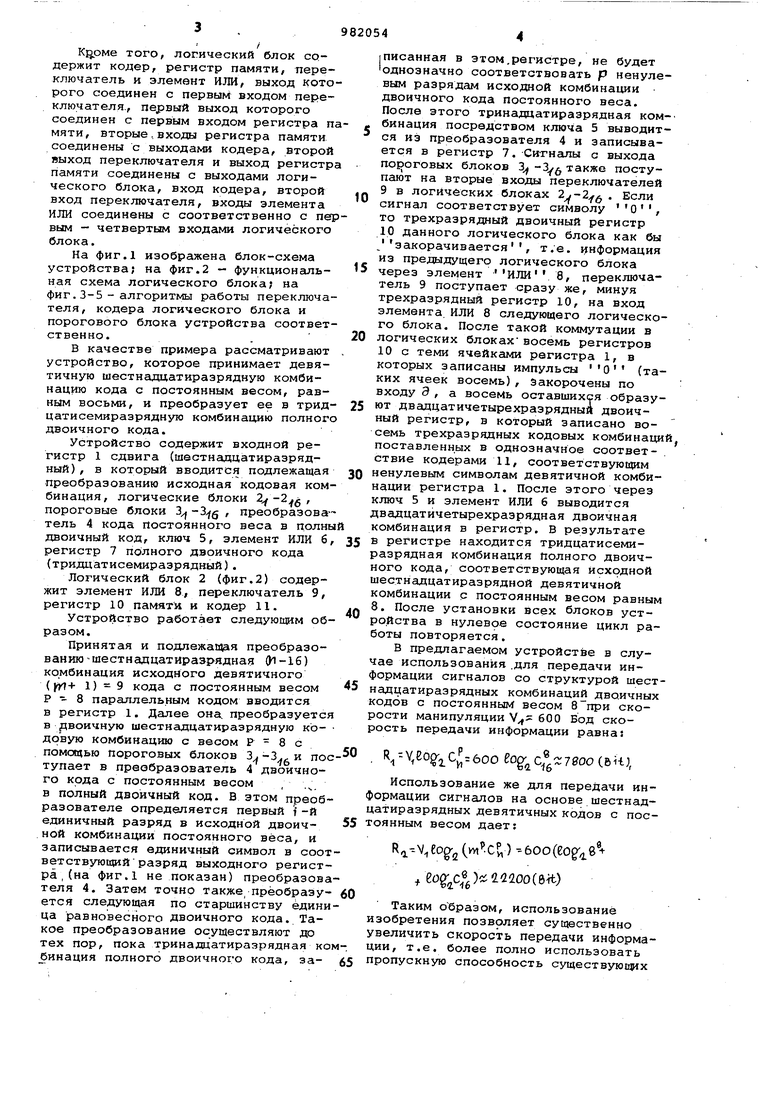

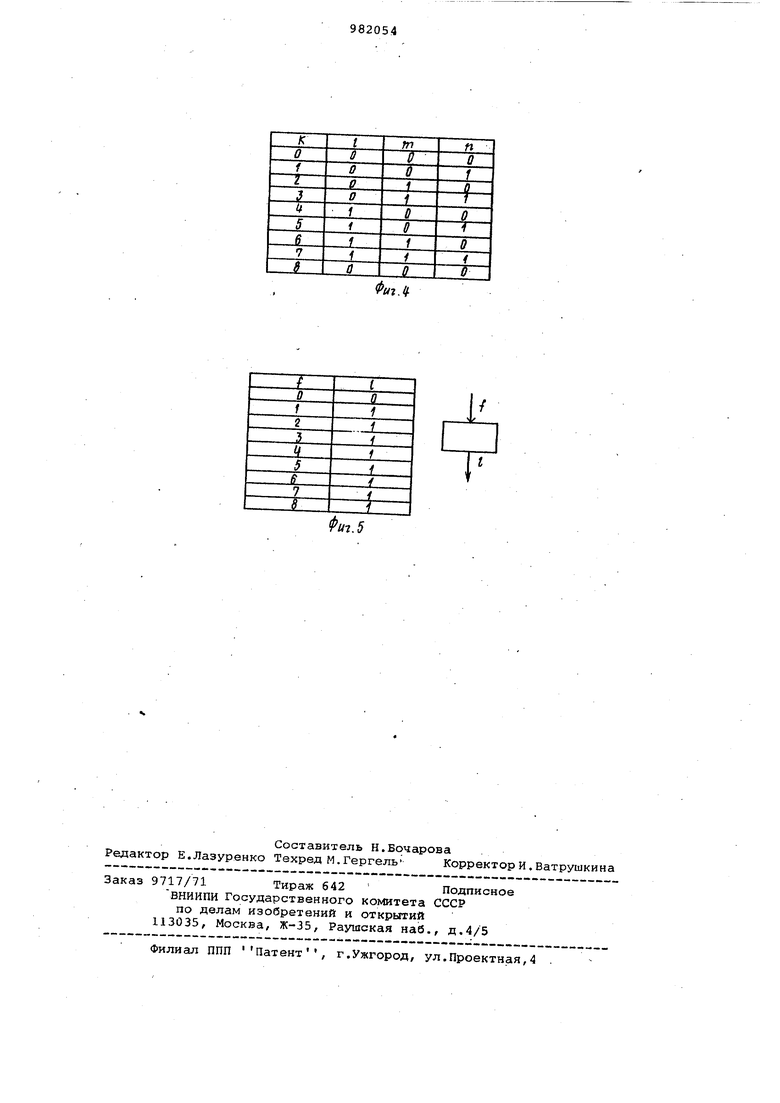

KfjpMe того, логический блок содержит кодер, регистр памяти, переключатель и элемент ИЛИ, выход которого соединен с первым входом переключателя., первый выход которого соединен с первым входом регистра па мяти, вторые,входы регистра памяти соединены с выходами кодера, второй выход переключателя и выход регистра памяти соединены с выходами логического блока, вход кодера, второй вход переключателя, входы элемента ИЛИ соединены с соответственно с пер вым - четвертым входами логического блока. На фиг.1 изображена блок-схема устройства; на фиг.2 - функциональная схема логического блока; на фиг.3-5 - алгоритмы работы переключателя, кодера логического блока и порогового блока устройства соответственно. В качестве примера рассматривают устройство, которое принимает девятичную шестнадцатиразрядную комбинацию кода с постоянным весом, равным восьми, и преобразует ее в тридцатисемиразрядную комбинацию полного двоичного кода. Устройство содержит входной регистр 1 сдвига (шестнадцатиразрядный) , в который вводится подлежащая преобразованию исходная кодовая ком бинация, логические блоки 2 -2 , пороговые блоки 3 1б г преобразователь 4 кода постоянного веса в полны двоичный код, ключ 5, элемент ИЛИ б регистр 7 полного двоичного кода (тридцатисемиразрядный). Логический блок 2 (фиг.2) содержит элемент ИЛИ 8, переключатель 9, регистр 10 памяти и кодер 11. Устройство работает следующим об разом. Принятая и подлежащая преобразованию шестнадцатиразрядная (И-16) комбинация исходного девятичного (Й+ 1) 9 кода с постоянным весом Р - 8 параллельным кодом вводится в регистр 1. Далее она. преобразуетс в рвоичную шестнадцатиразрядную кодовую комбинацию с весом Р 8 с помощью пороговых блоков по тупает в преобразователь 4 двоичного кода с постоянным весом в полный двоичный код. В этом преоб разователе определяется первый if -и единичный разряд в исходной двоичной комбинации постоянного веса, и записывается единичный символ в соо ветствующий разряд выходного регист ра , (на фиг.1 не показан) преобразов теля 4. Затем точно также прёобраЭу ется следующая по старшинству един ца равновесного двоичного кода. Такое преобразование осуществляют до тех пор, пока тринадцатиразрядная к бинация полного двоичного кода, заIписанная в этом,регистре, не будет однозначно соответствовать р ненулевым разрядам исходной комбинации двоичного кода постоянного веса. После этого тринадцатиразрядная комбинация посредством ключа 5 выводится из преобразователя 4 и записывается в регистр 7. Сигналы с выхода по эоговых блоков 3 3/6 также поступают на вторые входы переключателей 9в логических блоках . Если сигнал соответствует символу О, то трехразрядный двоичный регистр 10данного логического блока как бы ,закорачивается, т.е. 1 нформация из предыдущего логического блока через элемент ИЛИ,8, переключатель 9 поступает сразу же, минуя трехраэрядный регистр 10, на вход элемента ИЛИ 8 следующего логического блока. После такой коммутации в логических блокахвосемь регистров 10 с теми ячейками регистра 1, в которых записаны импульсы О (таких ячеек восемь), Закорочены по входу 9, а восемь оставшихся образуют двадцатичетырехразрядныи двоичный регистр, в который записано восемь трехразрядных кодовых комбинаций поставленных в однозначное соответствие кодерами 11, соответствующим ненулевым символам девятичной комбинации регистра 1. После этого через ключ 5 и элемент ИЛИ 6 выводится двадцатичетырехраэрядная двоичная комбинация в регистр. В результате регистре находится тридцатисемиразрядная комбинация полного двоичного кода, соответствующая Исходной шестнадцатиразрядной девятичной комбинации с постоянным весом равным 8. После установки всех блоков устройства в нулевое состояние цикл работы повторяется. В предлагаемом устройстве в случае использования .для передачи информации сигналов со структурой шестнадцатиразрядных комбинаций двоичных кодов с постоянным весом скорости манипуляции V 600 Бод скорость передачи информации равна: . R XBog-j CjJjraoO О - сЛ /еооСвН;, Использование же для передачи информации сигналов на основе шестнадцатиразрядных девятичных коДов с постоянным весом дает: Ra--v,eog-2 ( --боо( /eog-,(eit) Таким образом, использование изобретения позволяет сусцественно увеличить скорость передачи информации, т.е. более полно использовать пропускную способность существующих

каналов связи, что существенно поBt iaeT информативность устройства.

Формула изобретения

1. Устройство для приема кодовых комбинаций постоянного веса, содер ацее pierHCTp сдвига, входы которого соединены с входами устройства, и преобразователь кода постоянного веса в полный двоичный код, от л ичающееся тем, что, с целью повышения информативности устройства, в него введены логические блоки, пороговые блоки, элемент ИЛИ, регистр псшнЬго двоичного кода, ключ, ВЫХОД: ВХОДНОГО регистра сдвига соединены непосредственно с первыми входами логических блоков и через пороговые блоки с вторыми входами соответствующих логических блоков и соответствую1ф1ми входсЫи преоб разователя кода постояиногр веса в полный двоичный код, выход которого соединен с первым входом ключа, первый и второй выходы кгокдого логического блока соединены с третьим и четвертым входами Последующего логического блока, выходы последнего

логического блока соединены через злемент ИЛИ с вторым входом ключа, I выход которого соединен с входом регистра полного двоичного кода, выход которого соединен с выходом 5I устройства.

2. Устройство по П.1-, о т л и чающееся тем, что,логический .блок содержит кодер, регистр памяти, переключатель и злемент ИЛИ, выход

10 которого соединен с первым входом переключателя, первый выход которого соединен с первым входом регистра памяти, вторые входы регистра памяти соединены с выходами кодера, второй

5 выход перключателя и выход регистра памяти соединены с выходами логического блока, вход, кодера, второй вход .переключателя, входы элемента ИЛИ соединены соответственно с первым -

2Q четвертым входами логического блока.

Источники информации, принятые во внимание при экспертизе

1.Бородин Л.Ф. Введение в теорию 25 помехоустойчивого кодирования. М.,

Советское радио, 1968, с. 192.

2.Авторское свидетельство СССР 260963, кл. Н 03 К 13/24, 1968. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи кодовых комбинаций постоянного веса | 1981 |

|

SU982055A1 |

| Устройство для преобразования кодов в системе передачи данных | 1982 |

|

SU1086449A1 |

| Устройство для приема сигналов с избыточностью | 1983 |

|

SU1128281A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1233201A1 |

| Устройство для приема избыточной информации | 1983 |

|

SU1107146A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1218415A1 |

| Устройство для приема избыточной информации | 1984 |

|

SU1167638A1 |

| Устройство для приема и градиентного декодирования избыточных сигналов | 1983 |

|

SU1152016A1 |

| Устройство для приема и градиентного декодирования избыточных сигналов | 1985 |

|

SU1282184A1 |

| Устройство для приема избыточных сигналов | 1983 |

|

SU1107145A1 |

мг. J

Авторы

Даты

1982-12-15—Публикация

1981-01-08—Подача