11

Изобретение относится к электросвязи и может использоваться в системах передачи информации и вычислительной технике.

Цель изобретения - упрощение устройства-.

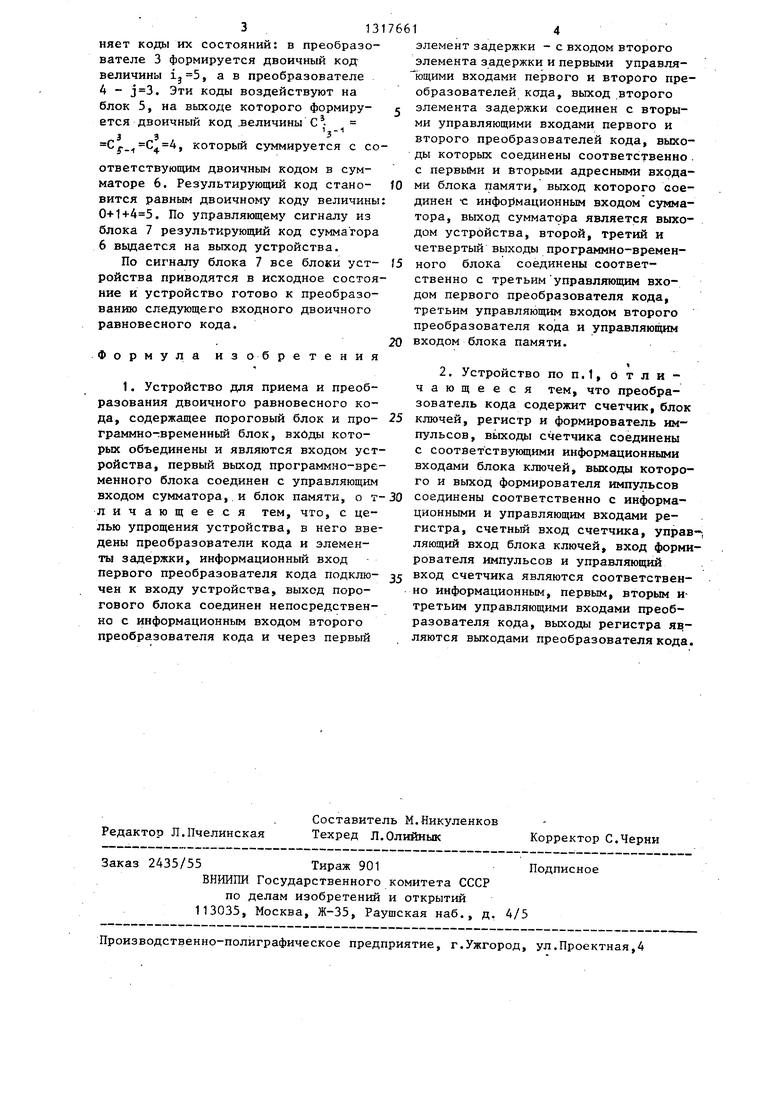

На чертеже представлена структурная схема устройства.

Устройство содержит блок 1 управления, пороговый узел 2, первый 3 и второй 4 преобразователи кода, блок 5 памяти и сумматор 6.

Узел управления образуют программно-временной блок 7 и первый 8 и второй 9 элементы задержки.

Преобразователь кода содержит счетчик 10, блок 11 ключей, регистр 12 сдвига и формирователь 13 импульсов.

Алгоритм функционирования устройства, математически описываемый как

н-Сг , +. . .+С +,.,+С.

ч-- I,--

где Р - номер исходного двоичного равновесного кода (в данном устройстве этот номер - комбинация полного двоичного кода)f К - вес (количество единичных

символов) комбинации исходного двоичного равновесного кода

j - номер соответствующего единичного . символа исходной комбинации (нумерация справа налево);

i- - номер разряда, содержащего j-ю единицу в комбинации двоичного равновесного кода.

Преобразователи 3 и 4 кода предназначены для преобразования входного унарного кода в выходной полый двоичный код.

Преобразователь 3(4) работает следующим образом.

На его информационный вход поступают импульсы, которые подсчитываются счетчиком 10 (параметры блоков преобразователя 3 определяются знач- .ностью Н комбинации исходного кода, а преобразователя 4 - весом К этой комбинации). Количество импульсов, поступающих на вход счетчика 10, отображаются соответствующим двоичным кодом, который параллельно предъявляется блоку 11 ключей. На вход блока 11 ключей, соединенного с входом преобразователя 3(4), пьдается из

76612

блока 1 управления сигнал, которьй открывает ключи блока 11. Через открытые ключи счетчик 10 воздействует на регистр 12, вследствие чего 5 содержание регистра 12 приводится в соответствие двоичному коду счетчика 10. Считывается двоичный код из регистра 12 на выход преобразователя в результате воздействия тактовых 10 импульсов, вырабатываемых формирователем 13 под воздействием управляющего сигнала с входа преобразователя,

Пороговый блок 2 пропускает на 5 свой выход только единичные входные сигналы.

Устройство работает следующим образом.

На вход устройства последователь- 0 но поступают двоячные символы комбинации равновесного кода, например, 10101 (значность , вес ) .

Пусть на вход устройства воздействует первый двоичный символ 1. 5 Он запускает программно-временной блок 7, подается в преобразователь 3 кода, где преобразуется в двоичный код величины i 1, и поступает через пороговый блок 2 в преобразо- 30 ватель 4 кода, где преобразуется в двоичный код величины .

Работой преобразователей 3,4 кода управляет блок 7.

Выходные двоичные коды i 1 и 35 преобразователей 3 и 4 подаются в блок 5,. из которого на вход сумматора 6 считывается двоичный код вел|1чины С: С 0. Далее на вход уст40 ройства поступает сигнал О. Он не проходит на выход порогового блока 2, а только изменяет двоичный код преобразователя 3 на двоичный код величины .

45 Третий входной сигнал 1 изменяет двоичный код преобразов-ателя 4 на двоичный код величины , а двоичный код преобразователя 3 - на двоичный код величины 1 3. Эти коды счи50 тываются в блок 5, на выходе которого формируется двоичный код величины2 2

. Данный код суммируется

н сумматоре 6 с предыдущим слагаемым. 55 Четвертый входной сигнал О изменяет только двоичный код преобразователя 3 на двоичный код величины . Пятый входной сигнал 1, воздействует на преобразователи 3,4 и изме313

няет коды их состояний: в преобразователе 3 формируется двоичный код величины , а в преобразователе 4 - . Эти коды воздействуют на блок 5, на выходе которого формируется двоичный код .величины С

I -1

33

С,., который суммируется с соответствующим двоичньм кодом в сумматоре 6, Результирующий код становится равным двоичному коду величины 0+1+4 5. По управляющему сигналу из блока 7 результирующий код сумматора 6 выдается на выход устройства.

По сигналу блока 7 все блоки устройства приводятся в исходное состояние и устройство готово к преобразованию следующего входного двоичного равновесного кода.

Формула изобретения

1. Устройство для приема и преобразования двоичного равновесного кода, содержащее пороговый блок и про- граммно-:временньш блок, входы которых объединены и являются входом устройства, первый выход программно-временного блока соединен с управляющим входом сумматора, и блок памяти, о т личающееся тем, что, с целью упрощения устройства, в него введены преобразователи кода и элементы задержки, информационный вход первого преобразователя кода подключен к входу устройства, выход порогового блока соединен непосредственно с информационным входом второго преобразователя кода и через первый

Редактор Л.Пчелинская

Составитель М.Никуленков Техред Л.Олийиык

Заказ 2435/55Тираж 901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

14

элемент задержки - с входом второго элемента задержки и первыми управля- ощими входами первого и второго преобразователей кода, выход .второго

элемента задержки соединен с вторыми управляющими входами первого и второго преобразователей кода, выходы которых соединены соответственно . с первыми и вторыми адресными входами блока памяти, выход которого соединен -с инфор мационным входом сумматора, выход сумматора является выходом устройства, второй, третий и четвертый выходы программно-временного блока соединены соответственно с третьим управляющим входом первого преобразователя кода, третьим управляющим входом второго преобразователя кода и управляющим входом блока памяти.

25

30

35

2. Устройство по п.1, отличающееся тем, что преобразователь кода содержит счетчик, блок ключей, регистр и формирователь импульсов, вькоды счетчика соединены с соответствующими информационными входами блока ключей, выходы которого и выход формирователя импульсов соединены соответственно с информационными и управляющим входами регистра, счетный вход счетчика, управ-; ляющий вход блока ключей, вход формирователя импульсов и управляющий вход счетчика являются соответственно информационным, первым, вторым и- третьим управляющими входами преобразователя кода, выходы регистра яц- ляются выходами преобразователя кода.

Корректор С.Черни

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема избыточной информации | 1983 |

|

SU1107146A1 |

| Адаптивное устройство для обработки избыточной информации | 1982 |

|

SU1062752A1 |

| Устройство для приема и обработки избыточных сигналов | 1982 |

|

SU1078455A1 |

| Устройство для приема и градиентного декодирования избыточных сигналов | 1983 |

|

SU1152016A1 |

| Устройство для преобразования двоичного равновесного кода в полный двоичный код | 1985 |

|

SU1596463A1 |

| Устройство для приема избыточных сигналов | 1989 |

|

SU1695353A1 |

| Устройство для преобразования двоичного равновесного кода в полный двоичный код | 1985 |

|

SU1543549A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1193713A1 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ | 1998 |

|

RU2174699C2 |

| Устройство для приема избыточной информации | 1984 |

|

SU1167638A1 |

Изобретение относится к электросвязи и может использоваться в системах передачи информации и вычислительной технике. Целью изобретения является упрощение устройства. Устройство преобразует двоичный равновесный код в полный двоичный код и содержит узел 1 управления, пороговый блок 2, преобразователи-3,4 кода, блок 5 памяти и сумматор 6. Узел управления содержит программно- временной блок 7 и элементы 8,9 задержки. Преобразователь кода содержит счетчик 10, блок 11 ключей, регистр 12 сдвига и формирователь 13 импульсов. 1 з.п.ф-лы, 1 ил. С (Л

| Устройство для приема кодовых комбинаций постоянного веса | 1981 |

|

SU982054A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Устройство для приема и градиентного декодирования избыточных сигналов | 1985 |

|

SU1282184A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1987-06-15—Публикация

1985-12-03—Подача