Изобретение относится к электросвязи и может использоваться в системах передачи цифровой информации и вычислительных системах..

Целью изобретения является повышение быстродействия устройства.

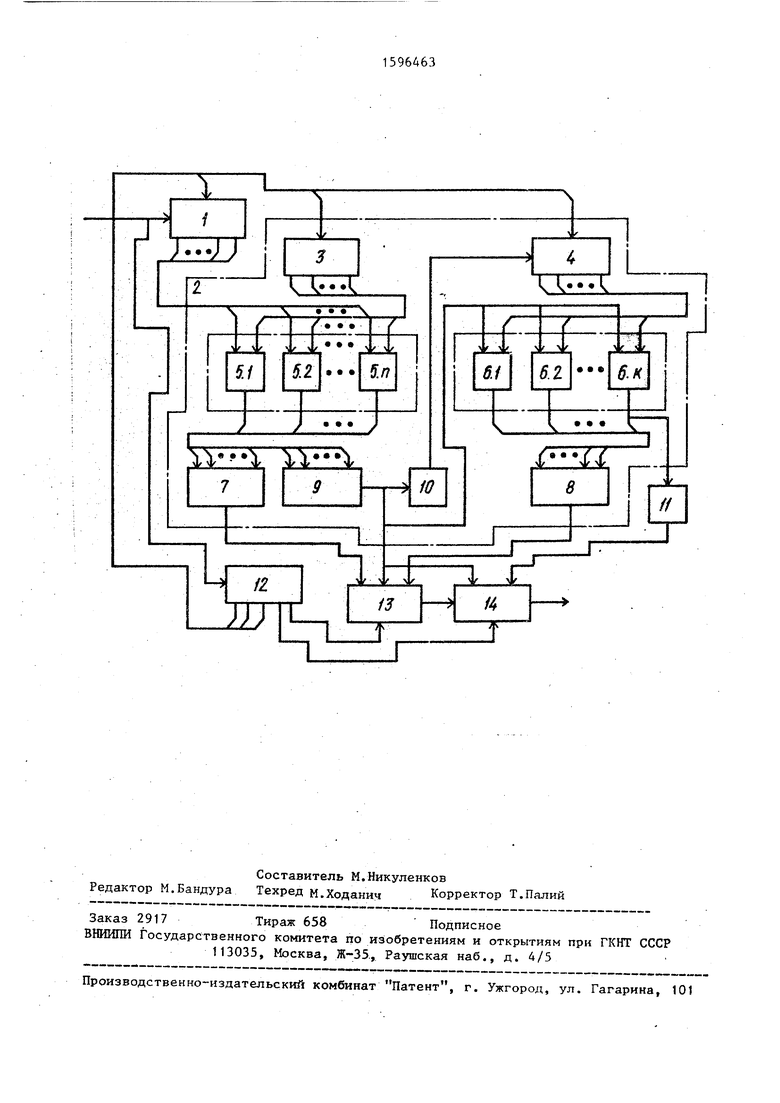

На чертеже представлена структурная схема устройства. Устройство содержит регистр 1 сдвига, шифратор 2, выполненный на первом, втором распределителях 3, 4 импульсов, элементах И 5.1-5.п, 6.16.k первой, второй групп, первом, втором преобразователях 7, 8 кода, элементе ИЛИ 9 и первом эдеме.нте 10 задержки, второй элемент 11 задержки программно-временной блок 12, блок 13 памяти и cyfiMaTOp 14. Например, значность исходного код , вес (т.е. в каждой кодовой комбинации исходного равновесного кода из пяти символов три являются .единичными, а два - нулевыми). Тогда (совотсупность кодовых комбинаций исходного кода составит 00111, 01011 01101, 01110, 10011, 10011, 10101,, 10110, 11001, 11010, 11100. Рассмотрим комбинацию 00111, Будем считать, что в данной комбинации единицы перенумерованы справа налево и все единицы располагаются на своих нулевых позициях. В комбинации 11100 все единицы находятся на своих вторых позициях В комбинации, например, 10101 пер вая единица находится на нулевой позиции, вторая единица на первой позиции, последняя третья единица на второй позиции. Таким образом, каждую из исходных комбинаций можно однозначно представить своими позициями единичных символов. При этом образуется совокупность уже не Н-значных, а 1С-значных (Н-К+О-ичных комбинаций (а, а.,а ): 000, 100, 110, 111,200 210, 211, 222. Анализ этой совокуп.ности показывает, что ее структура соответствует структуре позиционной системы счисления, для которой номер каждого числа (в этом случае целесообразно говорить не о комбинации, а о числах) определяется как jT, -Uj-/где . Cji - число сочетаний из а по Ь; j - номер единицы в исходной комбинации двоичного Р новесного кода; .{ цифра соответствую щего числа полученной системы счисления. Однако вследствие того, что a--j i, где i. - номер позиции в комбинации исходного равновесного кода (нумерация справа налево и начинается с позиции 1, заканчивается позицией Н), в котором находится j-я единица. Выражение (1) может быть представлено в виде : Последнее выражение и определяет алгоритм функционирования нового устройства. Причем в зависимости от тогб, в какой системе счисления будут представлены величины j, i,. К, а также число сочета ний и сумма, соответственно будет осуществлен переход от двоичной комбинации равновесного кода к комбинации (числу) этой системы счисления. Шифратор работает следующим образом. Программно-временной блок 12 формирует и вьщает сигнал начальной установки в распределители 3, 4 импульсов. На первых вьгходах распределителей 3, 4 постоянно присутствуют единичные сигналы. Выходные сигналы распределителей 3, 4 подаются на вторые входы элементов И 5, 6. На первые входы элементов И 5 поступают выходные сигналы регистра 1. Например, в регистре 1 хранится комбинация 10101 равновесного кода, т.е. на первом, третьем и пятом выходах регистра 1 присутствуют единичные сигналы. Тогда на выходе первого элемента И 5.1 формируется единичный сигнал, который поступает на вход элемента ИЛИ 9 и преобразователя 7 кода, осуществляющего преобразование входного двоичного позиционного кода в выходной двоичный полный код. в результате на входах преобразователя 7 присутствует комбинация 00001 позиционного двоичного кода, которая йреобразуется в комбинацию 001 полного двоичного кода. Эта комбинация соответствует . Входной единичный сигнал элемента ИЛИ 9 проходит на его выход и участвует в следующих преобразованиях. Во-первых, он подается на первые , входы элементов И 6. При этом на обоих входах элемента И 6.1 присутс вуют единичные сигналы, на его выходе формируется единичный сигнал. ;На входах преобразователя 8 формиру ется комбинация 001 позиционного ко да, а на его выходах - комбинация 0 двоичного полного кода. Эта комбинация определяет двоичный код . Во-вторых, он приводит в исходное состоянле блок 13 памяти. В сумматоре 1 А этот сигнал разрешает сложение соответствующих кодов. В-третьих, он задерживается на определенное время в элементе 10 задержки и, посту пая на вход распределителя 4 импульсов, изменяет выходное состояние последнего. В итоге единичный сигнал |вьщается уже не с первого, а со втоiporo выхода распределителя 4. После этого в соответствующий момент времени из программно-временного блока 12 в распределитель 3 посту пает управляющий сигнал, который, изменяя выходное состояние распределителя 3, приводит к формированию единичного сигнала на втором его выходе. . Во второй ячейке памяти регистра 1 единичного символа нет, поэтому на выходе элементов И 5 присутствует нулевая комбинация, на выходе эле ментов И 6 также нулевая комбинация. Нулевыми являются и выходные комбинации преобразователей 7, 8, При этом управляющий сигнал с выхода эле мента ИЛИ 9 на выход шифратора 2 не вьщается. После этого в соответствующий момент времени на управляющий вход распределителя 3 импульсов с выхода блока 12 подается третий управлякяцнй сигнал, который приводит к тому, что .единичный сигнал формируется только на 3-м выходе распределителя 3. Так как в 3-й ячейке памяти регистра t имеется единичный сигнал, на вькоде третьего элемента И 5.3 формируется единичный сигнал. На входах преобразователя 7 будет сформирована комбинация 00100, которая преобразуется в выходную комбинацию 011, соответствукидую двоичному коду номера позиции второго единичного символа исходной комбинации. Одновременно выходной единичный сигнал элемента И 5.3 проходит элеMeHT ИЛИ 9 и поступает на выход шиф ратора 2, соедингнный с блоком 13 памяти и сумматором 14, на первые входы элементов И 6 и на вход элемента 10 задержки, что приводит к появлению единичного сигнала на выходе второго элемента И 6.2. На выходе второго элемента И 6.2 появляется единичный сигнал, так что на входе преобразователя 8 формируется двоичный позиционный код 010, который преобразуется в двоичный выходной код преобразователя 8, соответствующий двоичному коду номера второй единицы в исходной комбинации. После этого на выходе элемента 10 задержки появляется единичный сигнал, который, воздействуя на распределитель 4 импульсов, приводит к появлению на его третьем выходе единичного сигнала . Далее в соответствуниций момент времени выходной управлякнций сигнал программно-временного блока 12 воздействует на распределитель 3 и единичный сигнал вьщается с его четвертого выхода. В четвертой ячейке памяти регистра 1 единичного сигнала нет, поэтому выходной сигнал преобразователя 7 нулевой, нулевым сигналом является и выходной сигнал преобразователя 8. Управляющий сигнал на выходе элемента ИЛИ 9 отсутствует. В соответствующий момент времени единичный сигнал появляется на последнем, пятом выходе распределителя 3 импульсов (количество выходов распределителя 3 определяется значностью входной комбинации равновесного кода) . Вследствие того, что в пятой ячейке памяти регистра 1 хранится единичный сигнал, на выходе пятого элзмента И 5.5 формируется единичный сигнал, который определяет входную комбинацию 10000 для преобразователя 7 и проходит на выход элемента ИЛИ 9. В преобразователе 7 осуществляется преобразование входной двоичной комбинации в комбинацию 101, соответствующую двоичному номеру позиции третьего единичного символа исходной комбинации. Выходной сигнал элемента ИЛИ 9 подается на выход шифратора 2, на вход элемента 10 задержки, на соответствующие входы элементовг И 6. Пр этом на выходе последнего, третьего элемента И 6.3 появляется единичный управляющий сигнал, который поступает на выход шифратора 2, соеди

ненный с входом элемента 11 задержки. Кроме того, этот единичный сигнал .определяет входную двоичную комбинацию 100 преобразователя, который преобразует ее в комбинацию 011, соответствукяцую двоичному коду номера третьего единичного символа исходной комбинации, которая выдается на соответствующий выход шифратора 2.

Далее ьа выходе элемента 10 задержки появляется управляющий сигнал, который распределителем 4 не воспринимается.

В соответствующий момент времени по управляющему сигналу из программно-временного блока 12 распределители 3 , 4 импульсоб приводятся в исходное состояние, и устройство готово к обработке следующей исходной комбинации входного регистра.

При поступлении на соответствующие входы блока 13 тамяти двоичных кодов ii и j из соответствующей ячейки памяти считывается двоичный код, определяющий величину числа сочетаний из (i - 1) по j. Если вес исходной комбинации равен , то первым на выходе блока 13 появится код Ct . , вторым - С , ,, третьим f Э f

«3- Например, для исходной комбинации

10101 эта последовательность имеет вид 0000, так как

г г

С. О, -1 1-«

второй - 0001, так как

Г

5- С 1,

чпоследний - 0010, так как

г г С

4. fj-r y-i 4

Сумматор 14 стробируется выходным сигналом элемента 9 ИЖ и осуществляет суммирование двоичных кодов, поступающих с выхода блока 13 памяти.

Например, если выходные коды блока 13 0000, 0001, 0100, то по управляющему сигналу с выхода элемента задержки на выходе сумматора 14 формируется код 0101 суммы входных кодов и вьщается на выход устройства.

Устройство для преобразования двоичного равновесного кода работает следующим образом.

: Исходная, подлежащая преобразованию, двоичная кодовая комбинация постоянного веса поступает на вход устройства, запускает программновременной блок 12 и запоминается в регистре 1.

В определенный момент времени в результате воздействия управляющих сигналов, вьфабатьтаемьк в блоке 12 шифратор 2/осуществляет последрвательное формирование на выходах двоичных кодов порядковых номеров единичных символов и их позиций в исходной комбинации. При этом каждая пара кодов (код i ) позиции единицы и код j порядкового номера единицы) стробируется. управляющим сигналом шифратора 2 и подается на соответстГвующие входы блока 13, который выI дает двоичный код числа сочетаний из (ij-1) по j на вход сумматора 14, В сумматоре 14 в моменты времени, определяемые стробирую1 ми импульсами шифратора 2, суммируются двоичные коды, подаваемые на сумматор 14 из блока 13. Результирующий код стробируется сигналом шифратора 2 после его I задержки в элементе 11. Код 0101 суммы (для рассматриваемого примера) по стробирующему сигналу выдается на выход устройства.

Далее все блоки устройства приводятся в исходное состояние и осуществляется преобразование следующей комбинации равновесного кода.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема и преобразования двоичного равновесного кода | 1985 |

|

SU1317661A1 |

| Устройство для преобразования кодов в системе передачи данных | 1982 |

|

SU1086449A1 |

| Устройство для преобразования двоичного равновесного кода в полный двоичный код | 1985 |

|

SU1543549A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU888102A1 |

| Преобразователь двоичного кода в модулярный код | 1985 |

|

SU1267624A1 |

| Преобразователь двоичного кода в трехпозиционный код | 1984 |

|

SU1317675A1 |

| Преобразователь двоичных кодов в двоично-десятичные | 1984 |

|

SU1200428A1 |

| Преобразователь двоичного кода в двоично-десятичный масштабированный код | 1978 |

|

SU767750A1 |

| Преобразователь параллельного комбинаторного кода в позиционный код | 1982 |

|

SU1035597A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU993244A1 |

Изобретение относится к электросвязи и может использоваться в системах передачи цифровой информации и вычислительных системах. Цель изобретения - повышение быстродействия устройства. Устройство содержит программно-временной блок, первый выход которого соединен с управляющим входом регистра, информационный вход регистра является входом устройства, выходы регистра соединены с первыми входами соответствующих элементов И первой группы, выходы которых соединены с соответствующими входами элемента ИЛИ и элементы И второй группы. В устройство дополнительно введены распределители импульсов, преобразователи кода, элементы задержки, блок памяти и сумматор. 1 ил.

| Авторское свидетельство СССР ,№ 982055, кл | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-09-30—Публикация

1985-11-26—Подача