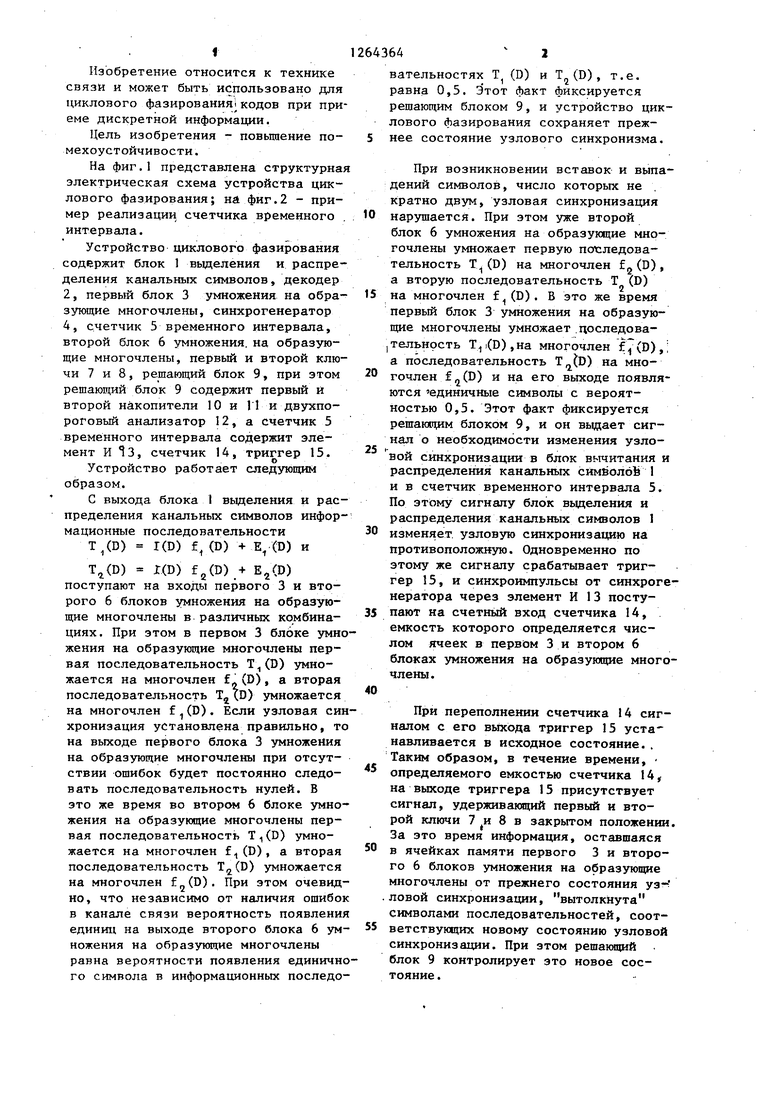

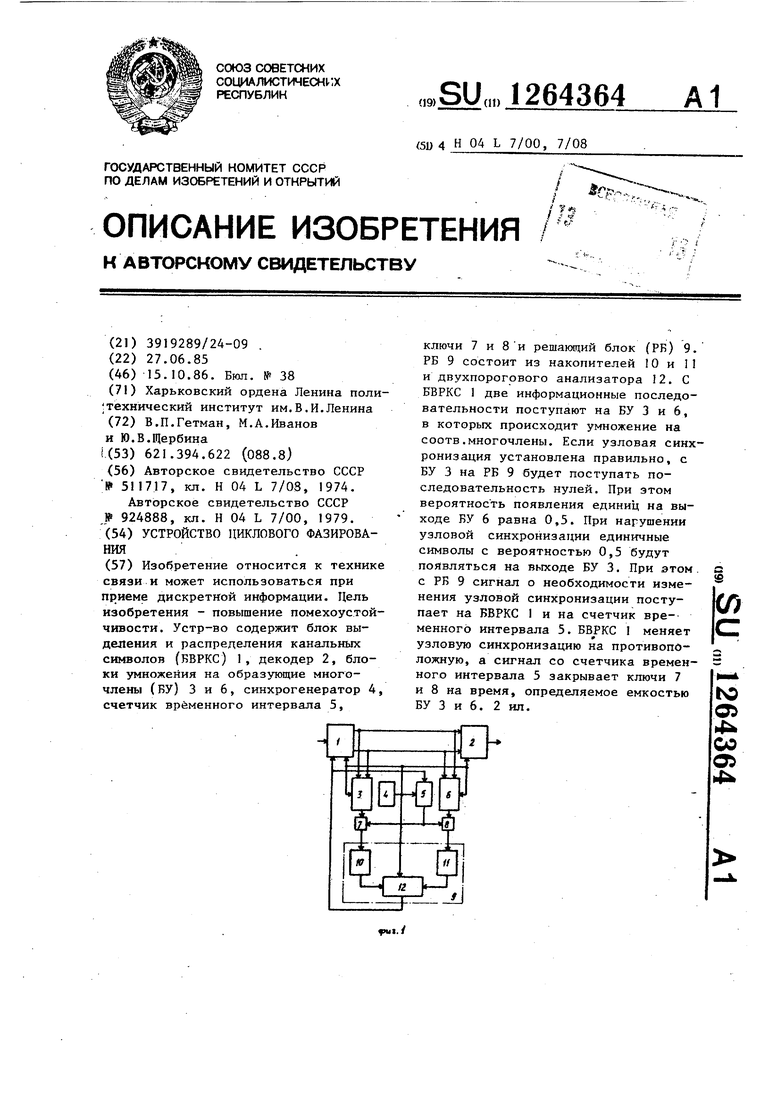

f Изобретение относится к технике связи и может быть использовано для циклоного фазирования кодов при при еме дискретной информации. Цель изобретения - повышение помехоустойчивости. На фиг.1 представлена структурна электрическая схема устройства циклового фазирования; на фиг.2 - пример реализации счетчика временного интервала. Устройство циклового фазирования содержит блок 1 выделения и распределения канальных символов, декодер 2, первый блок 3 умножения на образующие многочлены, синхрогенератор 4, счетчик 5 временного интервала, второй блок 6 умножения, на образующие многочлены, первый и второй ключи 7 и 8 , решающий блок 9, при этом решающий блок 9 содержит первый и второй накопители 10 и 11 и двухпороговый анализатор 12, а счетчик 5 временного интервала содержит элемент И ЧЗ, счетчик 14, триггер 15. Устройство работает следующим образом. С выхода блока 1 выделения и распределения канальных символов инфор мационные последовательности T(D) I(D) f (D) -t- E (D) и T,,(D) Г(В) fg(D) + E(D) поступают на входы первого 3 и второго 6 блоков умножения на образующие многочлены в различных комбинациях. При этом в первом 3 блоке умн жения на образующие многочлены первая последовательность Т;, (D) умножается на многочлен ), а вторая последовательность TjCD) умножается на многочлен f , (D). Если узловая си хронизация установлена правильно, т на выходе первого блока 3 умножения на образующие многочлены при отсутствии ощибок будет постоянно следовать последовательность нулей. В это же время во втором 6 блоке умно жения на образующие многочлены первая последовательность T,(D) умножается на многочлен f.,(D), а вторая последовательность Т, (D) умножается на многочлен ,(0). При этом очевид но, что независимо от наличия ощибо в канале связи вероятность появлени единиц на выходе второго блока 6 ум ножения на образующие многочлены равна вероятности появления единичн го символа в информационных последо 64 2 вательностях Т (D) и 1(0), т.е. равна 0,5. Этот факт фиксируется решающим блоком 9, и устройство циклового фазирования сохраняет прежнее состояние узлового синхронизма. При возникновении вставок и выпадений символов, число которых не кратно двум, узловая синхронизация нарушается. При этом уже второй блок 6 умножения на образующие многочлены умножает первую последовательность Т(D) на многочлен f (D), а вторую последовательность Т (D) на многочлен f(D). В это же время первый блок 3 умножения на образующие многочлены умножает .доследоваТельность (D),Ha многочлен f|(D),; а последовательность на многочлен fn(D) и на его вьпсоде появляются единичные символы с вероятностью 0,5. Этот факт фиксируется решающим блоком 9, и он выдает сигнал о необходимости изменения узловой синхронизации в блок вычитания и распределения канальных символов 1 и в счетчик временного интервала 5. По этому сигналу блок выделения и распределения канальных символов 1 изменяет узловую синхронизацию на противоположную. Одновременно по этому же сигналу срабатывает триггер 15, и синхроимпульсы от синхрогенератора через элемент И 13 поступают на счетный вход счетчика 14, емкость которого определяется числом ячеек в первом 3 и втором 6 блоках умножения на образующие многочлены. При переполнении счетчика 14 сигналом с его выхода триггер 15 уста навливается в исходное состояние.. Таким образом, в течение времени, определяемого емкостью счетчика 14 на выходе триггера 15 присутствует сигнал, удерживающий первый и второй ключи 7 и 8 в закрытом положении. За это время информация, оставшаяся в ячейках памяти первого 3 и второго 6 блоков умножения на образующие многочлены от прежнего состояния ловой синхронизахщи, вытолкнута символами последовательностей, соответствующих новому состоянию узловой синхронизации. При этом решаниций блок 9 контролирует это новое состояние . 3 Формула изобретени Устройство цикловоги фазирования содержащее блок выделения и распределения канальных символов, вход ко торого является входом устройства, декодер,выход которого является выходом устройства, и решакиций блок, выход которого соединен с управляющим входом блока выделения и распре деления канальных символов, первый , и второй выходы которого соединены соответственно с первым и вторым- вхо дами декодера, отличающееся тем, что, с целью повьшения помехоустойчивости, в устройство введень) первый и второй блоки умножения на образующие многочлены, пер вый и второй ключи,- синхрогенератор и счетчик временного интервала, при 64 этом выходы блока выделегтня и распределения канальных символов соединены соответственно с первыми и вто рыми информационными входами первого и второго блоков умножения на образуюрще многочлены, выходы которых через соответствующие первый и второй ключи соединены с входами решающего блока, выход синхрогенератора соединен с синхровходами решающего блока, первого и второго блоков умножения на образующие многочлены, блока выделения и распределения канальных символов, декодера и счетчика временного интервала, выход которого соединен с управляющими входами первого и второго ключей, при этом выход решающего бЛока также соединен с управляющим входом счетчика временного интервала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для узловой синхронизации сверточного декодера | 1979 |

|

SU924888A1 |

| Пороговый декодер сверточного кода | 1981 |

|

SU1046958A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ НА ОСНОВЕ МАТРИЧНОЙ ОБРАБОТКИ КАНОНИЧЕСКОЙ РЕКУРРЕНТНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ, СФОРМИРОВАННОЙ МОДУЛЬНЫМ ГЕНЕРАТОРОМ | 2024 |

|

RU2831303C1 |

| УСТРОЙСТВО ДИВЕРГЕНТНОГО ДЕКОДИРОВАНИЯ СЕГМЕНТОВ ЛИНЕЙНОЙ РЕКУРРЕНТНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2023 |

|

RU2820053C1 |

| Пороговый декодер сверточного кода | 1989 |

|

SU1667264A1 |

| Система передачи и приема дискретной информации | 1980 |

|

SU944146A1 |

| Сверточный кодек с алгоритмом порогового декодирования | 1985 |

|

SU1327296A1 |

| Устройство для узловой синхронизации в системах передачи информации | 1981 |

|

SU960896A1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1994 |

|

RU2085046C1 |

| ВЕДОМСТВЕННАЯ СИСТЕМА ДВУХСТОРОННЕЙ ВЫСОКОСКОРОСТНОЙ РАДИОСВЯЗИ С ЭФФЕКТИВНЫМ ИСПОЛЬЗОВАНИЕМ РАДИОЧАСТОТНОГО СПЕКТРА | 2016 |

|

RU2650191C1 |

г-F

cpue.Z

| Способ цикловой синхронизацмм при двоичном сверточном кодировании | 1974 |

|

SU511717A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Авторское свидетельство СССР ,№ 924888, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-10-15—Публикация

1985-06-27—Подача