ьо

s|

ю

со со

бой разрядное изображение f и а при (п 4 п-разрядность представления информации);

1 Т

при 1

« 5 J . . .

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный вычислитель | 1985 |

|

SU1265765A1 |

| Вычислительное устройство | 1985 |

|

SU1291978A1 |

| Устройство для вычисления модуля вектора | 1983 |

|

SU1111156A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1332313A1 |

| Матричный вычислитель | 1985 |

|

SU1247864A1 |

| Матричный вычислитель | 1985 |

|

SU1283791A1 |

| Матричный вычислитель функции @ | 1984 |

|

SU1216779A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Устройство для деления | 1986 |

|

SU1381492A1 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

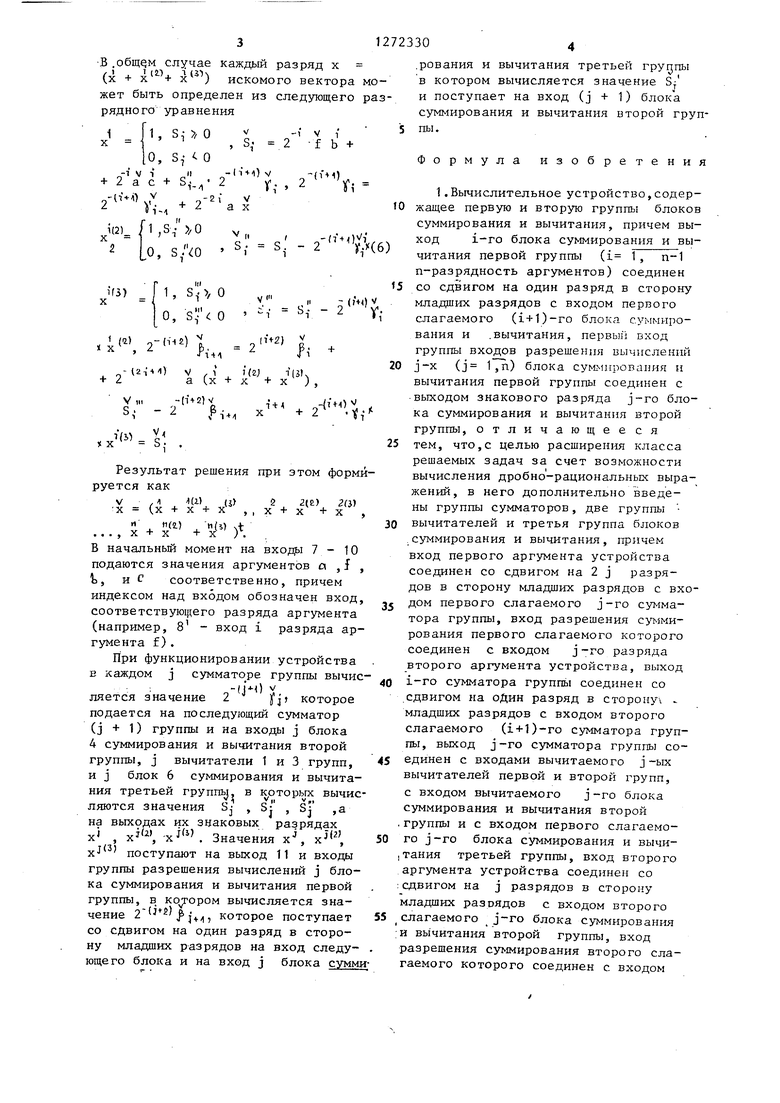

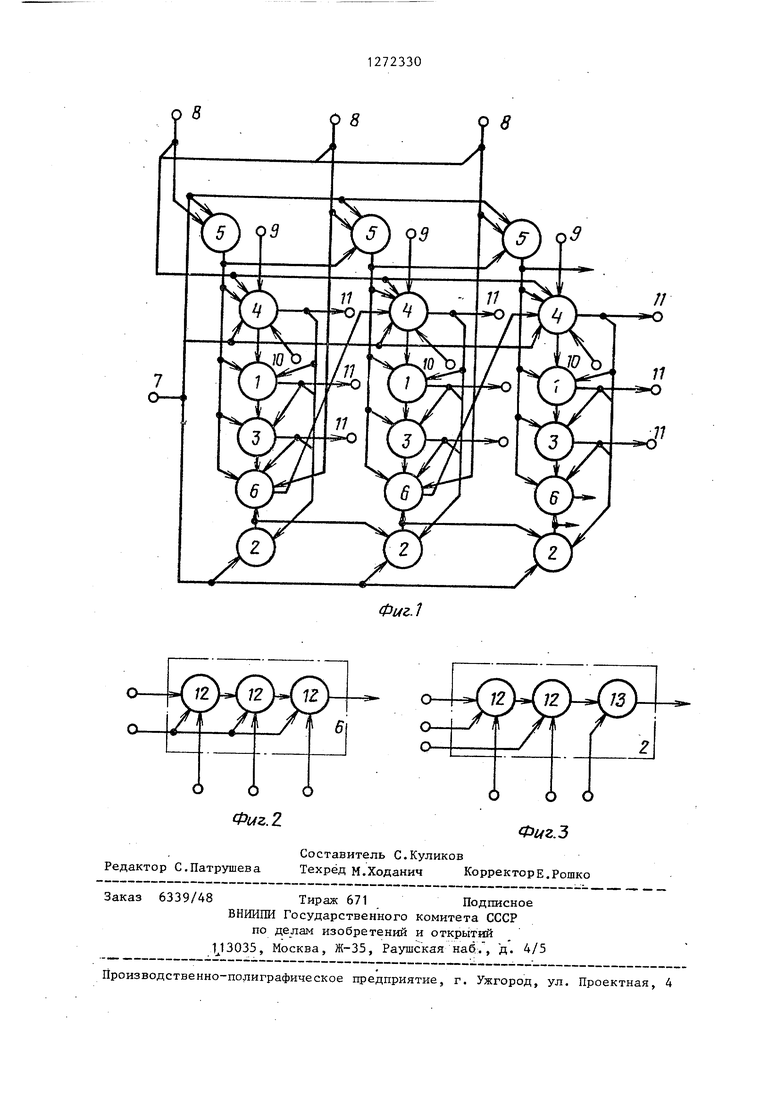

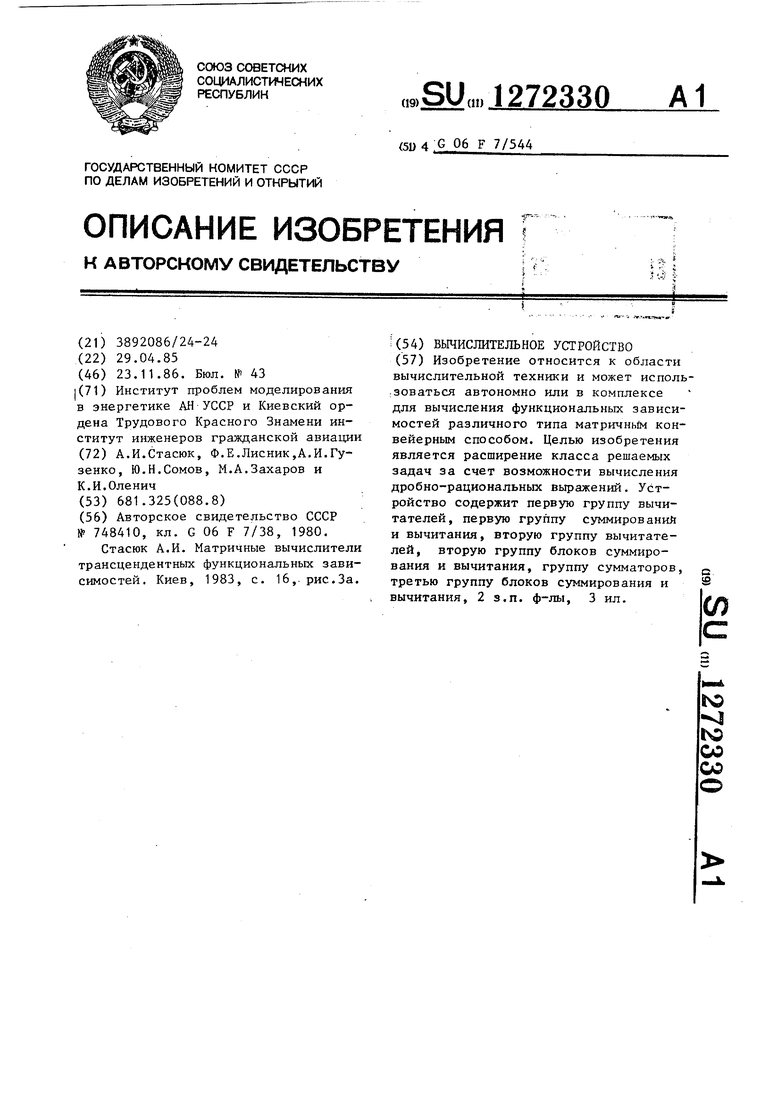

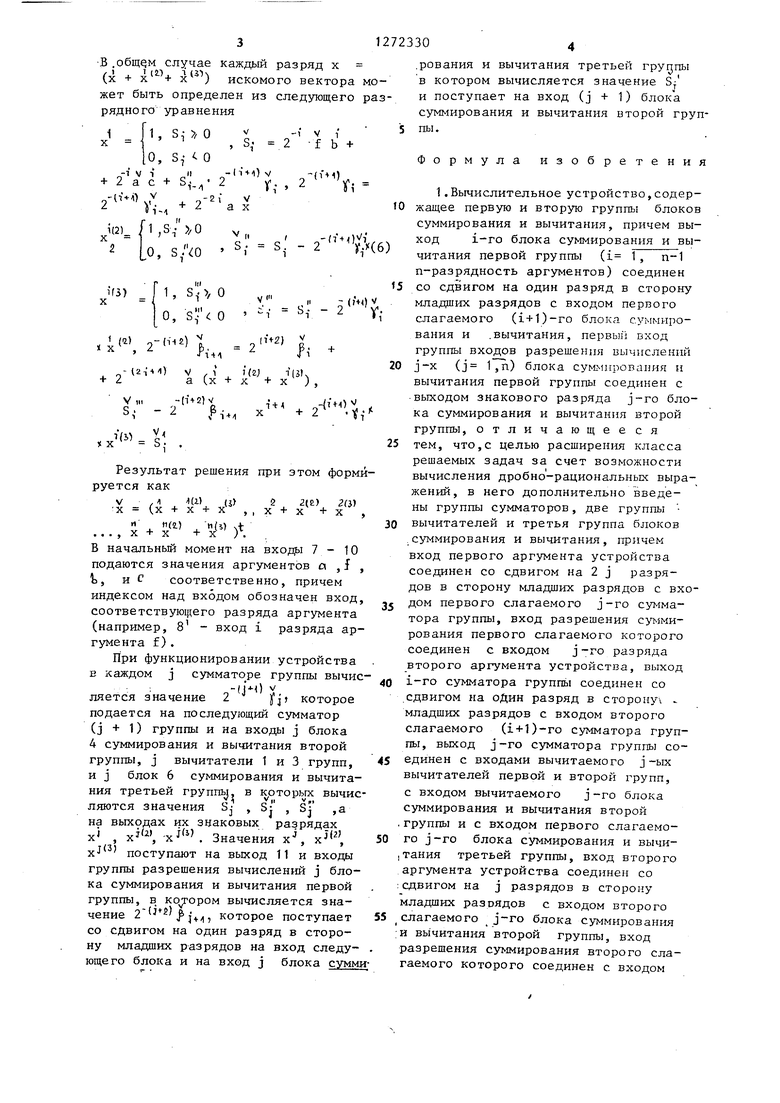

Изобретение относится к области вычислительной техники и может исполь.зоваться автономно или в комплексе для вычисления функциональных зависимостей различного типа матричнь м конвейерным способом. Целью изобретения является расширение класса решаемых задач за счет возможности вычисления дробно-рациональных выражений. Устройство содержит первую группу вычитателей, первую группу суммирований и вычитания, вторую группу вычитателей, вторую группу блоков суммирования и вычитания, группу сумматоров, с. третью группу блоков суммирования и вычитания, 2 з.п. ф-лы, 3 ил. (Л

1

X

л

X

, V -(-М)

2 а 2. 2 X

(51

j-го разряда третьего аргумента уст ройства, вход первого аргумента устройства соединен со сдвигом на j разрядов в сторону младших разрядов с входом третьего слагаемого j-ro блока суммирования и вычитания второй группы, вход . разрешения суммирования третьего слагаемого которого соединен с входом j-ro разряда четвертого- аргумента устройства, выход j-ro блока суммирования и вычитания второй группы соединен с входо уменьшаемого j-ro вычитателя первой группы, вход разрешения вычитания которого соединен с выходом знакового разряда j-ro блока суммирования и вычитания, второй группы, выход jго вычитателя первой группы соединен сВХОДОМ уменьшаемого j-ro вычитателя второй группы, вход разрешения вы читания которого соединен с выходом знакового разряда j-ro вычитателя первой группы, информационный выход j вычитателя второй группы соединен с входом первого слагаемого jго блока суммирования и вычитания третьей группы, вход вычитаемого которого соединен с выходом j-ro блока суммирования и вычитания первой группы, вход разрешения вычитания i-ro блока суммирования и вычитания соединен с входом (i+1)-ro разряда второго аргумента устройства, вход разрешения суммирования j-ro блока суммирования и вычитания третьей группы соединен с выходом знакового разряда j-ro вычитателя второй группы, выход i-ro блока суммирования и вычитания соединен с входом первого слагаемого (i+1)-ro блока суммирования и вычитания второй группы, второй и третий входы группы входов разрешения вычислений j-ro блока суммирования и вычитания соединены с выходами знаковых разрядов j-ro вычитателя соответственно первой и второй групп, вход первого аргумента устройства соединен со сдвигом на (2J +1)-й разряд в сторону млад.ших разрядов с входом второго елагаемого j-ro блока суммирования и вычитание первой группы, выход знаковых разрядов блока суммирования и вычитания, j-ro вычитателя первой группы j-ro вы-читателя третьей группы являются выходами результата в разрядном представлении.

| Устройство для деления двоичных чисел | 1978 |

|

SU748410A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Стасюк А.И | |||

| Матричные вычислители трансцендентных функциональных зависимостей | |||

| Киев, 1983, с | |||

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| рис.За | |||

| i | |||

Авторы

Даты

1986-11-23—Публикация

1985-04-29—Подача