{

Изобретение, относится к вычисл}гтельной технике и может найти применение в цифровых устройствах высокого быстродействия.

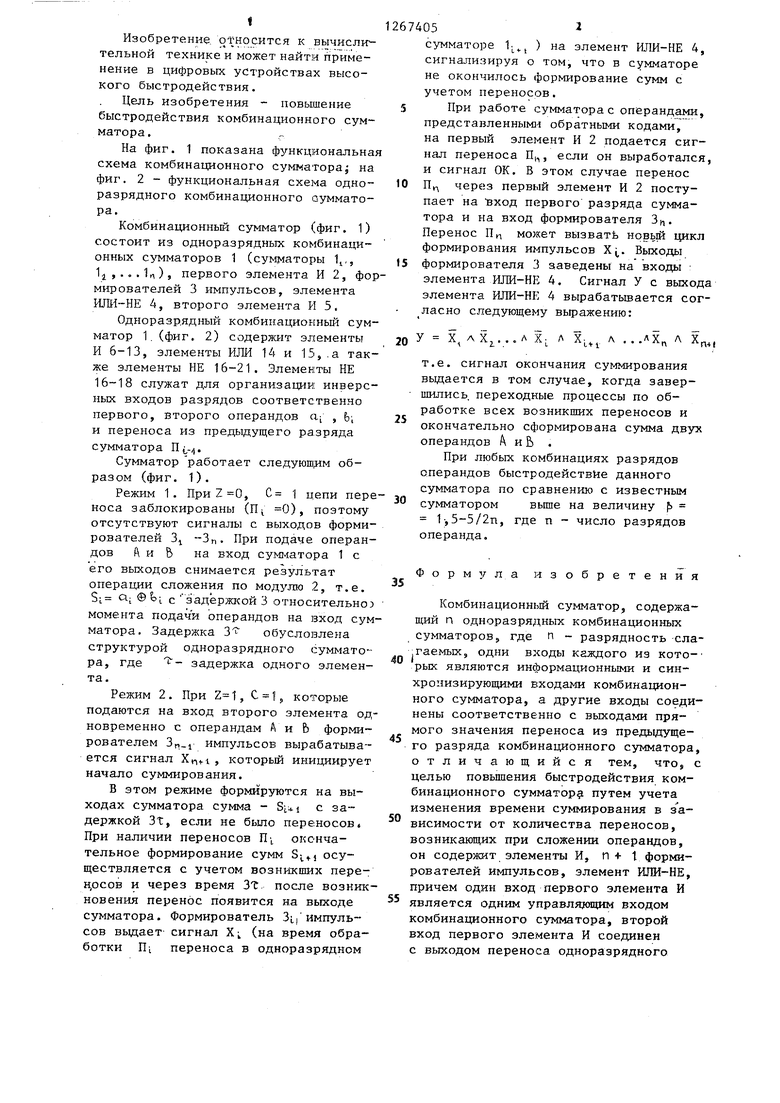

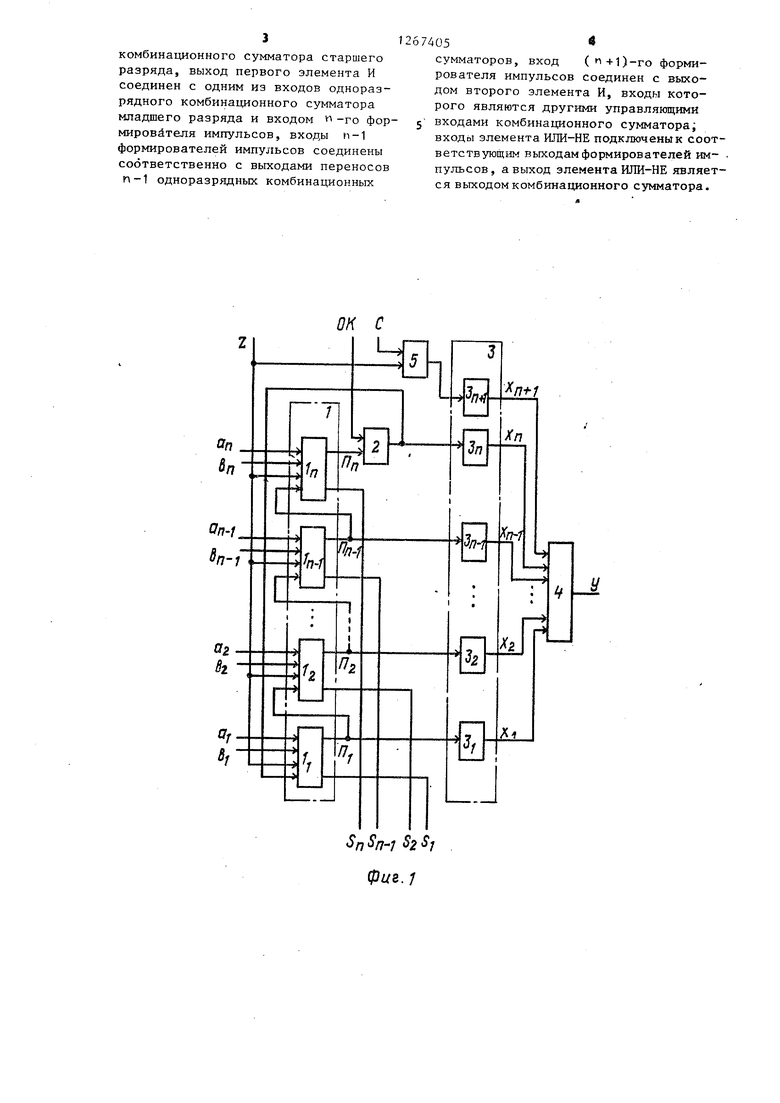

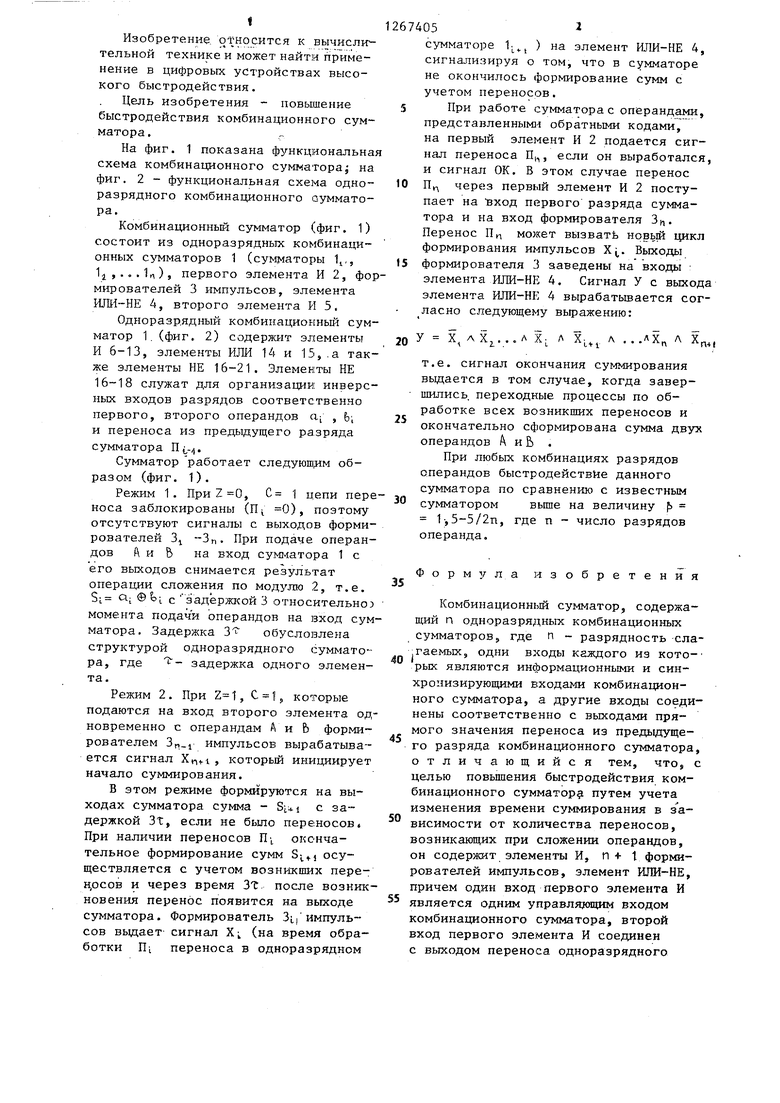

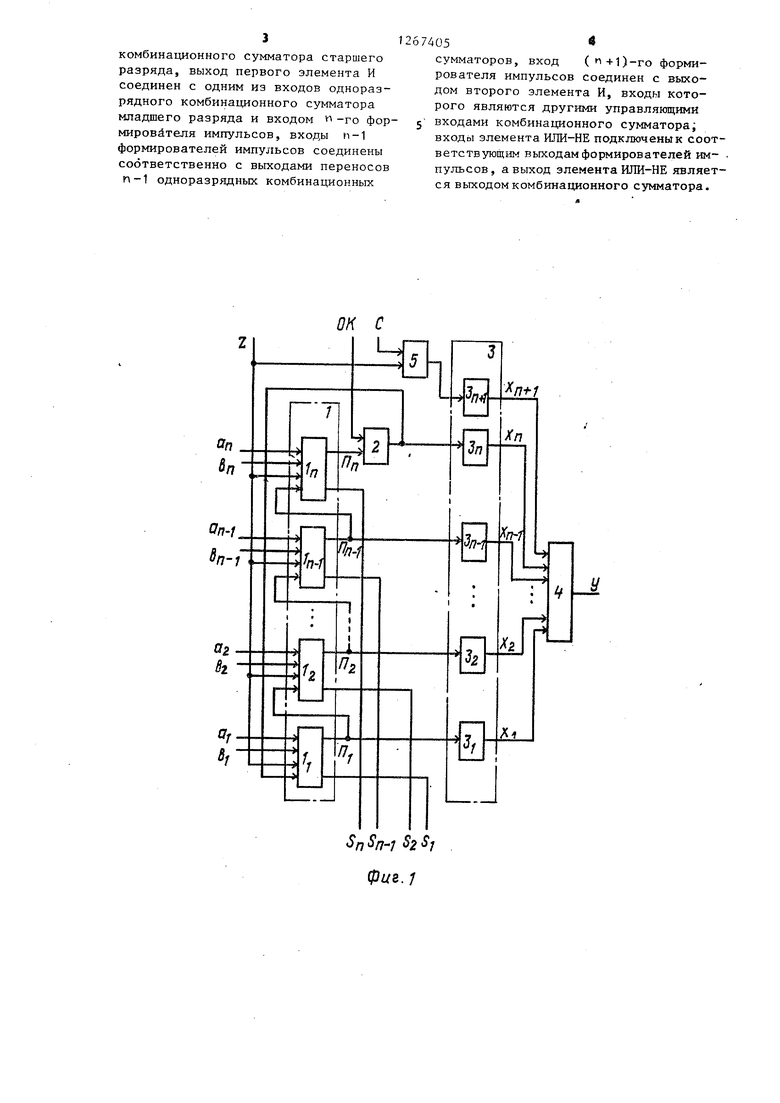

Цель изобретения - повышение быстродействия комбинационного сумматора .:На фиг. 1 показана функциональная схема комбинационного сумматора; на фиг. 2 - функциональная схема одноразрядного комбинационного сумматора.

Комбинационньй сумматор (фиг. 1) состоит из одноразрядных комбинационных сумматоров 1 (сумматоры :, 1j,...1,i), первого элемента И 2, формирователей 3 импульсов, элемента HJQi-HE А, второго элемента И 5.

Одноразрядный комбинационный сумматор 1.(фиг. 2) содержит элементы И 6-13, элементы ИЛИ 14 и 15,.а также элементы НЕ 16-21. Элементы НЕ 16-18 служат для организации инверсных входов разрядов соответственно первого, второго операндов а , Ь; и переноса из предыдущего разряда сумматора П,-.

Сумматор работает следуюш;им образом (фиг. 1).

Режим 1. При , С 1 цепи перв носа заблокированы (П 0), поэтому отсутствуют сигналы с выходов формирователей 3 3л. При подаче операндов f и & на вход сумз атора 1 с его выходов снимается результат операции сложения по модулю 2, т.е. S; а; ® bt с задершсой 3 относительноз момента подачи операндов на вход сумматора. Задержка 3 обусловлена структурой одноразрядного сумматора, где задержка одного элемента.

Режим 2. При , С. |, которые подаются на вход второго элемента одновременно с операндам Аи Ь формирователем Зг. импульсов вырабатывается сигнал , который инициирует начало суммирования.

В этом режиме формируются на выходах сумматора сумма - S;, с задержкой 3t, если не было переносов. При наличии переносов И,, окончательное формирование сумм осуществляется с учетом возник11ш:х перенрсов и через время St. после возникновения перенос появится на выходе сумматора. Формирователь 3 |импульсов выдает сигнал Xi (на время обработки Hi переноса в одноразрядном

267405

сумматоре l.j ) на элемент ИЛИ-НЕ 4, сигнализируя о том, что в сумматоре не окончилось формирование сумм с учетом переносов.

5 При работе сумматора с операндами, представленным 1 обратными кодами, на первый элемент И 2 подается сигнал переноса П,,, если он выработался, и сигнал ОК. В этом случае перенос 10 П, через первый элемент И 2 поступает на вход первого разряда сумматора и на вход формирователя 3ц. Перенос П может вызвать новьй цикл формирования импульсов Х. Выходы fS формирователя 3 заведены на входы ; элемента ИЛИ-НЕ 4. Сигнал У с выхода элемента. ИЛИ-НЕ 4 вырабатьшается сог ласно следующему выражению:

20 У X, АХ...л X. л Х.,, л ...лх„ л Хп„

т.е. сигнал окончания суммирования выдается в том случае, когда завершились, переходные процессы по обработке всех возникших переносов и окончательно сформирована сумма двух операндов Л и Ь .

При любых комбинациях разрядов операндов быстродействие данного сумматора по сравнению с известным

выше на величину р

сумматором

1-, 5-5/2п, где п - число разрядов операнда.

Формула изобретения

35

Комбинационный сумматор, содержащий п одноразрядных комбинационных сумматоров, где п - разрядность слагаемых, одни входы каждого из котоIрык являются информационными и синхронизирующими входами комбинационного сумматора, а другие входы соединены соответственно с выходами прямого значения переноса из предыдущего разряда комбинационного сумматора, отличающийся тем, что, с целью повьшения быстродействия комбинационного сумматору путем учета изменения времени суммирования в зависимости от количества переносов, возникающих при сложении операндов, он содержит элементы И, п 4- t формирователей импульсов, элемент ИЛИ-НЕ, причем один вход первого элемента И является одним управляющим входом комбинационного сумматора, второй вход первого элемента И соединен с выходом переноса одноразрядного

комбинационного сумматора старшего разряда, выход первого элемента И соединен с одним из входов одноразрядного комбинационного сумматора младшего разряда и входом -го фор мировйтеля импульсов, входы п-1 формирователей импульсов соединены соответственно с выходами переносов п-1 одноразрядных комбинационных

267405

сумматоров, вход (+1)-го формирователя импульсов соединен с выходом второго элемента И, входы которого являются другими управляющими 5 входами комбинационного сумматора; входы элемента ИЛИ-НЕ подключены к соответствукидим выходам формирователей импульсов , а выход элемента ИЛИ-НЕ является выходом комбинационного сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Последовательный сумматор | 1989 |

|

SU1709298A2 |

| Сумматор по переменному модулю | 1990 |

|

SU1756884A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1056184A2 |

| ПАРАЛЛЕЛЬНЫЙ АСИНХРОННЫЙ СУММАТОР | 1994 |

|

RU2097826C1 |

| Сумматор с контролем | 1979 |

|

SU788108A1 |

| Комбинационный сумматор | 1979 |

|

SU800992A1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| Последовательный сумматор | 1987 |

|

SU1411734A1 |

| Комбинационный сумматор | 1982 |

|

SU1078426A1 |

Изобретение относится к вычислительной технике и может найти применение в цифровых устройствах высокого быстродействия. Цель изобретения - повьппение быстродействия комбинационного сумматора. Комбинационный сумматор состоит из одноразрядных комбинационных сумматоров, элементов И, формирователей импульсов, элемента ИЛИ-НЕ. Одноразрядный комбинационный сумматор содержит элементы И, элементы ИЛИ и элементы НЕ. Элементы НЕ служат для организации инверсных входов разрядов соответственно первого, второго операндов , bi и переноса из предыдущего разряда сумматора П .. При любых комбинациях разрядов операндов быстродействие данного сумматора вьипе на величину 1,5-5/2п, где п - хгасло разрядов операнда. 2 ил. (Я С

Sfj Sn-j 82 Sj фиг.;

Физ. 2

| Асинхронный сумматор | 1973 |

|

SU491949A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Комбинационный сумматор | 1979 |

|

SU800992A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-30—Публикация

1983-12-27—Подача