дпми первого, вторстго и седьмого элементов II и с вторелм входом девятого элемента И, третий вход которого соединен с входом прямого знания переноса из пред адущего разряда сумматора, выход четвертого элемента ИЛИ соединен с четвертыми входами пятого, шестого и восьмого

элементов , с выходом инверсного значения суммы сумматора и с первым входом одиннадцатого элемента И, второй и третий входы которого соединены соответственно с выходом второго элемента ИЛИ и с входом инверсного значения переноса из предыдущехо разряда сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Комбинационный сумматор | 1987 |

|

SU1411737A1 |

| Комбинационный сумматор | 1979 |

|

SU800992A1 |

| Арифметико-логическое устройство | 1978 |

|

SU922727A1 |

| Одноразрядный адаптируемый четверичный сумматор | 1981 |

|

SU1053102A1 |

| Комбинационный сумматор | 1987 |

|

SU1543399A1 |

| Конвейерное вычислительное устройство | 1989 |

|

SU1693601A1 |

| Конвейерное операционное устройство | 1985 |

|

SU1254470A1 |

| Арифметическо-логическое устройство | 1979 |

|

SU822180A1 |

| Устройство для сложения в избыточной системе счисления | 1986 |

|

SU1365077A1 |

| Четверичный сумматор | 1983 |

|

SU1124290A1 |

КОМБИНАЦИОННЫЙ СУММАТОР, содерхсащий в каждом разряде десять элементов И и четыре элемента ИЛИ, причем входы первого элемента И соединены соответственно с входами инверсного значения первого операнда, прямого значения второго операнда и инверсного значения переноса из предыдущего разряда сумматора, входы второго элемента .И соединены соответственно с входами прямого значения первого операнда, инверсного значения второго операнда и инверсного значения переноса из предыдущего разряда cy мaтopa, входы третьего элемента И соединены соответственно с входами инверсных значений первого и второго операндов сумматора, входы .четвертого элемента И соединены соответственно с входами прямых значений первого и второго операндов сумматора, входы пятого элемента И соединены соответственно с входами инверсного значения первого операнда, прямого значения второго операнда и прямого значения переноса из предыдущего разряда сумматора, вхбды шестого элемента И соединены соответственно с входами прямого зпачения первого операнда, инверсного значения второго операнда и прягтаго значения переноса из предыдущего разряда сумматора, входы седьмого элемента И соединены СООТВЕ; гственно с входами )x значений первого и второго операндов и прямого значения переноса из предыдущего разряда сумматора, входы восьмого элемента И соединены соответственно с входами инверсных значений первого и второго операндов и инверсного значения переноса из предыдущего разряда cyMT/iaTopa, выходы первого, второго и третьего элементов И подключены к соответствующим входам первого элемента МЛН, выходы четвертого, пятого и шестого элементов И подключены к соответствующим входам второго элемента ИЛИ, выходы седьмого и восьмого элементов И Q S подключены соответственно к первым (Л входам третьего и четвертого элементов ИЛИ, выход первого элемента ИЛИ соединен с первым входом девятого элемента И, отличающийся тем,- что, с целью упрощения комбинационного сумматора, он содержит одиннадцатый элемент И, причем выходы первого и второго элементов ИЛИ соединены соответствен но с выходами инверсного и прямого значений переноса в следующий 00 разряд сумматора и первым и вторым NP входами десятого элемента И, осталььо ные входы которого соединены с входами прямого и инверсного значений о .первого и второго операндов .сумматора, а выход - с вторыми входами третьего и четвертого элементов ИЛИ, третий, четвертый и пятый входы третьего элемента ИЛИ соединены :соответственно с выходами первого, второго и девятого элементов И, а третий, четвертый и пятый входы четвертого элемента ИЛИ соединены соответственно с выходами пятого, шестого и одиннадцатого элементов И, выход третьего элемента ИЛИ соединен с выходом прямого значения суммы сумматора, с четвертьлм вхо

Изобретение относится к вычислительной технике и может быть исполь зовано в процессорах ЭВМ. Известен асинхронный сумматор, выполненный на триггерах, у которого увеличение быстродергствия достигается за счет обеспече.ния работы по реальным задержкам путем индикации моментов окончания переходных процессов Cl3 Недостатком известного асинхронного сумматора является сравнительно низкое быстродействие: один разряд по быстродействию эквивалентен 7- 8-уровневой комбинационной схеме. Наиболее близким техническим решением к предлагаемому является ком бинационный сумматор, содержащий в каждом разряде десять элементов И и четыре элемента ИЛИ, причем входы первого элемента И соединены соответственно с входами инверсного значения первого операнда, прямого значения второго операнда и инвепсного значения переноса из предыдущего разряда сумматора, входы второго элемента И соединены соответст венно с входами прямого значения первого операнда, инверсного значен второго операнда и инверсного значения переноса из предыдущего разряда сумматора, входы третьего элемента И соединены соответственно с входами инверсных значений первого и второго операндов сумматора, а вх ды четвертого элемента И соединены соответственно с входами прямых значений первого и второго операндов сумматора, входы пятого эле-- мента И соединены соответственно с вxoдaIvlи инверсного значения первого операнда, прямого значения второго операнда и прямого значения переноса из предьщущего разряда сумматора, входы шестого элемента И соединены соответственно с входами прямого значения первого операнда, инверсного значения второго операнда и прямого значения переноса из предыдущего разряда сум матора, входы седьмого элемента И соединены соответственно с входами прямых значений первого и второго операндов и прямого значения переноса из предьщущего разряда сумматора, входы восьмого элемента И соединены соответственно с входами первого и второго операн- . дов и инверсного значения переноса из предыдущего разряда сумматора, выходы первого, второго и третьего элементов И подключены к соответствующим входам первого элемента ИЛИ, выходы четвертого, пятого и шестого элементов.И подключены к соответствующим входам второго элемента ИЛИ, выходы седьмого и восьмого элемента И подключены соответственно к первым входам третьего и четвертого элементов ИЛИ, выход первого элемента ИЛИ соединен с первым входом девятого элемента И и с входами третьего элемента ИЛИ, вторые входы девятого.и десятого элементов И соединены с выходом третьего элемента ИЛИ и выходом суммы данного разряда сумматора, а выходы - с первыми входами четвертого и пятого элементов ИЛИ, вторые входы которых соединены соответственно с выходами восьмого элемента И и второго элемента ИЛИ, а выходы - с выходами инверсного и прямого значений переноса в последующий разряд сумматора ;2J. Недостатком такого сумматора является сложность конструкции из-за избыточного количества входов и выходов сумматора. Действительно, для реализации сумматора с Hcno fbзованием его максимального быстродействия путем обеспечения работы по реальным задержкам элементов и индикации моментов окончания переходных процессов сумматор должен иметь выходы не только значения суммы каждого разряда, но и переноса последние и подаются на вход индикатора окончания переходных процессов. Кроме того, в сумматоре не индицируется инертное состояние входов сумматора, что также является его недостатком, так как требует увеличения числа входов индикатора окончания переходных процессов, а следовательно, и его усложнения. Наконец, наличие у сумматора входда, подключен Hoio к входу всех его элементов И, также усложняет конструкцию сумматора.

Цель изобретения - упрощение комбинационного сумматора.

Для достижения поставленной цели комбинационный сумт.1атор, содержащий в каждом разряде десять элементов И и четыре элемента ИЛИ, причем входы первого элемента И соединены соответственно с входами инверсного значения первого операнда, прямого значения второго операнда и инверсного значения переноса из предыдущего разряда сумматора, входы второго элемента Н соединены cooTBetcTBeHHO с входами прямого значения первого операнда, инверсного значения второго операнда и инверсного значения переноса из предыдущего разряда сумматора, входы третьего элемента И соединены соответственно с входами инверсных значений первого и второго операндов сумматора, входы четвертого элемента И соединены соответствен.но с входами прямых значений первого и второго операндов сумматора входы пятого элемента И соединены соответственно с входами инверсного значения первого операнда, прямого значения второго операнда и прямого значения переноса из предьщущего разряда сумматора, входы шестого элемента И соединены соответственно с входами прямого значения первого операнда, инверсного значения второго операнда и прямого значения переноса из предыдущего разряда сумматора, входы седьмого элемента И соединены соответственно с входами прямых значений первого и второго операндов и прямого значения переноса из предыдущего разряда сумматора, входы восьмого элемента И соединены соответственно с входами инверсных значений первого и второго операндов и инверсного значения переноса из предыдущего разряда сумматора, выходы первого, второго и третьего элементов И подключены к соответствующим входам первого элемента ИЛИ, выходы четвертого, пятого и шестого элементов И подключены к соответствующим входам второго элемента ИЛИ, выходы седьмого и восьмого элементов И подключены соответственно к первым входам третьего и четвертого элементов ИЛИ, выход первого элемента ИЛИ соединен с первым входом девятого элемента И, содержит одиннадцатый элемент И, причем выходы первого и второго элементов ИЛИ соедиHeHhj соответственно с выходами инверсного и прямого значений переноса в следующий разряд сумматора и первым и вторып входами десятого элемента И, остальные входды которого соединены с входами прямого и инверсного значений первого и второ операЕщов cyм 5aтopa, а выход - с вторыми входами третьего и четвертого элементов ИЛИ, третий, четвертый и пятый входы третьего элемента ИЛИ соединены соответственно с выходами первого, второго и девятого элементов И, а третий, четвер тый и пятый входы четвертого элемента ИЛИ соединены соответственно с выходами пятого, шестого и одиннадцатого элементов И, выход третьего элемента ИЛИ соединен с выходом прямого значения суммы сумматора, с четвертыми входами первого, второго и седьмого элементов И и с вторым входом девятого элемента И, третий вход которого соединен с входом прямого значения переноса из предыдущего разряда сумматора, выход четвертого элемента ИЛИ сое динен с четвертыми входами пятого, шестого и восьмого элементов И, с выходом инверсного значения суммы, сумматора и с первым входом одиннадцатого элемента И, второй и третий входы которого соединены соответственно с выходом второго элемента ИЛИ и с входом инверсного значения переноса из предыдущего разряда сумматора .

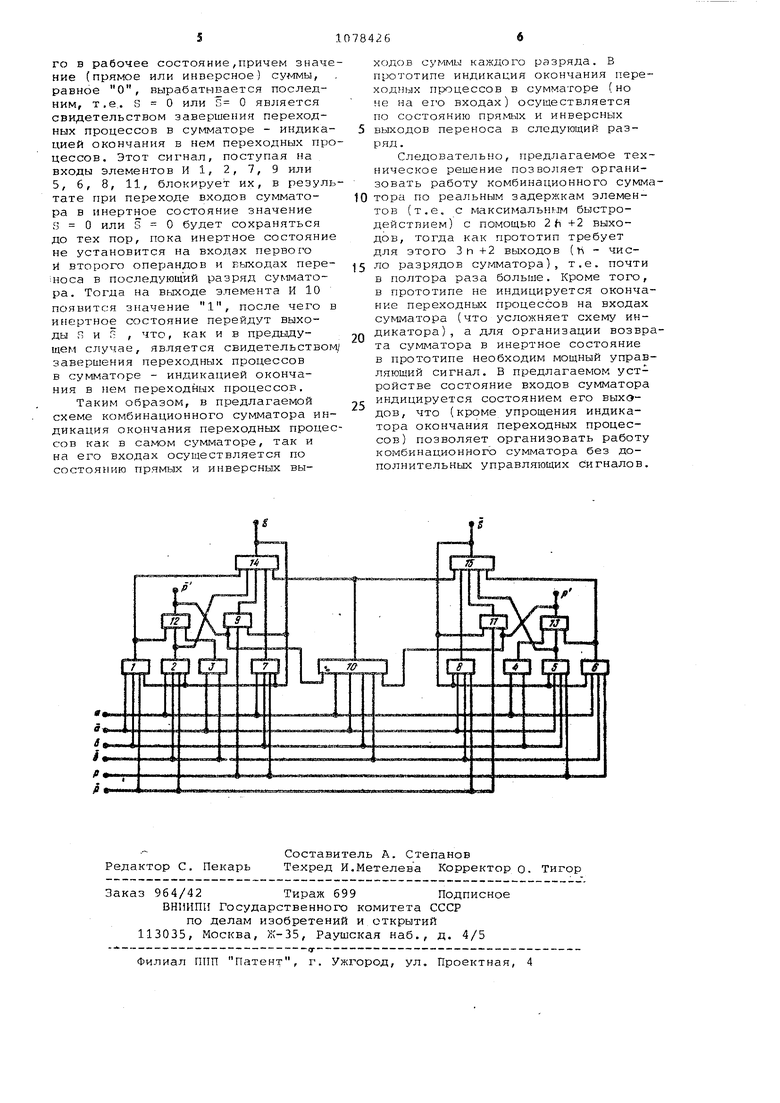

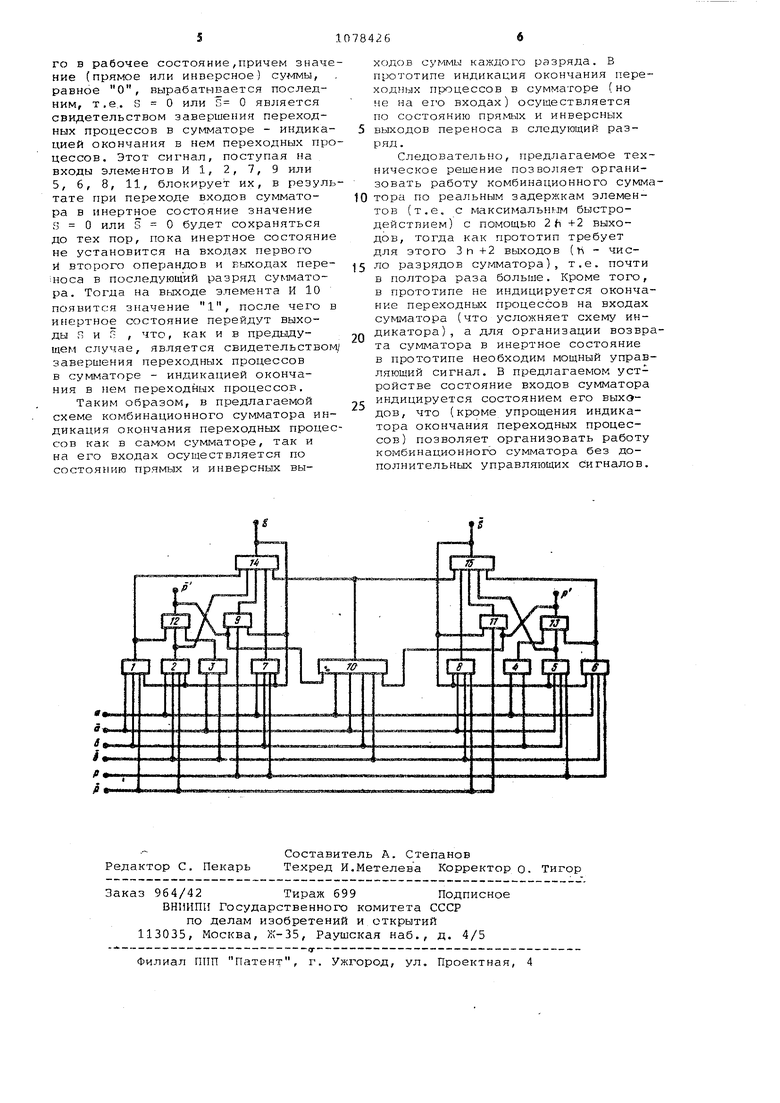

На чертеже представлена функциональная схема одного разряда комбинационного сумматора.

Разряд комбинационного сумматора содержит элементы И 1-11 и элементы ИЛИ 12-15.

Выходы S и - выходы прямого и инверсного значений суммы (сигналы завершения переходного процесса в cy 1мaтope), р и р - выходы прямого и инверсного значений переносов в последующий разряд сумматора, входы а, а и Ь, b - входы прямого и инверсного значений первого и второго операндов, Р и р - входы прямого и инверсного значений переноса из предыдущего разряда сумматора.

Сумматор работает следующим образом.

Инертное состояние схемы характеризуется значением 1 на всех ее входах и выходах: 1. После того, как на выходах сумматора появится какой-либо рабочий набор значений входов, на его выходах установятся прямые и инверсные значения переноса в следующий разряд и суммы данного разряда.

При этом указанные значения вырабтываются только после Tord, как все входы сумматора перейдут из инертно

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Асинхронный сумматор | 1973 |

|

SU491949A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Комбинационный сумматор | 1979 |

|

SU800992A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1984-03-07—Публикация

1982-08-03—Подача