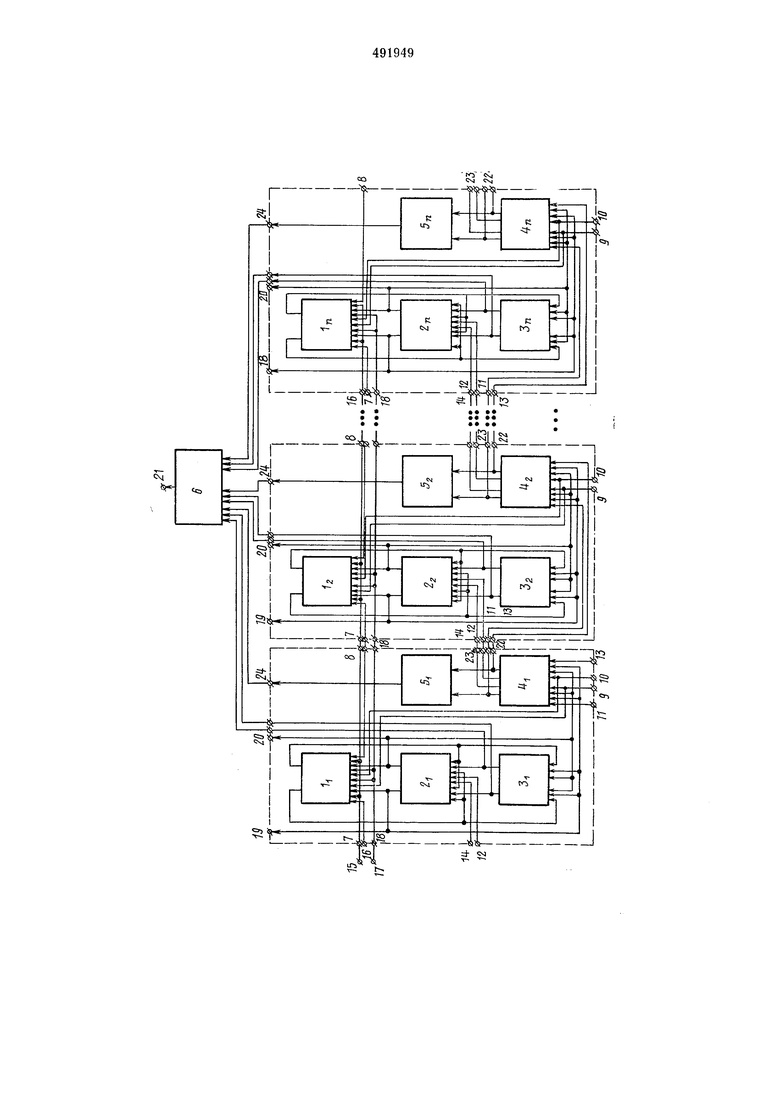

3

ния установки первого слагаемого, вход 17, соедиленный со.лхода,1п 18 каждого разряда, для разрешснпя сум-МП Ю вапия слагаемых.

Внешними выходам.и сумматора являются: выходы 19 и 20 каждого разряда; выход 21, соединенный с выходом триггера-индикатора 6, для шщикации разЛИчных фаз нереходных процессов при суммировании.

Функционирование асинхронного сумматора сводится .к следующему.

В .исходном состоЯНии в триггерах 21 хранится код первого слагаемого, на внешних входах 9 н 10 каждого разряда установлены прямое И инверсное значения .кода второго слагаемого, на внешних входах 15 и 17 установлен потенциал «О. Триггеры И три этом заблокированы, т. е. .на обоих их плечах сигналы равны «i. Все триггеры 3i и 4i также заблокированы, поскольку на одном из плеч трИггеров 2i имеется потенциал «О. На выходах 22 и 23 сигналы равны «О, а на выходах элементов 51 - «1. На всех входах триггераиндикатора 6 сигналы равны «1, так, что па левом его плече устанавливается сигнал «О, а на правом- {выход 21) -«1. На входах И, 12 и 13, 14 1-го разряда установлены соответственно прямое и ИНверсное значения сигналов переноса в 1-й разряд сумматора (например, при сложении в прямых кодах положительных ч 1Сел - «О и «1).

Суммирование начинается с .изменения значения потенциала па входе 17 с «О на «1 (на входе 15 в рабочем режиме сохраняется сигнал «О), что вызывает деблокировку триггеров 1, и в них поразрядно записываются значения полусумм.

Как только на одном пз плеч триггера 1/ появится потенциал «О, это вызывает блокировку триггера 2г, что, в свою очередь, разрешит перепись пиформацш с триггера li в триггер 31, а также вызовет деблокирование триггера 4г. В триггер 4i заносится значение переноса. Время устаповлення триггеров 4 в обш&м случае зависит от значений слагаемых. После того, как во :все триггеры 3/ и 4/ в сумматоре запишутся зт1ачения «О или «1, а на выходах 24 элементов 5f во всех разрядах появятся сигналы «О, левое плечо трнггера-ипднкатора 6 перебросится из «О в «1, а правое плечо (выход 21) -из «1 в «О. Появление сигнала «О па выходе 21 означает окончание переходных процессов первой фазы сумм.ировапия - выработки значений полусумм и переносов.

4

С целью ускорения работы сумматора за счет использовапия этого факта сигналы переноса снимаются не непосредственно с плеч триггеров, а с выходов подключенных к ним ииверторов.

После .появления еигиала «О на выходе 21 потенциал иа входе 17 должен быть изменен е «1 па «О (это делает автомат, улравляющий работой сумматора). Происходит блокировка триггеров i, запись ре.зультата в триггеры 2i всех разрядов сумматора и затем блокировка триггеров 3i и 4t всех разрядов. Когда будут заблокированы все триггеры 3i и 4(, на всех входах триггера-индикатора 6 сигналы будут равны «1, что вызовет иереброс его левого плеча в «О, а правого - в «1. Появление сигнала «1 означает, что закончились переходные процессы второй фазы работы сумматора - формирование сумм. Инверсные и прямые значения суммы могут быть сняты с выходов 18 и 20 всех разрядов. Сумматор готов к следующему циклу работы.

Появление сигнала переноса из младшего разряда ожидается только в двух из четырех случаях: когда о.дно из слагаемых равно «I, а второе - «О. Поэтому для подсчета числа разрядов, в которых ожидается сквозной перенос, надо сложить по модулю 2 коды двух слагаемых.

11 р е д м е т и 3 о б р е т е и и я

Асиихропный сумматор, содержаш,ий в каждом разряде один основной, два вспомогательных триггера и триггер переноса, выход которого соединен с входом триггера переноса последуюш,его разряда, элемент НЕ-ИЛИ, а также общнй триггер-индикатор, отличающийся тем, что, с целью повышения быстродействия, выходы обоих плеч основного триггера соедииены соответственно с входами первого и второго вспомогательных триггеров данного разряда и с выходом сумматора, а входы основного триггера :соеди«ены с выходами вспомогательных триггеров данного разряда iH е соответствующими входами сумматора, входы первого вспомогательного триггера соединены е входами триггера переноса, а выходы второго вспомогательного триггера соединенгз с входами триггера-индикатора, выходы триггера переноса каждого разряда соединены с входами элемента НЕ-ИЛИ своего разряда, выход элемента НЕ-ИЛИ соединен с входом триггера-индп.катора, выход которого подключен к выходу сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" | 2011 |

|

RU2475812C1 |

| ПАРАЛЛЕЛЬНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР | 1973 |

|

SU375646A1 |

| Устройство для преобразования двоично-десятичного кода в двоичный код и обратно | 1990 |

|

SU1755375A1 |

| Устройство для сравнения двоичных чисел | 2018 |

|

RU2665255C1 |

| Устройство для моделирования нейрона | 1991 |

|

SU1831715A3 |

| Двухтактный п-разрядный сумматор накапливающего типа | 1974 |

|

SU538365A1 |

| Устройство формирования адреса памяти | 1991 |

|

SU1827674A1 |

| Устройство для интегрирования функций | 1984 |

|

SU1242993A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ МИНИМАЛЬНЫХ ДВОИЧНЫХ ЧИСЕЛ | 2020 |

|

RU2755274C1 |

| Устройство для деления | 1988 |

|

SU1681303A1 |

Авторы

Даты

1975-11-15—Публикация

1973-09-26—Подача