1

со

О

;о

О)

, 5

Изобретение относится к вычислиельной технике и может быть испольовано в ЭВМ для контроля правильноси выполнения программ.

Цель изобретения - повьшение достоверности контроля.

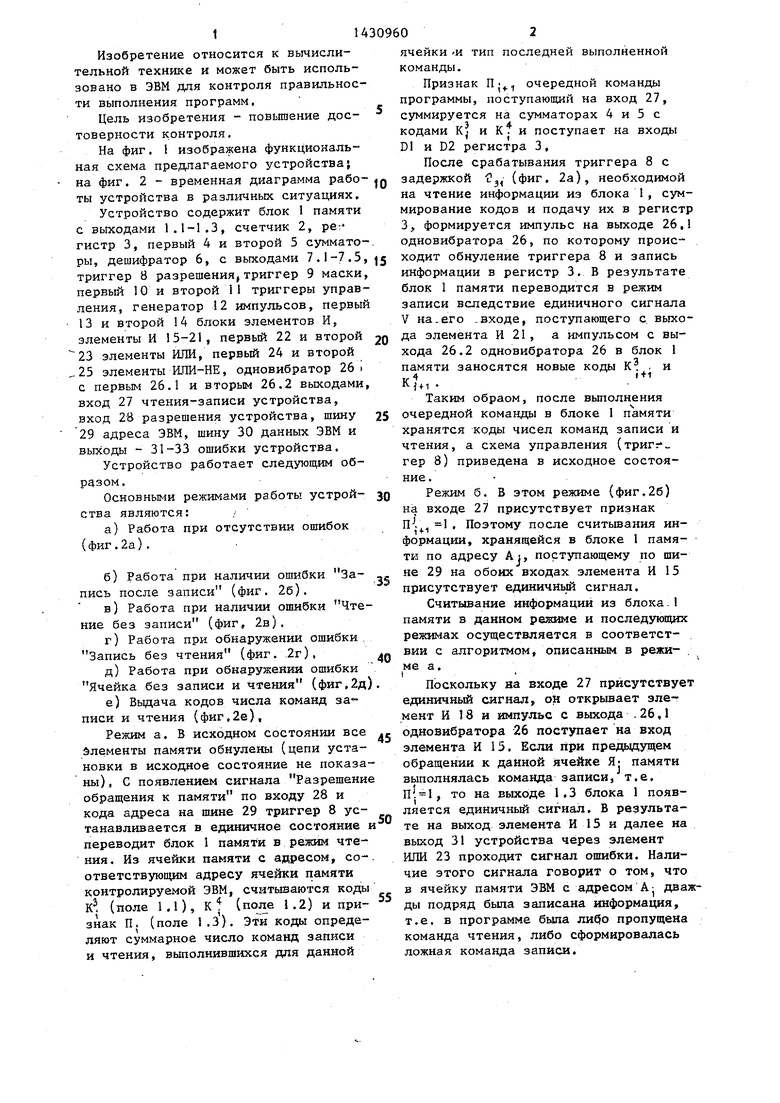

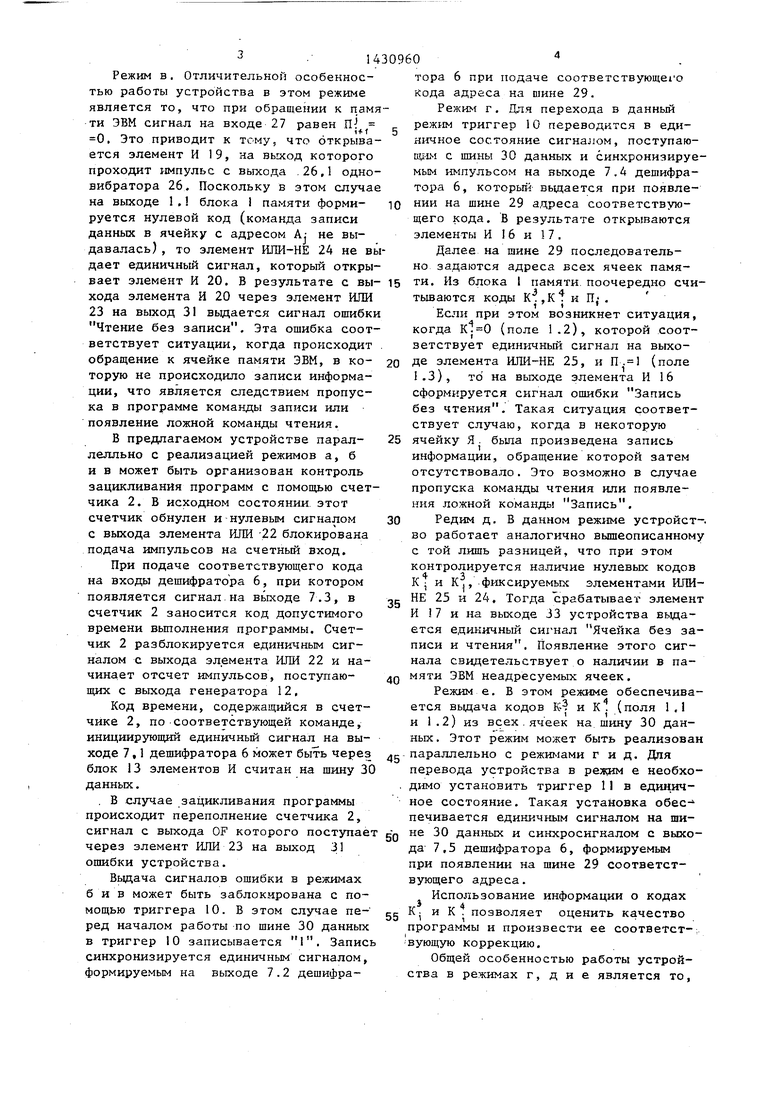

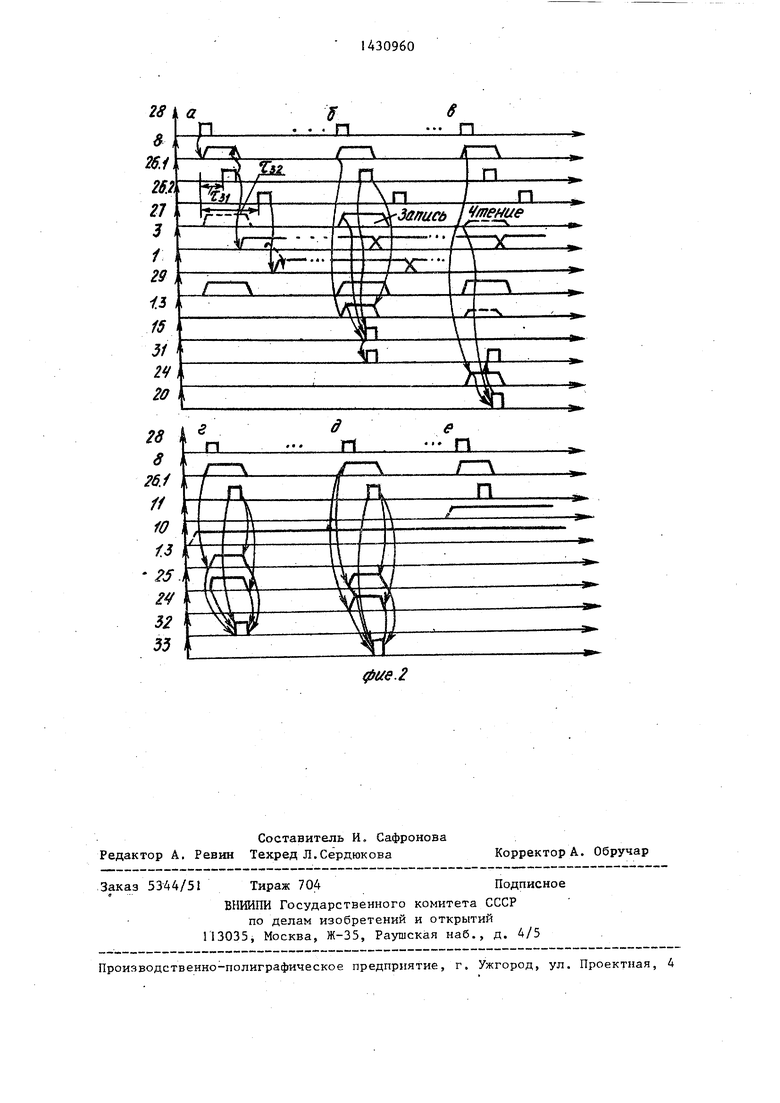

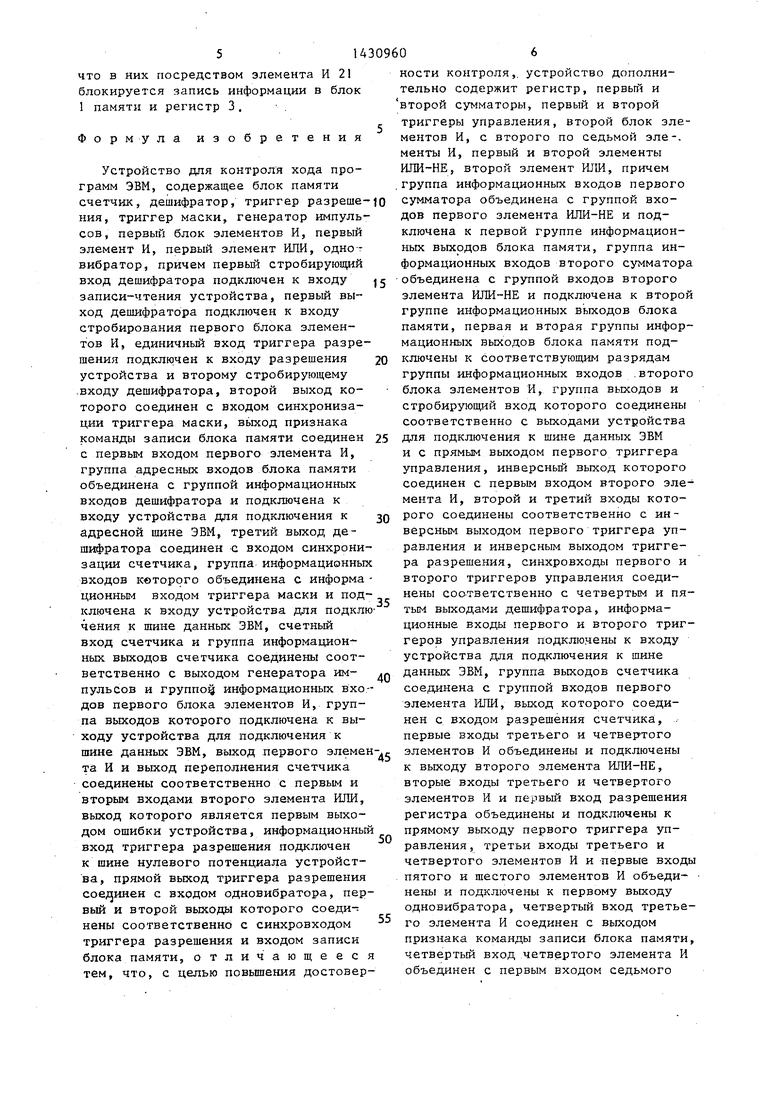

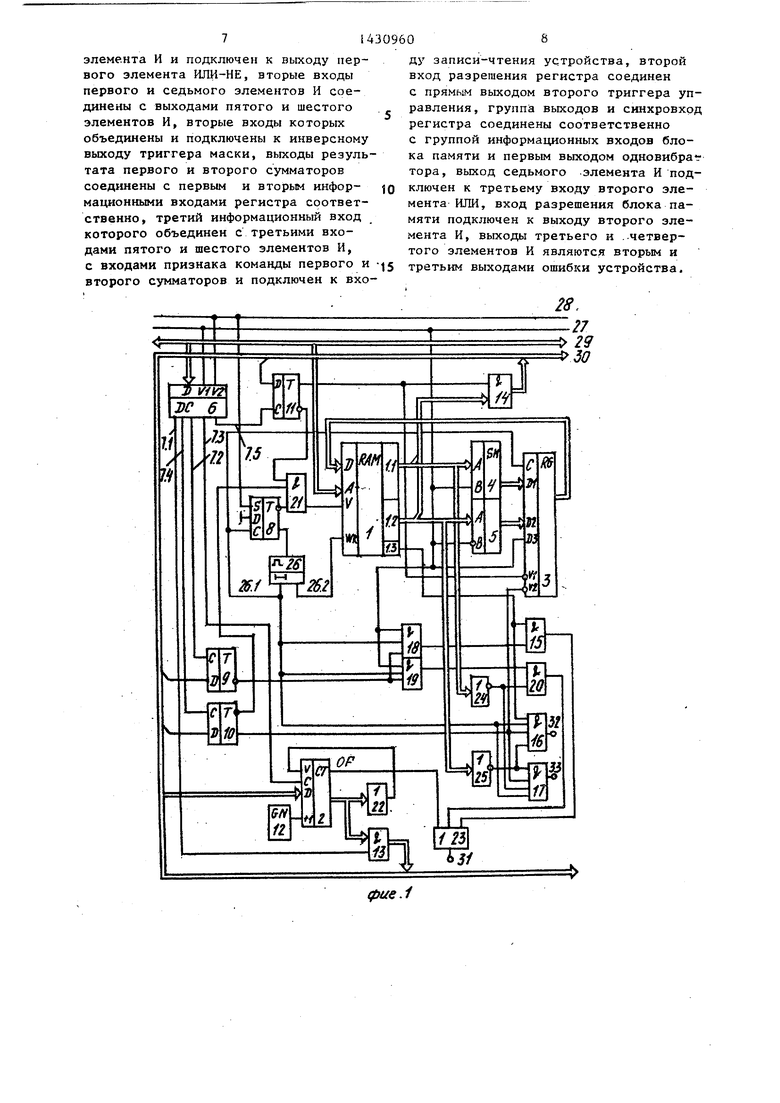

На фиг, 1 изображена функциональая схема предлагаемого устройства; а фиг. 2 - временная диаграмма рабо- Q ты устройства в различных ситуациях.

Устройство содержит блок 1 памяти выходами 1.1-1.3, счетчик 2, истр 3, первый 4 и второй 5 суммато-. ы, дешифратор 6, с выходами 7.1-7.5, j триггер 8 разрешения,триггер 9 маски, первьй 10 и второй 11 триггеры управления, генератор 12 импульсов, первый 13 и второй 14 блоки элементов И, элементы И 15-21, первый 22 и второй Q 23 элементы ИЛИ, первый 24 и второй 25 элементы Ш1И-НЕ, одновибратор 26 с первым 26.1 и вторым 26.2 выходами, вход 27 чтения-записи устройства, вход 28 разрешения устройства, шину 25 29 адреса ЭВМ, шину 30 данных ЭВМ и выходы - 31-33 ошибки устройства.

Устройство работает следующим об- .

Основными режимами работы устрой- ЗО ства являются: / .

а)Работа при отсутствии ошибок (фиг.2а).

б)Работа при наличии ошибки За- ,, пись после записи (фиг. 2б).

в)Работа при наличии ошибки Чтение без записи (фиг, 2в).

г)Работа при обнаружении ошибки . Запись без чтения (фиг. 2г), д

д)Работа при обнаружении ошибки Ячейка без записи и чтения (фиг,2д).

е)Выдача кодов числа команд за писи и чтения (фиг,2е),

Режим а. В исходном состоянии все д. Элементы памяти обнулены (цепи установки в исходное состояние не показаны), С появлением сигнала Разрешение обращения к памяти по входу 28 и кода адреса на шине 29 триггер 8 устанавливается в единичное состояние и переводит блок 1 памяти в режим чтения. Из ячейки памяти с адресом, со-, ответствующим адресу ячейки памяти контролируемой ЭВМ, считываются коды К. (поле 1.1), КI (попе I .2) и признак П. (поле 1.3). Эти коды определяют суммарное число команд записи и чтения, выполнившихся для данной

50

55

5

.

-. , j , йQ , 25

-

- ЗО

,,

. д

).

е д. аиеи-, ы 50

55

ячейки И тип последней выполненной команды.

Признак П|, очередной команды программы, поступающий на вход 27, суммируется на сумматорах 4 и 5 с кодами Kj и К . и поступает на входы D1 и D2 регистра 3,

После срабатывания триггера 8 с задержкой Dj, (фиг, 2а), необходимой на чтение информации из блока 1, суммирование кодов и подачу их в регистр 3, формируется импульс на выходе 26,1 одновибратора 26, по которому происходит обнуление триггера В и запись информации в регистр 3. В результате блок 1 памяти переводится в режим записи вследствие единичного сигнала V на.его .входе, поступающего с. выхода элемента И 21, а импульсом с выхода 26.2 одновибратора 26 в блок 1 памяти заносятся новые коды К , и

K}fi

Таким обраом, после вьшолнения очередной команды в блоке 1 п амяти хранятся коды чисел команд записи и чтения, а схема управления (тригг- гер 8) приведена в исходное состояние .

Режим б. В этом режиме (фиг,26) на входе 27 присутствует признак П 1 , Поэтому после считывания информации, хранящейся в блоке 1 памяти по адресу Ai, поступающему по шине 29 на обоих входах элемента И 15 присутствует единичньй сигнал,

Считывание информации из блока.I памяти в данном режиме и последукмцих режимах осуществляется в соответствии с алгоритмом, описанным в режиме а , 1.

Поскольку на входе 27 присутствует единичный сигнал, он открывает элемент И 18 и импульс с выхода .26,1 одновибратора 26 поступает на вход элемента И 15, Если при предащущем обращении к данной ячейке Я- памяти выполнялась команда записи, т,е, П.-1, то на выходе 1,3 блока 1 появляется единичный сигнал, В результате на выход элемента И 15 и далее на выход 31 устройства через элемент ИЛИ 23 проходит сигнал ошибки. Наличие этого сигнала говорит о том, что в ячейку памяти ЭВМ с адресом А- дважды подряд была записана информация, т.е. в программе бьша либо пропущена команда чтения, либо сформировалась ложная команда записи.

Режим в. Отличительной особенностью работы устройства в этом режиме является то, что при обращении к памти ЭВМ сигнал на входе 27 равен П 0, Это приводит к тому, что открывается элемент И 19, на выход которого проходит импульс с выхода .26,1 одно вибратора 26. Поскольку в этом случа на выходе 1. блока I памяти форми- руется нулевой код (команда записи данных в ячейку с адресом А; не вы

давалась), то элемент ИЛИ-НЕ 24 не вдает единичный сигнал, который открывает элемент И 20. В результате с вы хода элемента И 20 через элемент ИЖ 23 на выход 31 выдается сигнал ошибк Чтение без записи. Эта ошибка соответствует ситуации, когда происходит обращение к ячейке памяти ЭВМ, в которую не происходило записи информации, что является следствием пропуска в программе команды записи или появление ложной команды чтения.

В предлагаемом устройстве парал- лелльно с реализацией режимов а, б и в может быть организован контроль зацикливания программ с помощью счетчика 2. В исходном состоянии этот счетчик обнулен и нулевым сигналом с выхода элемента ИЛИ -22 блокирована подача импульсов на счетный вход.

При подаче соответствующего кода на входы дешифратора 6, при котором появляется сигнал на вькоде 7.3, в счетчик 2 заносится код допустимого времени вьшолнения программы. Счетчик 2 разблокируется единичньм сигналом с выхода элемента ИЛИ 22 и начинает отсчет импульсов, поступающих с выхода генератора 12,

Код времени, содержащийся в счетчике 2, по соответствующей команде, инициирующий единичный сигнал на выходе 7,1 дешифратора 6 может быть через блок 13 элементов И считан на шину 3 данных.

. В случае зацикливания программы происходит переполнение счетчика 2, сигнал с выхода OF которого поступае через элемент ИЛИ 23 на выход 31 ошибки устройства.

Выдача сигналов ошибки в режимах бив может быть заблокирована с помощью триггера 10. В этом случае перед началом работы по шине 30 данных в триггер 10 записывается 1. Запис синхронизируется единичным сигналом, формируемым на выходе 7.2 дешифра

о

0

0

35

15 ти. Из блока

тора 6 при подаче соответствующех о Кода адреса на шине 29.

Режим г. Для перехода в данный режим триггер 10 переводится в единичное состояние cигнaJJOм, поступаю- Щ1-1М с шины 30 данных и синхронизируемым импульсом на выходе 7.4 дешифратора 6, которьш выдается при появлении на шине 29 адреса соответствующего кода. В результате открываются элементы И 16 и 17,

Далее на шине 29 последовательно задаются адреса всех ячеек памя- I

памяти поочередно счи- тьшаются коды К. ,Kt и П; .

Если при этом возникнет ситуация, когда К (поле 1.2), которой соответствует единичный сигнал на выходе элемента ИЛИ-НЕ 25, и П.1 (поле 1.3), то на выходе элемента И 16 сформируется сигнал ошибки Запись без чтения. Такая ситуация соответствует случаю, когда в некоторую 25 ячейку Я. была произведена запись информации, обращение которой затем отсутствовало. Это возможно в случае пропуска команды чтения или появления ложной команды Запись,

Редим д. В данном режиме устройст-, во работает аналогично вышеописанному с той лишь разницей, что при этом контролируется наличие нулевых кодов

л о

К- и К,, фиксируемых элементами ИЛИ- НЕ 25 и 24, Тогда срабатывает элемент И 7 и на выходе 33 устройства выдается единичный сигнал Ячейка без записи и чтения. Появление этого сигнала свидетельствует о наличии в памяти ЭВМ неадресуемых ячеек,

Режим е. В этом режиме обеспечивается выдача кодов К и К . (поля 1,1 и 1.2) из всех.ячеек на шину 30 данных. Этот режим может быть реализован параллельно с режимами гид. Для перевода устройства в режим е необходимо установить триггер 1I в единичное состояние. Такая установка обес- печивается единичным сигналом на шине 30 данных и синхросигналом с выхода 7,5 дешифратора 6, формируемым при появлении на шине 29 соответствующего адреса.

40

45

50

55

Использование информации о кодах К. и К позволяет оценить качество

программы и произвести ее соответст-; вующую коррекцию.

Общей особенностью работы устройства в режимах г, д и е является то.

что в них посредством элемента И 21 блокируется запись информации в блок 1 памяти и регистр 3.

Формула изобретения

Устройство для контроля хода программ ЭВМ, содержащее блок памяти счетчик, дешифратор, триггер разрешения, триггер маски, генератор импульсов, первый блок элементов И, первый элемент И, первый элемент ИЛИ, одно- вибратор, причем первый стробирующий вход дешифратора подключен к входу записи-чтения устройства, первый выход дешифратора подключен к входу стробирования первого блока элементов И, единичньй вход триггера разрешения подключен к входу разрешения устройства и второму стробирующему .входу дешифратора, второй выход которого соединен с входом синхронизации триггера маски, вьгход признака команды записи блока памяти соединен с первым входом первого элемента И, группа адресных входов блока памяти объединена с группой информационных входов дешифратора и подключена к входу устройства для подключения к адресной шине ЭВМ, третий выход дешифратора соединен с входом синхронизации счетчика, группа информационных входов которого объединена с информа ционным входом триггера маски и подключена к входу устройства для подклю чения к шине данных ЭВМ, счетный вход счетчика и группа информацион-- ных выходов счетчика соединены соответственно с выходом генератора им- пульсов и группоц информационных входов первого блока элементов И, группа выходов которого подключена к выходу устройства для подключения к шине данных ЭВМ, выход первого элемен

та И и выход переполнения счетчика соединены соответственно с первым и вторым входами второго элемента ШШ, выход которого является первым выходом ошибки устройства, информационный вход триггера разрешения подключен к шине нулевого потенциала устройства, прямой выход триггера разрешения coe JИнeи с входом одновибратора, первый и второй вькоды которого соединены соответственно с синхровходом триггера разрешения и входом записи блока памяти, отличающееся тем, что, с целью повьшгения достовероj 0 5 о « 5

5

0

5

ности контроля,, устройство дополнительно содержит регистр, первьй и

второй сумматоры, первый и второй триггеры управления, второй блок элементов И, с второго по седьмой эле-, менты И, первый и второй элементы ИЛИ-НЕ, второй элемент ИЛИ, причем

.группа информационных входов первого сумматора объединена с группой входов первого элемента ИЛИ-НЕ и подключена к первой группе информационных выходов блока памяти, группа информационных входов второго сумматора объединена с группой входов второго элемента ИЛИ-НЕ и подключена к второй группе информационных выходов блока памяти, первая и вторая группы информационных выходов блока памяти подключены к соответствующим разрядам группы информационных входов .второго блока элементов И, группа выходов и стробирующий вход которого соединены соответственно с выходами устройства для подключения к шине данных ЭВМ и с прямым выходом первого триггера управления, инверсный вьгход которого соединен с первым входом второго элемента И, второй и третий входы которого соединены соответственно с инверсным выходом первого триггера управления и инверсным выходом триггера разрешения, синхровходы первого и второго триггеров управления соединены соо-тветственно с четвертым и пятым выходами дешифратора, информационные входы первого и второго триггеров управления подключены к входу устройства для подключения к шине данных ЭВМ, группа выходов счетчика соединена с группой входов первого элемента ШШ, выход которого соединен с входом разрешения счетчика, . первые входы третьего и четвертого элементов И объединены и подключены к выходу второго элемента ИЛИ-НЕ, вторые входы третьего и четвертого элементов И и первый вход разрешения регистра объединены и подключены к прямому выходу первого триггера управления , третьи входы третьего и четвертого элементов И и первые входы пятого и шестого элементов И объеди- нены и подключены к первому выходу одновибратора, четвертый вход третьего элемента И соединен с выходом признака команды записи блока памяти, четвертый вход .четвертого элемента И объединен с первым входом седьмого

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля хода программы | 1987 |

|

SU1413634A1 |

| Устройство для отладки программ | 1988 |

|

SU1654827A1 |

| Устройство для контроля выполнения программ | 1989 |

|

SU1709319A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Устройство для сопряжения двух электронных вычислительных машин (ЭВМ) | 1983 |

|

SU1265781A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

Изобретение относится к области вычислительной техники и может быть использовано в ЭВМ для контроля правильности выполнения программы. Целью изобретения является повышение достоверности контроля. В устройство введены регистр, первый и второй сумматоры,, первый и второй триггеры управления, второй блок элементов И, со второго по седьмой элементы И, первый и второй элементы ИЛИ-НЕ. Введение новых блоков обеспечивает снижение вероятности необнаружения нарушения хода программы в 2,2-2,6 раза и повьшение достоверности контроля устройства. Устройство обеспечивает контроль неадресуемых ячеек и подсчет числа команд записей и чтения по каждой из ячеек памяти ЭВМ. 2 ил. i

фие.1

фие.2

| Устройство для контроля хода программ | 1980 |

|

SU894713A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля хода программы | 1984 |

|

SU1211735A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-15—Публикация

1987-03-09—Подача