1

Изобретение относится к вычислительной технике к предназначено для решения уравнений математической .физики.

ИзвеСтны устройства, содержащие .цифровые однородные конечно-разностные сеточные модели . Наиболее близким к изобретению по технической сущеости является устройство для (решеНИя уравнения теплопроводностн, содержащее цифровую однородную конечно-разностную сеточную модель 2. Однако известное устройство не обеспечивает достаточной точности решения уравнений математической физики.

Целью изобретения является повышение точности решения уравнений. В описываемом устройстве это достигается тем, что в него введены блок управления и блок индикац-ии параметров, и каждый узел сеточной модели содержит |МИкропрО|Цессор, блок пам:яти и «регистры, причем каждый выход блока управления связан со входом соответствующего микропроцессора, один выход каждО|Го из которых подключен д одному из входов блока «ндикации пара:мет:ров решения, а другие выходы каждого микропро.цессора соединены с адресной и информационной шинами и со входа-ми блока памяти и ре гистров соответствующего узла сеточной модели, первый вход регистров и яблока памяти соединены с информационными шинами, вторые входы блока памяти и двух регистров соединены с адресной шиной, информационные и адресные шины узлов сеточной -моделн соединены мелхду собой и подключены соответственно к выходам блока управления и входам блока индикации.

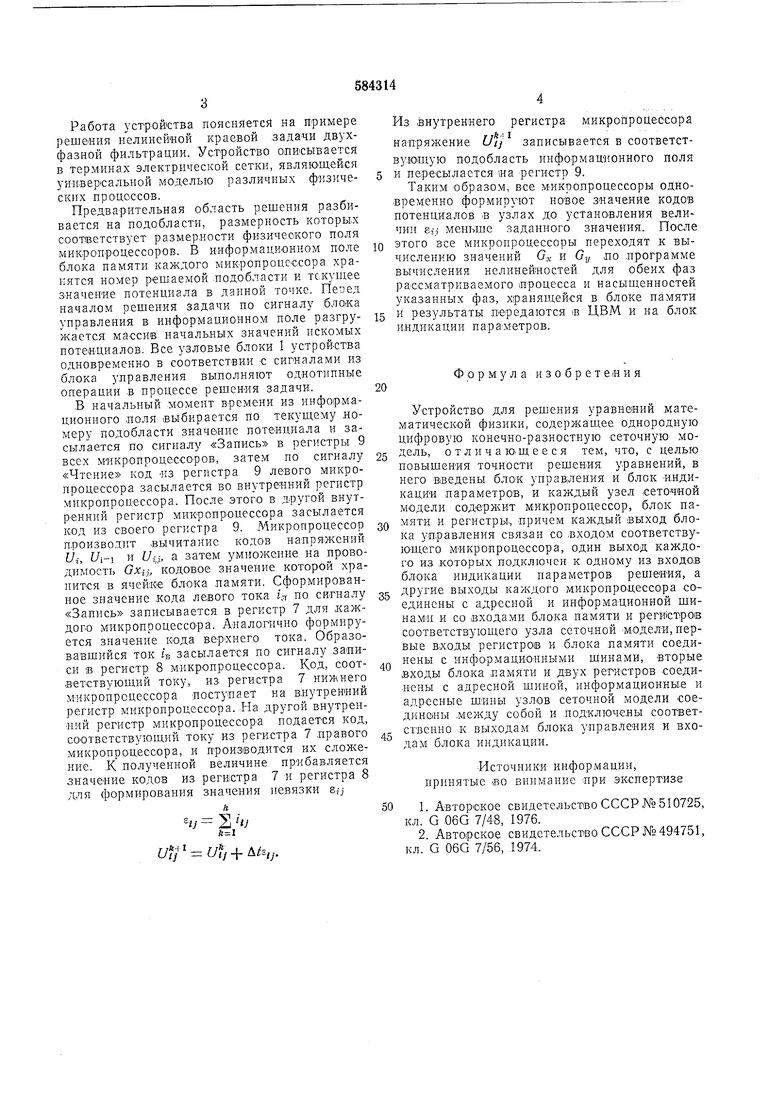

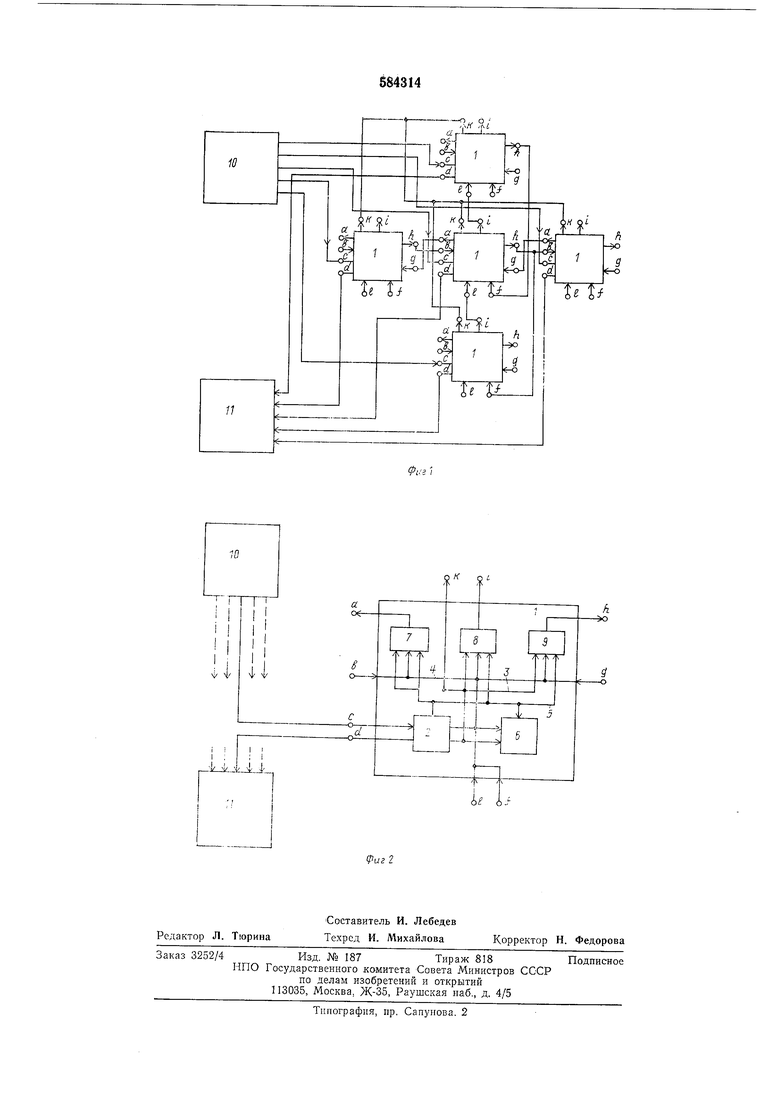

На фи1Г. I представлена блок-схема описываемого устройства; на фиг. 2 - блок-схема

узла сетки.

Устройство имеет стандартные узловые блоки 1, каждый из которых содержит микропроцессор 2, адресную 3, Информационную 4 и записи-чтения 5 шины, блок i6 памяти,

регистр 7 для хранения кода, соответствующего левому току, регистр 8 для хранения кода, соответствующего верхнему току, регистр 9 для хранения кода, соответствующего напряжению в узле, .причем, кроме своего

микропроцессора, регистры 7, 8 и 9 жестко связаны по адресным « информационньгм шинам с выходами четырех соседних микронроцессоров. Кроме того, устройство соде|)жит блок 10 1Иравления всеми узловыми

блоками и блок 11 индикации параметров решения.

Обращение к регистрам соседних узловых блоков 1 производится с ломошью сигналов, задаваемых по адресным шинам 3 данного

|ЗЛ01вого блока 1.

Работа устройства поясняется на примере решения нелинейной краевой задачи двухфазной фильтрации. Устройство описывается в терминах электрической сетки, являющейся уНИверсальной моделью различных физических ИрОЦСССОВ.

Предварительная область решения разбивается на подобласти, размерность которых соответствует размерности физического поля микропроцессоров. В информационном поле блока памяти каждого микропроцессора хранятся номер решаемой подобласти и текущее злачеиие потенциала в данной точке. Перед началом решения задачи по сигналу блока управления в информационном поле разгружается массив начальных значений искомых потенциалов. Все узловые блоки 1 устройства одновременно в соответствии с сигналами из блока управления выполняют однотипные операции в процессе решения задачи.

,В начальный момент времени из информационного поля (Выбирается по текущему номеру подобласти значение потенциала и засылается по сигналу «Запись в регистры 9 всех микропроцессоров, затем по сигналу «Чтение код ИЗ регистра 9 левого микропроцессора засылается во внутренний регистр микропроцессора. После этого в другой внутренний регистр микропроцессора засылается код из своего регистра 9. Микропроцессор производит вычитание кодов напряжений Ui, Ui-i и , а затем умножение на проводимость Gx-ij, кодовое значение которой хранится в ячейке блока памяти. Сформированное значение кода левого тока i но сигналу «Запись записывается в регистр 7 для каждого микропроцессора. Аналогично формируется значение кода верхнего тока. Образовавшийся ток IE засылается по сигналу записи В регистр 8 микропроцессора. Код, соответствующий току, из регистра 7 нижнего М14кронроцессора ноступает на внутренний регистр микропроцессора. J-Ia другой внутренний регистр микропроцессора цодается код, соответствующий току из регистра 7 нравого микронронессора, и производится их сложение. ,К нолучениой величине прибавляется значение кодов из регистра 7 и регистра 8 для формирования значения невязки гц

h.

1} S 1)

+ A/3,.

Из внутреннего регистра микроНроЦессора

Г rft 1

напряжение Uij записывается в соответствующую подобласть информационного поля

и пересылается та регистр 9.

Таким образом, все микропроцессоры одновременно формируют новое значение кодов потенциалов в узлах до установления величии 8г.1 меньше заданиого значения. После

этого все микропроцессоры переходят к вычислению значений GX и Су по программе вычисления нелинейностей для обеих фаз рассматриваемого процесса и насыщенностей указанных фаз, хранящейся в блоке памяти

и результаты передаются IB ЦВМ и на блок индикации пара метров.

Формула изобретения

Устройство для решения уравнений математической физики, содержащее однородную цифровую конечно-разностиую сеточную модель, отличаЮЩееся тем, что, с целью повышения точности решения уравнений, в него введены блок управления и блок нндикациИ параметров, и каждый узел сеточиой модели содержит микропроцессор, блок памяти и регистры,, причем каждый выход блока управления связан со входом соответствующего Микропроцессора, один выход каждого из которых подключен к одному из входов блока индикации параметров решения, а

другие выходы каждого микропро цессора соединены с адресной и информационной шинам1И и со входами блока памяти и регистров соответствующего узла сеточной модели, первые входы регистров и блока памяти соедииены с информационными шинами, вторые входы блока памяти и двух регистров соединены с адресной шиной, информационные и адресные шнны узлов сеточной модели соединены ,между собой и подключены соответсгвенно ,к выходам блока управления и входам блока индикации.

Источиики информации, принятые ;во внимание при экспертизе

1. Авторское свидетельст1во СССР №510725, кл. G .06G 7/48, 1976.

2. Авторское свидетельстсо СССР №494751, кл. G 06G 7/56, ,1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сеточная модель | 1984 |

|

SU1260981A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| Сеточная модель | 1987 |

|

SU1483469A1 |

| Устройство для решения нелинейных краевых задач | 1987 |

|

SU1683028A1 |

| Устройство для решения дифференциальных уравнений | 1983 |

|

SU1269151A1 |

| Устройство для решения краевых задач | 1983 |

|

SU1149286A1 |

| Устройство для решения дифференциальных уравнений в частных производных | 1989 |

|

SU1675911A1 |

| Устройство для решения нелинейных задач теории поля | 1984 |

|

SU1229781A1 |

| Устройство для ввода информации | 1983 |

|

SU1124332A1 |

| Вычислительная система для решения дифференциальных уравнений | 1977 |

|

SU674031A1 |

Авторы

Даты

1977-12-15—Публикация

1976-07-07—Подача