ледовательные цепи 9, соцержав е k ит каскадов. Устройство позволяет обрабатьшать информацию как в параллельном, так и в последовательном

1270890

двоичном коде для любых кодовых комбинаций Использование микросхем средней степени интеграции позволяет удешевить устройство„ 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СИНХРОНИЗАЦИИ НА ОСНОВЕ КОМБИНИРОВАННОГО ПРИМЕНЕНИЯ ДВОЙСТВЕННОГО БАЗИСА ПОЛЯ GF(2) И ВЫДЕЛЕНИЯ "СКОЛЬЗЯЩЕГО ОКНА" С ОШИБКАМИ | 2014 |

|

RU2580806C2 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2012 |

|

RU2480823C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ РЕКУРРЕНТНОЙ ПОСЛЕДОВАТЕЛЬНОСТЬЮ С ФУНКЦИЕЙ ВЫДЕЛЕНИЯ ЗАЧЕТНЫХ ИМПУЛЬСОВ В СКОЛЬЗЯЩЕМ ОКНЕ | 2013 |

|

RU2553089C2 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ОШИБОК В КАНАЛЕ | 2001 |

|

RU2192038C1 |

| Устройство широкодиапазонного логарифмического аналого-цифрового преобразования | 1988 |

|

SU1571763A1 |

| Устройство определения временного положения импульсных сигналов | 1988 |

|

SU1596301A1 |

| Формирователь импульсов | 1986 |

|

SU1383468A1 |

| Устройство для сопряжения источника информации с ЭВМ | 1986 |

|

SU1381528A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

Изобретение относится к,области автоматики и вычислительной техники и может быть использовано в системах управления и обработки информации. Цель изобретения - расширение функци ; ональных возможностей устройства, достигается благодаря- тому, что каждый элемент И дополнен до элемента И-ИЛИ, введены m дополнительных элементов И-ИЛИ, m элементов сравнения, m дополнительных элементов задержки, Dтриггеры 4, 5, инвертор 6, п-разрядс В ; ный универсальньй сдвиговьй регистр 8. При этом все элементы И-ИЛИ И-НЕ и элементы задержки объединены в посЮ О 00 00

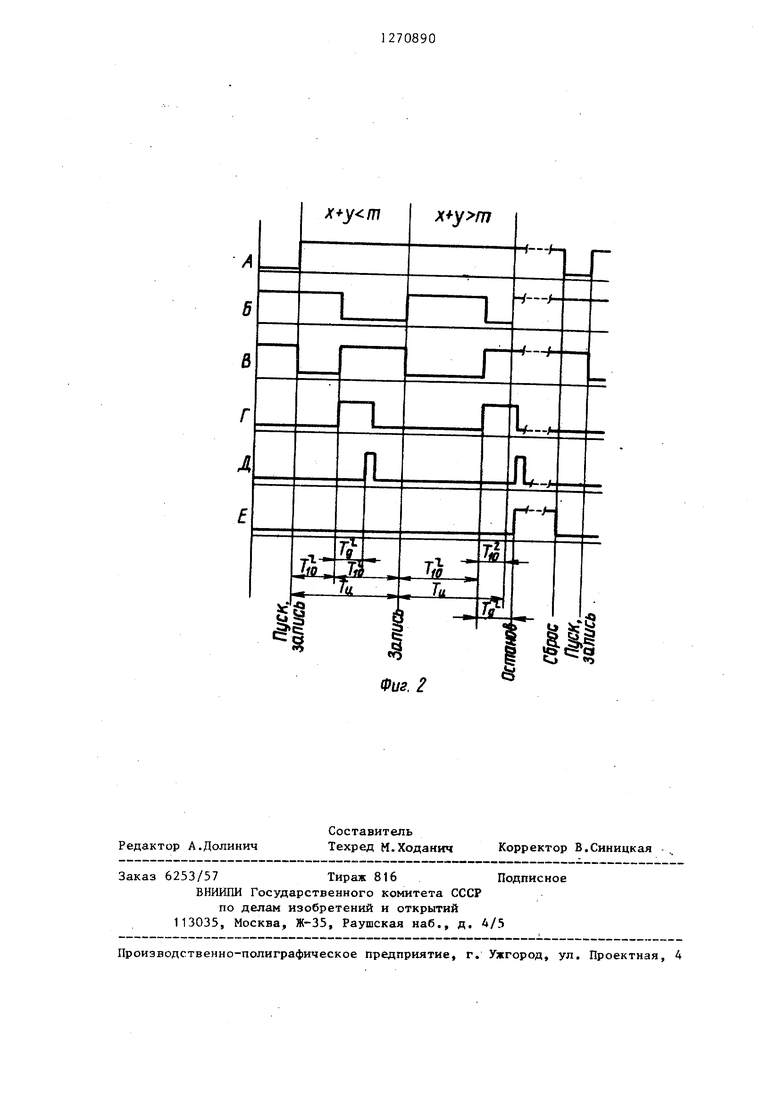

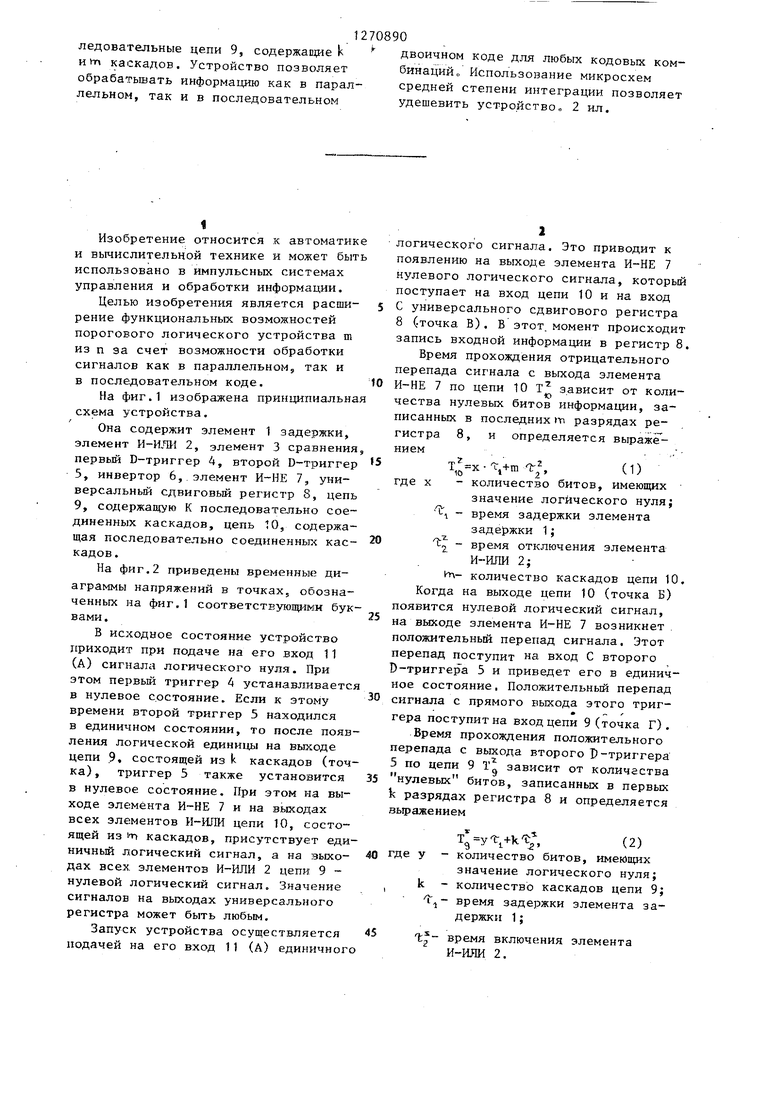

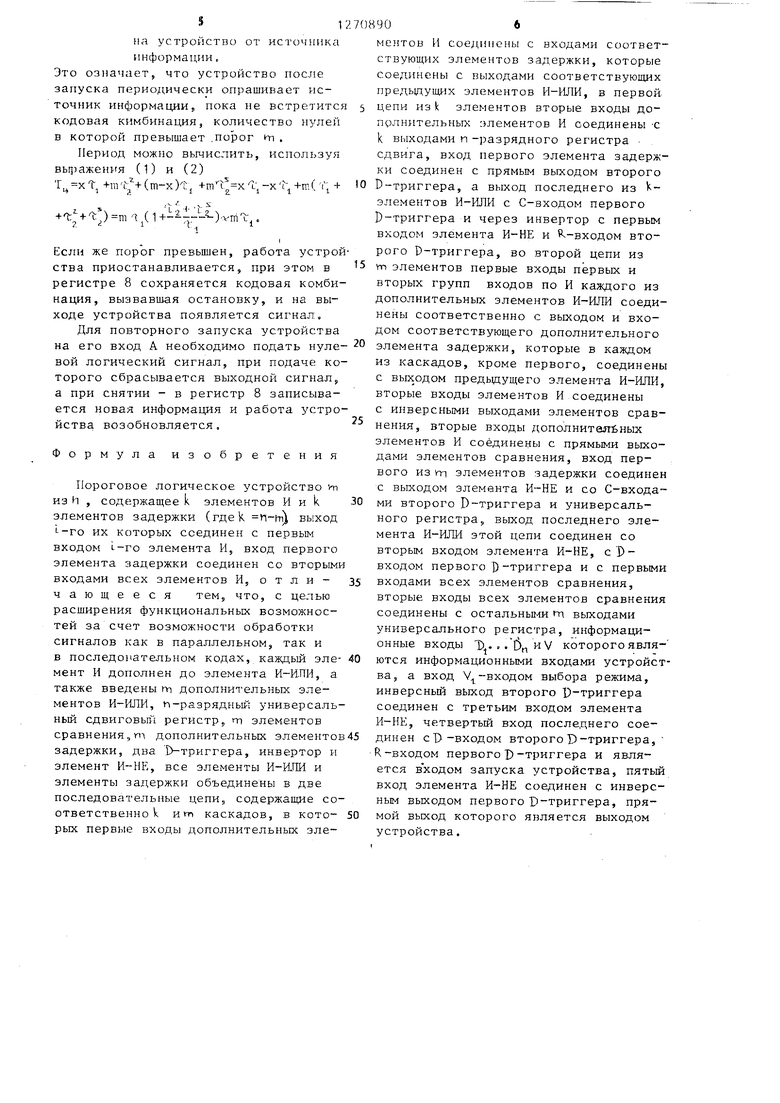

Изобретение относится к автоматик и вычислительной технике и может быт использовано в импульсных системах управления и обработки информации. Целью изобретения является расширение функциональных возможностей порогового логического устройства m из п за счет возможности обработки сигналов как в параллельном, так и в последовательном коде. На фиг.1 изображена принципиальна схема устройства. Она содержит элемент 1 , элемент И-ИЛИ 2, элемент 3 сравнения первый D-триггер 4, второй В-т)эиггер 5, инвертор 6, элемент И-НЕ 7, универсальный сдвиговьй регистр 8, цепь 9, содержащую К последовательно соединенных каскадов, цепь 10, содержащая последовательно соединенньк каскадов. На фиг.2 приведены временные диаграммы напряжений в точках, обозначенных на фиг.1 соответствующими бук вами. В исходное состояние устройство приходит при подаче на его вход 11 (А) сигналг логического нуля. При этом первый триггер 4 устанавливаетс в нулевое состояние. Если к этому времени второй триггер 5 находился в единичном состоянии, то после появ ления логической единицы на выходе цепи 9, состоящей из k каскадов (точ ка) , триггер 5 также установится в нулевое состояние. При этом на выходе элемента И-НЕ 7 и на выходах всех элементов И-ИЛИ цепи 10, состоящей из 1п каскадов, присутствует еди ничньш логический сигнал, а на выходах всех элементов И-ИЛИ 2 цепи 9 нулевой логический сигнал. Значение сигналов на выходах универсального регистра может быть любым. Запуск устройства осуществляется подачей на его вход 11 (А) единичног огического сигнала. Это приводит к появлению на выходе элемента И-НЕ 7 нулевого логического сигнала, который поступает на вход цепи 10 и на вход С универсального сдвигового регистра 8 (точка В), В этот, момент происходит запись входной информации в регистр 8. Время прохождения отрицательного перепада сигнала с выхода элемента И-НЕ 7 по цепи 10 Т зависит от количества нулевых битов информации, записанных в последних t-n разрядах регистра 8, и определяется выражёнием ,. ., . (1) где X - количество битов, имеющих значение логического нуля; - время задержки элемента задержки 1; 2 - время отключения элемента И-ИЛИ 2; Ил- количество каскадов цепи 10. Когда на выходе цепи 10 (точка Б) появится нулевой логический сигнал, на выходе злемента И-НЕ 7 возникнет положительный перепад сигнала, Этот перепад поступит на вход С второго D-триггера 5 и приведет его в единичное состояние, Положительный перепад сигнала с прямого выхода этого триггера поступит на вход цепи 9 (точка Г) . Время прохождения положительного перепада с выхода второго Р-триггера 5 по цепи 9 1 зависит от количества нулевых битов, записанных в первых k разрядах регистра 8 и определяется зьгражением , 2) где у - количество битов, имеющих значение логического нуля; I k - количество каскадов цепи 9; .j - время задержки элемента задержки 1; время включения элемента И-ИЛИ 2.

Время прохождения положительного перепада напряжения с выхода элемента

10 Т определяется И-НЕ 7 по цепи

п

количеством единичных битов информации, записанных в m разрядах регистра 8, так как теперь на выходе цепи 10 (точка Б) и соответственно на первых входах элементов 3 сравнения присутствует сигнал логического нуля, Это время определяется по формуле

Tj(tn-x) t. (3) Если 1д меньше чем Т,, то положительньй перепад напряжения с выхода цепи 9 на вход С первого Т)-триггера 4поступит раньше, чем на егоВ-вход придет сигнал логической единицы с выхода цепи 10, и триггер 4 не изменит своего состояния. В то же время сигнал логического нуля с выхода инвертора 6 установит второй D-триггер 5в нулевое состояние, что приводит к появлению сигнала логического нуля на выходе цепи 9 (точка Д) и сигнала логической единицы-на выходе инвертора 6. При этом на выходе 12 элемента И-НЕ 7 (точка В) вновь возникает отрицательный перепад сигнала, в регистр 8 запишется новая информация и цикл работы устройства повторится. Если же окажется, что Т больше, чем Т, то сигнал логической единицы на выходе цепи 10 появится раньше, чем на выходе цепи 9. Тогда в момент появления положительного перепада напряжения с выхода цепи 9 (точка Д) на входе первого D-триггера 4, последний перейдет в единичное состояние, так как на его D-вход в этот момент поступает сигнал логической единицы с выхода цепи 10 (точка Б). С инверсного выхода первого триггера 4 на пятый вход элемента И-НЕ 7 поступит сигнал логического нуля, который запрещает появление на выходе элемента И-НЕ 7 сигнала логического нуля, после того, как произойдет сброс в нулевое состояние второго I)триггера 5 и на выходе инвертора 6 вновь появится сигнал логической единицы. Работа устройства приостанавливается до момента появления на входе А устройства сигнала логического нул Наличие сигнала логической единицы на выходе первого D-триггера 4 (точка Е), который является выходом устройства означает, что в регистре 8 записано « -разрядное двоичное число, код которого содержит количество нулевых битов, превышающее число ту.

При подаче на вход А устройства сигнала логического нуля первый D триггер 4 устанавливается в нулевое состояние и устройство приходит в исходное состояние.

Новая двоичная информация записывается в регистр 8 в момент появления на входе А единичного сигнала. Запись входной информации может осуществляться двумя различными способами, в зависимости от сигнала, поданного на вход Vj выбора режима работы регистра 8.Если на вход V подан сигнал логического нуля - работа в параллельном коде, то на выходы регистра 8 переписывается П-разрядный двоичный код, который присутствует на входах р.. . момент появления отридательного перепада на входе С регистра 8. Если же на вход V| подан единичный логический сигнал - -работа в последовательном коде, то ранее записанная информация сдвигается на один разряд, а в первый разряд регистра 8 заносит бит информации с входаУ . Независимо от режима работы устройства, цикл работы устройства будет постоянен и равен т.е. период У Следования отрицательных импульсов с выхода элемента И-НЕ 7 (точка В) при непрерывной циклической работе устройства, когда выполняется условие Т.. Т ло 9 . Подставляя в это условие вьфажения для Т, т|, (см. выражения 2 и 3 описания) получим (т-х)ц+тТ 2 - niT.i(x+ +y) + (k-m)l, Если выбрать время задержки элемента 1 задержки так, чтобы выполнялось неравенство | (t-m) 0,5i|, то время отклонения элемента И-ИЛИ . 2 -Т| можно не учитывать, и условие непрерывной циклической работы устройства примет вид L-i(x+y)T m т.е. m х+у, где m - число, характеризующее порог срабатывания устройстт ва, равное числу каскадов цепи 10; х+у - общее количество битон, имеющих значение логического нуля в h-разрядном двоичном коде, поступившем

на устройство от источника

информации.

Это означает, что устройство после запуска периодически опрашивает источник информации, пока не встретится кодовая кимбинация, количество нулей в которой превышает .порог Ип , Период можно вычислить, используя вы1)ажения (1) и (2) Т х Т, +111 (m-x)t +т1 х - -х ц +т( i + л , Ч 1 )-vniТ, Если же порог превышен, работа устрой ства приостанавливается, при этом в регистре 8 сохраняется кодовая комбинация, вызвавшая остановку, и на выходе устройства появляется сигнал. Для повторного запуска устройства на его вход А необходимо подать нулевой логический сигнал, при подаче ко торого сбрасывается выходной сигнал, а при снятии - в регистр 8 записывается новая информация и работа устро йства возобновляется, Формула изобретения Пороговое логическое устройство vn из h , содержащее k элементов И и k элементов задержки (где К l-m выход L-ro их которых соединен с первым входом L-ro элемента И, вход первого элемента задержки соединен со вторыми входами всех элементов И, о т л и чающееся тем, что, с целью расширения функциональных возможностей за счет возможности обработки сигналов как в параллельном, так и в последо11ательном кодах, каждый эле мент И дополнен до элемента И-ИЛИ, а также введены m дополнительных элементов И-ИЛИ, п-разрядный универсаль ный сдвиговый регистр, m элементов сравнения , п-( дополнительных элементо задержки, два D-триггера, инвертор и элемент И--НЕ, все элементы И-ИЛИ и элементы задержки объединены в две последовательные цепи, содержащие со ответственно k игл каскадов, в которых первые входы дополнительных элемснтов И соединены с входами соответствующих элементов задержки, которые соединены с ВЕлходами соответствующих предыдущих элементов И-ИЛИ, в первой цепи из k элементов вторые входы дополнительных элементов И соединены -с k выходами п -1эазрядного регистра сдвига, вход первого элемента задержки соединен с прямым выходом второго D-триггера, а выход последнего из l-элементов И-ИЛИ с С-входом первого р-триггера и через инвертор с первым входом элемента И-НЕ и --входом второго Р-триггера, во второй цепи из уп элементов первые входы первых и вторых групп входов по И каждого из дополнительных элементов И-ИЛИ соединены соответственно с выходом и входом соответствующего дополнительного элемента задержки, которые в каждом из каскадов, кроме первого, соединены с выходом предыдущего элемента И-ИЛИ, вторые входы элементов И соединены с инверсными выходами элементов сравнения, вторые входы дополниталбных элементов И соединены с прямыми выходами элементов сравнения, вход первого из УП элементов задержки соединен с выходом элемента И-НЕ и со С-входа ми второго D-триггера и универсального регистра, выход последнего элемента И-ИЛИ этой цепи соединен со вторым входом элемента И-НЕ, с )входом первого )-триггера и с первыми входами всех элементов сравнения, вторые входы всех элементов сравнения соединены с остальными m выходами универсального регистра, информационные входы 1). ,.6г,иУ которогоявляются информационными входами устройства, а вход V -входом выбора режима, инверсный вьгход второго 1)-триггера соединен с третьим входом элемента И-НЕ, четвертый вход последнего соединен сD-входом второгоР-триггера, R-входом первогоD-триггера и является входом запуска устройства, пятый вход элемента И-НЕ соединен с инверсным выходом первого D-триггера, прямой выход которого является выходом устройства.

Фиг. 2

| Пороговый логический элемент | 1979 |

|

SU818016A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Логическое устройство из | 1979 |

|

SU818017A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-11-15—Публикация

1985-06-19—Подача