«. 12

Изобретение -относится к цифровой Бычислительной технике и может быть использовано при проектировании арифметических устройств ЦВМ,

Цель изобретения - упрощение сум- матора.

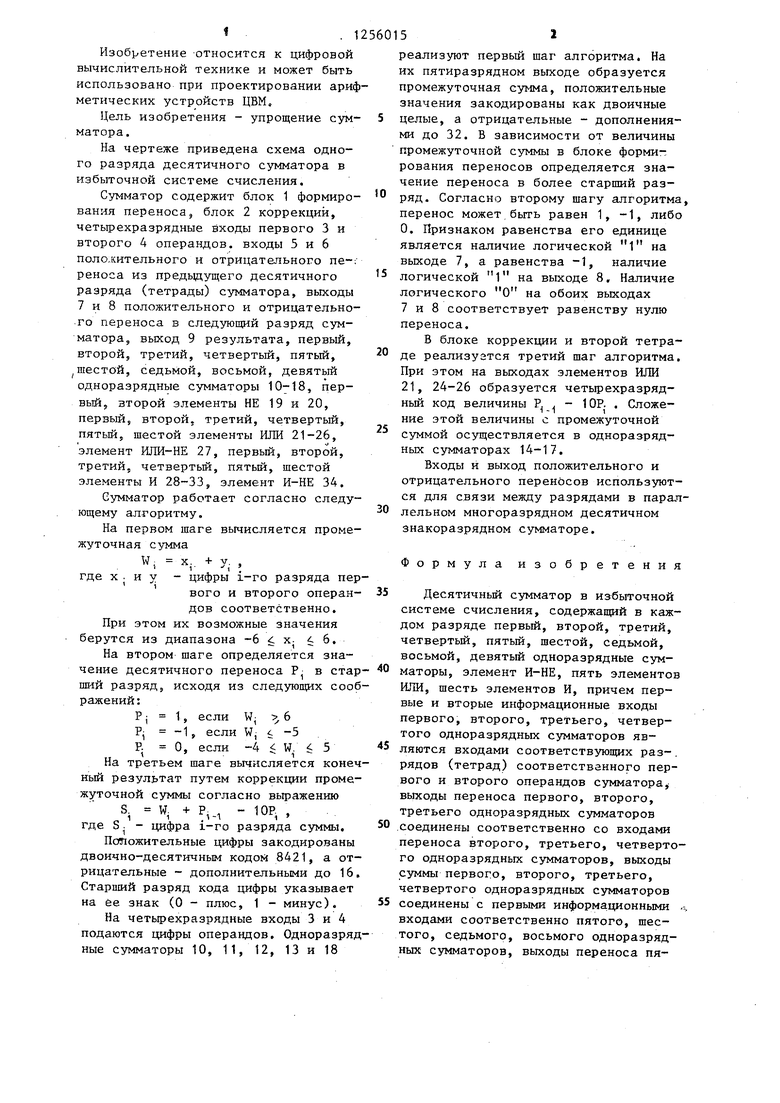

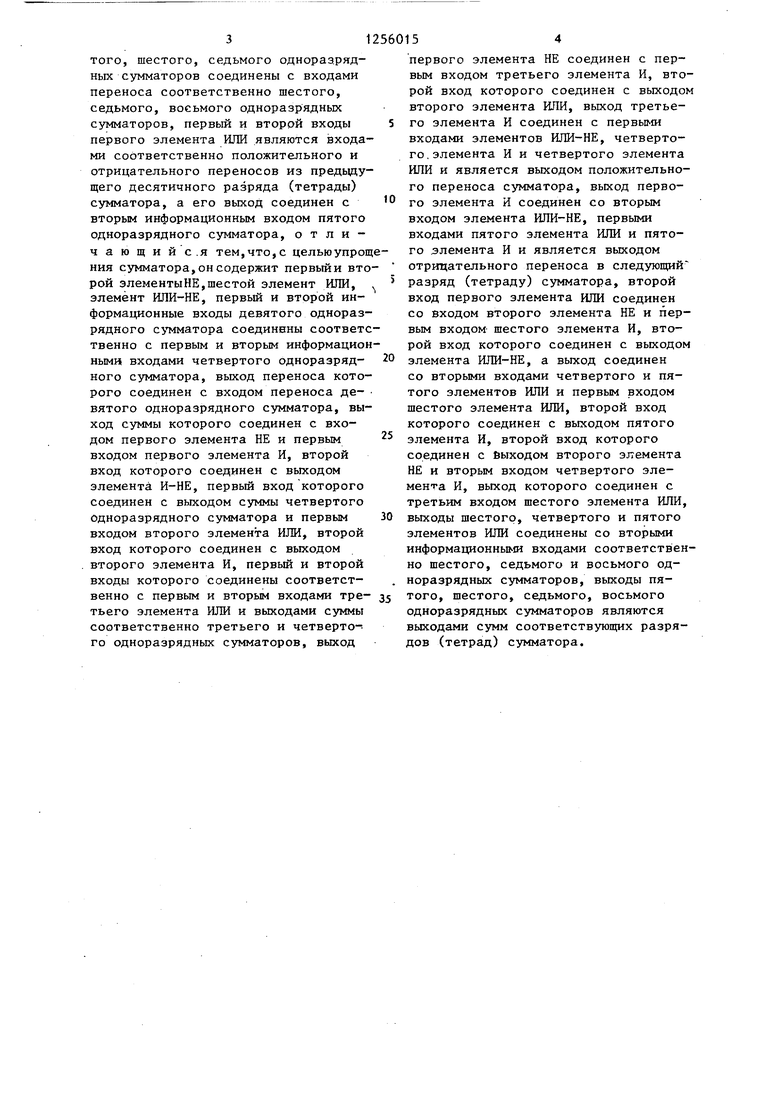

На чертеже приведена схема одного разряда десятичного сумматора в избыточной системе счисления.

Сумматор содержит блок 1 формиро- вания переноса, блок 2 коррекций, четырехразрядные входы первого 3 и второго 4 операндов, входы 5 и 6 поло.кительного и отрицательного пе-г реноса из предьщущего десятичного разряда (тетрады) сумматора, выходы 7 и 8 положительного и отрицательно- го переноса в следующий разряд сумматора, выход 9 результата, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый одноразрядные сумматоры 10-18, первый, второй элементы НЕ 19 и 20, первый, второй, третий, четвертый, пятый, шестой элементы ИЛИ 21-26, элемент ИЛИ-НЕ 27, первый, второй, третий, четвертьй, пятьй, шестой элементы И 28-33, элемент И-НЕ 34.

Сумматор работает согласно следующему алгоритму.

На первом шаге вычисляется промежуточная сумма

, W, X.. + у. ,

где X . и у - цифры i-ro разряда первого и второго операн- дов соответственно. При этом их возможные значения берутся из диапазона -6 х .6.

На втором шаге определяется значение десятичного переноса Р в стар пшй разряд, исходя из следуюш;их соображений:

Р j 1, если W; , 6

1

-1, если W, -5

Р. О, если -4 W. 5 На третьем шаге вычисляется конечный результат путем коррекции промежуточной суммы согласно выражению

S, W, + Р,-. - ЮР. . где S. - цифра 1-го разряда суммы.

Положительные цифры закодированы двоично-десятичным кодом 8421, а отрицательные - дополнительными до 16 Старший разряд кода цифры указывает на ее знак (О - плюс, 1 - минус).

На четырехразрядные входы 3 и 4 подаются цифры операндов. Одноразрядные сумматоры 10, 11, 12, 13 и 18

5

0

5

5

5

реализуют первый шаг алгоритма. На их пятиразрядном выходе образуется промежуточная сумма, положительные значения закодированы как двоичные целые, а отрицательные - дополнениями до 32. В зависимости от величины промежуточной суммы в блоке формирования переносов определяется значение переноса в более старший разряд. Согласно второму шагу алгоритма, перенос может быть равен 1, -1, либо 0. Признаком равенства его единице является наличие логической 1 на выходе 7, а равенства -1, наличие логической 1 на выходе В, Наличие логического О на обоих выходах 7 и 8 соответствует равенству нулю переноса.

В блоке коррекции и второй тетраде реализуется третий шаг алгоритма. При этом на выходах элементов ИЛИ 21, 24-26 образуется четырехразрядный код величины Р - 10Р. . Сложение этой величины с промежуточной суммой осуществляется в одноразрядных сумматорах 14-17.

Входы и выход положительного и отрицательного переносов используются для связи между разрядами в параллельном многоразрядном десятичном знакоразрядном сумматоре.

Формула изобретения

Десятичный сумматор в избыточной системе счисления, содержащий в каждом разряде первый, второй, третий, четвертый, пятьй, шестой, седьмой, восьмой, девятый одноразрядные сумматоры, элемент И-НЕ, пять элементов ИЛИ, шесть элементов И, причем первые и вторые информационные входы первого, второго, третьего, четвертого одноразрядных сумматоров являются входами соответствующих раз-. рядов (тетрад) соответственного первого и второго операндов сумматора, выходы переноса первого, второго, третьего одноразрядньк сумматоров .соединены соответственно со входами переноса второго, третьего, четвертого одноразрядных сумматоров, выходы суммы первого, второго, третьего, четвертого одноразрядных сумматоров соединены с первыми информационными ,, входами соответственно пятого, шестого, седьмого, восьмого одноразрядных сумматоров, выходы переноса пятого, шестого, седьмого одноразрядных сумматоров соединены с входами переноса соответственно шестого, седьмого, восьмого одноразрядных сумматоров, первый и второй входы первого элемента ИЛИ являются входа- ми соответственно положительного и отрицательного переносов из предыдущего десятичного разряда (тетрады) сумматора, а его выход соединен с вторым информационным входом пятого одноразрядного сумматора, о т л и - чающийс.я тем,что,с цельюупрощ ния сумматора,он содержит первыйи второй элементыНЕ,шестой элемент ИЛИ, элемент Ш1И-НЕ, первый и второй информационные входы девятого одноразрядного сумматора соединены соответственно с первым и вторым информационными входами четвертого одноразрядного сумматора, выход переноса которого соединен с входом переноса де- вятого одноразрядного сумматора, выход суммы которого соединен с входом первого элемента НЕ и первым входом первого элемента И, второй вход которого соединен с выходом элемента И-НЕ, первый вход которого соединен с выходом суммы четвертого одноразрядного сумматора и первым входом второго элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, первый и второй входы которого соединены соответственно с первым и вторым входами третьего элемента ИЛИ и выходами суммы соответственно третьего и четверто-- го одноразрядных сумматоров, выход

е-

10

5

20

25

30

35

с пер- И, ВТО- выходом

2560154

первого элемента НЕ соединен вым входом третьего элемента рой вход которого соединен с второго элемента ИЛИ, выход третьего элемента И соединен с первыми входами элементов ИЛИ-НЕ, четвертого, элемента И и четвертого элемента ИЛИ и является выходом положительного переноса сумматора, выход первого элемента И соединен со вторым входом элемента Ш1И-НЕ, первыми входами пятого элемента ИЛИ и пятого элемента И и является выходом отрицательного переноса в следующий разряд (тетраду) сумматора, второй вход первого элемента ИЛИ соединен со входом второго элемента НЕ и первым входом шестого элемента И, второй вход которого соединен с выходом элемента ИЛИ-НЕ, а выход соединен со вторыми входами четвертого и пятого элементов ИЛИ и первым входом шестого элемента ИЛИ, второй вход которого соединен с выходом пятого элемента И, второй вход которого соединен с быходом второго элемента НЕ и вторым входом четвертого элемента И, выход которого соединен с третьим входом шестого элемента ИЛИ, выходы шестого, четвертого и пятого элементов ИЛИ соединены со вторыми информационными входами соответственно шестого, седьмого и восьмого одноразрядных сумматоров, выходы пятого, шестого, седьмого, восьмого одноразрядных сумматоров являются выходами сумм соответствующих разрядов (тетрад) сумматора.

Редактор П.Коссей

Составитель М.Есенина

Техред Л.Сердюкова Корректор А.Обручар

Заказ 4824/48Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий . 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Десятичный сумматор в избыточной системе счисления | 1988 |

|

SU1594524A1 |

| Двоично-десятичный сумматор | 1985 |

|

SU1305664A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1234831A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| Устройство для умножения двоично-десятичных цифр | 1983 |

|

SU1198513A1 |

| Устройство для сложения - вычитания | 1985 |

|

SU1273918A1 |

| Операционный модуль | 1984 |

|

SU1406592A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU955039A1 |

Изобретение относится к области вычислительной техники и автоматики. Цель изобретения - упрощение сумматора. Каждый разряд десятичного суматора содержит девять рднооб- р.азных сумматоров, два элемента НЕ, шесть элементов ИЛИ, элемент ИЛИ-НК, элемент И-НЕ, шесть элементов И. Отличительная особенность заключается в наличии блока коррекции в струг: ктуре десятичного знакораэрядного сумматора вместо трехразрядного двоичного сумматора. Благодаря этому в каждом разряде предлагаемого десятичного знакоразрядного сумматора аппаратурные затраты ниже, чем в Прототипе более чем на два двоичных сумматора, 1 ил. (Л IND Сл 0

| Двоично-десятичный сумматор | 1981 |

|

SU1019441A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Рабинович З.Л., Раманаускас В.Л | |||

| Типовые операции в вычислительных машинах | |||

| Киев: Техника, 1980, с | |||

| Плуг с фрезерным барабаном для рыхления пласта | 1922 |

|

SU125A1 |

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

Авторы

Даты

1986-09-07—Публикация

1985-04-03—Подача