f

-(21) 4462590/24-24 (22) 20.07.88 (46) 23.09.90. Бюл. № 35

(71)Кишиневский политехнический институт им. С.Лазо

(72)В.С.Гыскэ и Л.Т.Кирьяк (53) 681.325 (088.J)

(56) Авторское свидетельство СССР № 924698, кл. G 06 F 7/49, 1980.

Авторское свидетельство СССР № 1019441, кл. G 06 F 7/50, 1981.

Рабинович Я.П., Раманаускас В.А. Типовые операции в вычислительных машинах. - Киёв: Техника, 1980 с. 125, рис. 17.

Авторское свидетельство СССР № 1256015, кл. G 06 F 7/40,.1985.

(54) ДЕСЯТИЧНЕЙ СУММАТОР В ИЗБЫТОЧНОЙ CHCTEIffi СЧИСЛЕНИЯ

(57) Изобретение относится к вычислительной технике и может быть использовано при проектировании арифметических устройств цифровых ЭВМ. Цель изобретения - упрощение cyi waTo- ра. Кавдый разряд десятичного сумматора в избыточной системе счисления содержит восемь одноразрядных сумматоров, девять элементов И, гаесть элементов ИЛИ, элемент И-НЕ, элемент Ш1И-НЕ, три элемента НЕ. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Десятичный сумматор в избыточной системе счисления | 1985 |

|

SU1256015A1 |

| Двоично-десятичный сумматор | 1985 |

|

SU1305664A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 1993 |

|

RU2069009C1 |

| Многофункциональное арифметико-логическое устройство | 1985 |

|

SU1259247A1 |

| Сумматор в знакоразрядной позиционно-остаточной системе счисления | 1986 |

|

SU1383349A1 |

| Универсальное суммирующее устройство | 1990 |

|

SU1786484A1 |

| Конвейерный сумматор | 1983 |

|

SU1137460A1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU955039A1 |

| Устройство для сложения - вычитания | 1985 |

|

SU1273918A1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании арифметических устройств цифровых ЭВМ. Цель изобретения - упрощение сумматора. Каждый разряд десятичного сумматора в избыточной системе счисления содержит восемь одноразрядных сумматоров, девять элементов И, шесть элементов ИЛИ, элемент И-НЕ, элемент ИЛИ-НЕ, три элемента НЕ. 1 ил.

Изобретение относится к цифровой вычислительной технике и может быть использовано при проектировании арифметических устройств цифровых ЭВМ.

Цель изобретения - упрощение сумматора.

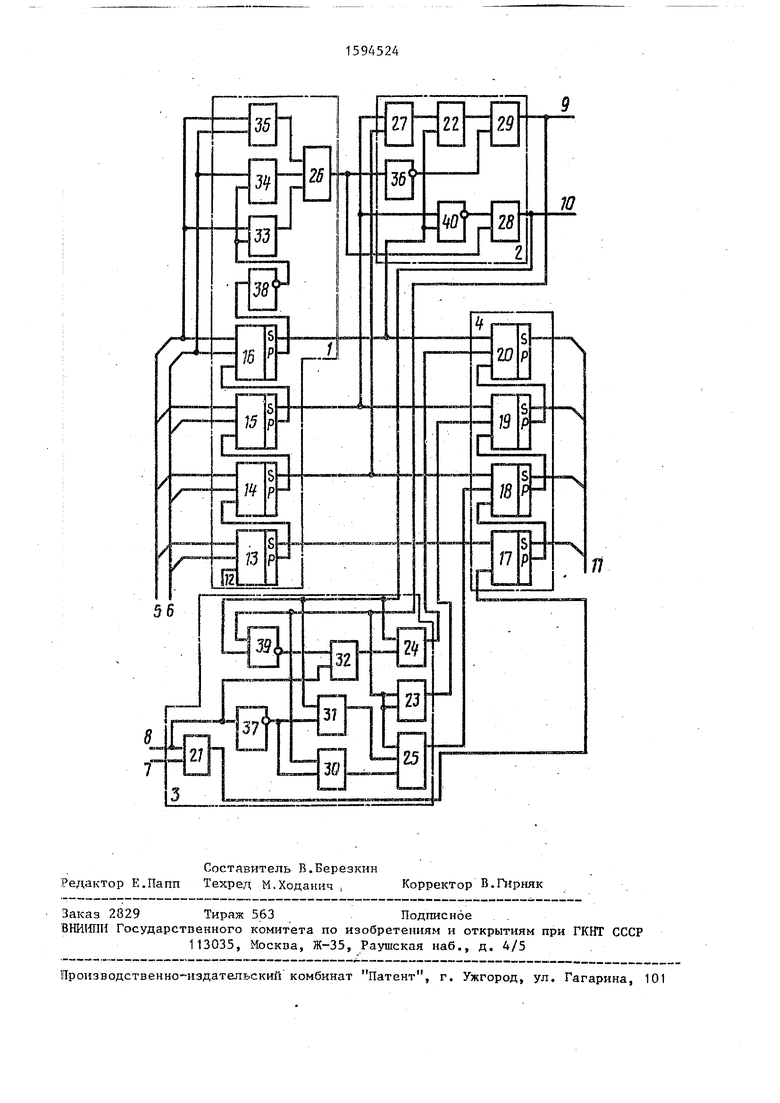

На чертеже приведена схема одного разряда десятичного сумматора в избыточной системе счисления.

Сумматор содержит блок 1 формирования промежуточного результата, блок 2 формирования переноса, блок 3 коррекции, блок 4 формирования конечного результата, четырехразрядные входы первого 5 и второго 6 операндов, входы 7 и 8 положительного и отрицательного переноса из предыдущего десятичного разряда сумматора, выходы 9 и 10 положительного и отрицательного переноса в следующий разряд сумматора, четырехразрядный выход 11 : суммы и управляющий вход 12 определения операции, одноразрядные сумматоры 13-20, элементы ИЛИ 21 - 26, элементы И 27 - 35, элементы НЕ 36 - 38, элемент ИЛИ-НЕ 39 и элемент И-НЕ 40. Лесятичньп сумматор в избыточной системе счисления работает согласно следующему алгоритму.

На первом этапе вычисляется промежуточный результат

Wj Х;± У

«У I

где X j и .- ( - тцгфры i-ro разряда первого и второго операндов соответственсл

сд

rsD

fu

no. При этом они представляготся в десятичной избыточной знакоразрядной системе с шслення и принимают значения из диапазона -б Х f,

На втором шаге определяется значение десятичного переноса в старишь разряд исходя из следуюрщх соображений:

Р

если W j 6 J

PJ -1, если W- : 5 ; Г; О, если -4 Wj 5, На третьем шаге вычисляется конеч Hbiff результат путем корректщи промежуточной суммы согласно выражению

Wj + Р J., - 10 Р,

где S- - i-ro разряда суммы.

Положительные цифры закодированы двоично-десятичным кодом 8421, а отрицательные - дополненияьм до 16, Старшш разряд кода указывает на €;е знак (О - плюс, 1 - минус).

.На четырехразрядные входы 5 и 6 подаются 1ЩФРЫ операндов. При выполнении сложеш1я цифры операндов подаются бе изменений, и на управляющей вход 12 подается логический О, При выполнении вычитания цифры уменьшаемого подаются на четырехразрядный вход 5 без изменений, а щлЬра вычитаемого - на четырехразрядный вход 6 в обратном коде. При этом на управляю П7 Й вход 12 подается логическая 1. Тем самым реализуется изменение знака цифр вычитаемого на обратный, так КПК вычитание знакоразрядных чисел осуществляется как сложение согласно следующему выраженик Х; - Y,. X j (-Yi). Блок 1 формирования промезтуточно- го результата, состоягуга из однораз- ркцпък сумматоров 13-16, логических элементов И 33-35j логического элемента НЕ 38 и логического элемента . ИГМ 26, реализует первый шаг алгоритма. На Bbtxo/tax одноразрядных сумматоров 13-16 и логического элемента ИЛИ 26 образуется гштиразрядный щюмеж-уточный результат, Положитель- ные значения закодированы как дво- ич1-1ые , а отрицательные - дополнениями до 32,

В зависимости от величины промежуточного результата в блоке 2 фор- мировашш переноса, состоящем из логических элементов И 27-29, логического элемента НИИ 22, логического эмента НЕ 36 и логического элемента И-НЕ 40, определяется значение.пенаО

5

0

5

0

5

0

45

реноса в следуюпрсй старгшй десятичный разряд. Согласно второму шагу алгоритма перенос может быть равен 1, 1 либо 0. Признаком равенства его единице является наличие логической 1 на выходе 9, .а равенства -1 - наличие логической 1 выходе 10. Наличие логического на обоих выходах 9 и 10 соответствует равенству нулю переноса.

В блоке 3 коррекции, cocтoяJ geм из логических элементов И 30-32, ИЛИ 21, 23-25, логического элемента НЕ 37 и логического элемента ИЛИ-НЕ 39, определяется величина Р-Ю Ее четырехразрядный код образуется на выходах элементов ИЛИ 21, . Сложение этой величины с промежуточным результатом осу дествляется в блоке 4 формирования конечного результата, состоящем ий одноразрядных сумматоров 17-20, Тем самым в блоках 3 и 4 (коррек1щи и формирования - конечного результата) реал1 зуется третий шаг алгоритма.

Входы к выходы положительного и отрицательного переносов используются для связи между разрядами в параллельном многоразрядном десятичном сумматоре в избыточной знакоразряд- ной системе С1шсления,

Рассмотрим пример сложений десятичных знакоразрядных чисел по выше приведенному алгоритму. Значения операндов в обычном десятичном представлении равны X 26345, а Y 18094.В знакоразрядном представлении их значения соответственно равны X 34345, Y. 22П4.

Номер разряда

Операнд X

Операнд Y

Промеж:уточиый

резуль.тат

Перенос

Коррекгр я

Окончательный

результат

4 4 4 4 Т

В обычном десятичном представлении результат вычислений будет равен 44439, что подтверждает правильность приведенного алгоритма.

Формула изобретения

Лесятичньй сумматор в избыточной системе счисления, содержагщ й в каждом разряде первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой одноразрядные сумматоры, шесть элементов И, шесть элементов ИЛИ, два элемента НЕ, элемент И-НЕ, элемент ИЛИ-НЕ, причем первые и вторые информационные входы первого, второго, третьего, четвертого одноразрядных сумматоров являются входами соответствукзргнх разрядов соответственно первого и второго операндов сумматора, выходы переноса первого, второго, третьего одноразрядных сумматоров соединены соответственно с входами переноса второго, третьего, четвертого одноразрядных сумматоров, выходы суммы первого, втрого, третьего, четвертого одноразрядных сумматоров соединены с первы- MSi информационными входами соответственно пятого, шестого, седьмого, восьмого одноразрядных сумматоров, выходы переноса пятого, шестого, седьмого одноразрядных сумматоров соединены с входа и переноса соот- вественно шестого седьмого, восьмого одноразрядных сумматоров, первый и второй входы первого элемента ИЛИ являются входами соответственно положительного и отрицательного переносов из предьщутцего десятичного разряда сумматора, а его выход соединен с вторым информационным входом пятого одноразрядного сумматора, первый и второй входы первого элемента И соединены с выходами суммы соответст венно второго и третьего одноразрядных сумматоров, а его выход соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом суммы четвертого одноразрядного сумматора и первым входом элемента И-НЕ, второй вход которого соединен с выходом суммы третьего одноразрядного С5Т матора, а выход соединен с первым входом второго элемента И, второй вход которого соединен с входо первого элемента НЕ, выход которого соединен с первым входом третьего элемента И, второй вход которого соединен с выходом второго элемента ИЛИ, а выход является выходом поло1

о -н , м

15945

10

15

20

5

жительного переноса суммато эа и соединен с первыми входами элемента ШШ- НЕ, четвертого элемента И и третьего элемента ИЛИ, выход второго элемента И соединен с вторым входом элемента ИЛИ-НЕ, первыми входами пятого элемента И и четвертого элемента ИЛИ и является выходом отрицательного переноса в следуют ий десятичный разряд сумматора, второй вход первого элемента lUDi соединен с входом второго элемента НЕ и первьм входом шестого элемента И, второй вход которого соединен с выходом элемента ИЛИ-НЕ, а выход соединен с вторыми входами третьего и четвертого элементов ИЛИ и первым входом пятого элемента ИЛИ, второй вход которого соединен с выходом пятого элемента И, второй вход которого соединен с выходом второго элемента НЕ и вторым входом четвертого элемента И, вьосод которого соединен с третьим входом пятого элемента ИЛИ, выходы пятого, третьего и четвертого элементов ИЛИ соединены с вторыми информа1щонными входами соответственно шестого, седьмого и восьмого одноразрядных сумматоров, выходы суммы пятого, шестого, седьмого и восьмого одноразрядных сумматоров являются выходами сумм соответ- ствуюцих разрядов сумматора, о т- личаюгцийся тем, что, с целью упрощешм сумматора, он содерзшт седьмой, восьмой и девятый элементы И, третий элементы НЕ, выход переноса четвертого одноразрядного сумматора соединен с входом третьего элемента НЕ, выход которого соединен с первыми входами седьмого и восьмого элементов И, вторые входы которых соединены соответственно с первым и вторым информационными входа- j ми четвертого одноразрядного сумматора и с первым и вторым входами девятого элемента И, выходы седьмого, восьмого и девятого элементов И соединены соответственно с первым, 0 вторым и третьим входами шестого элемента ИЛИ, выход которого соединен с входом первого элемента НЕ,

0

5

0

як

Авторы

Даты

1990-09-23—Публикация

1988-07-20—Подача