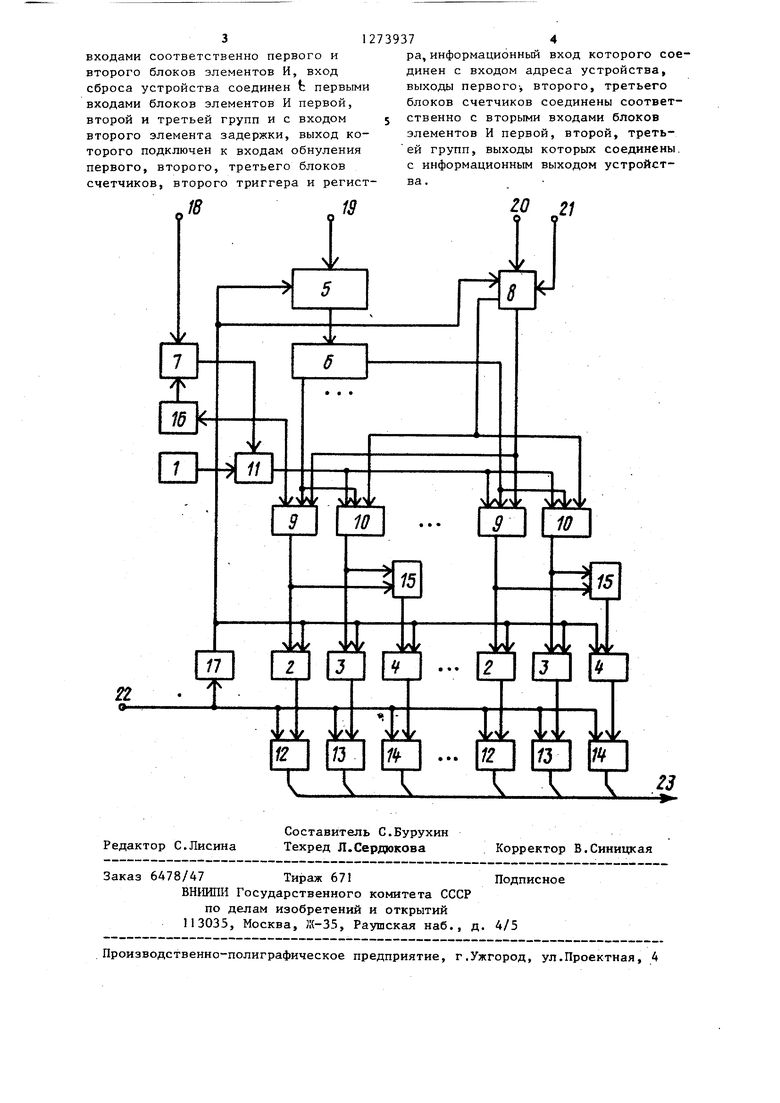

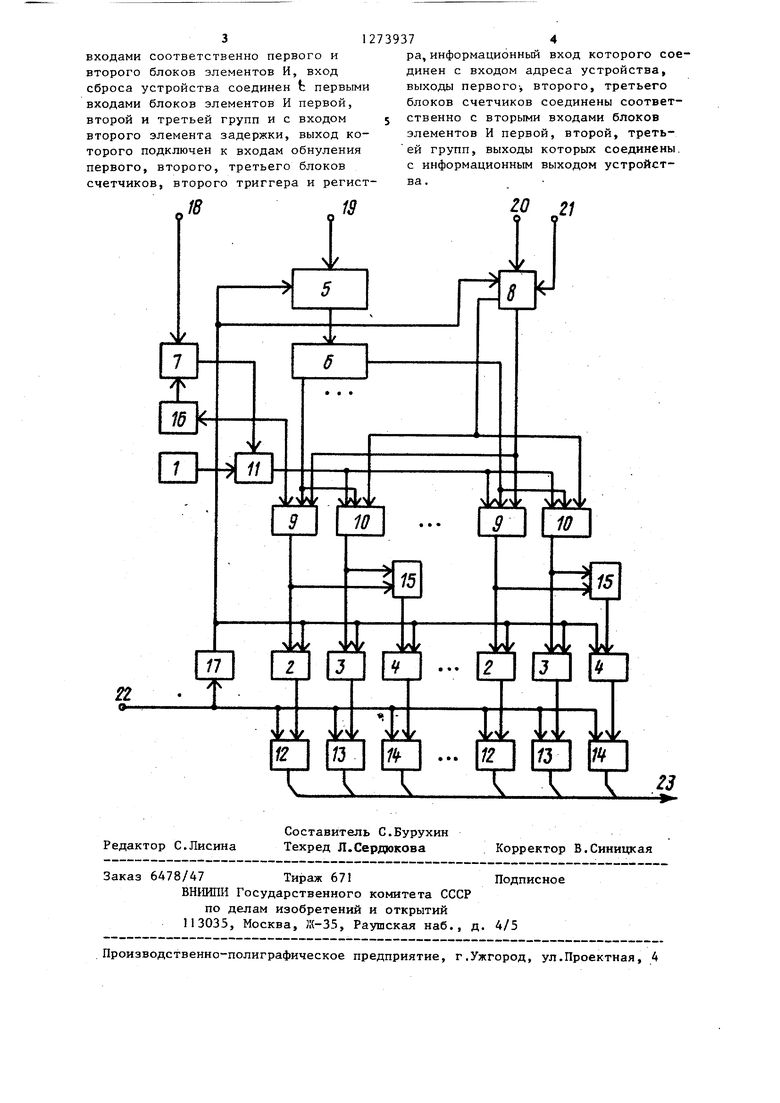

1 Изобретение относится к вычислительной технике, в частности к устройствам для анализа информации, и может быть использовано при проектировании быстродействующих вычислительных комплексов. Цель изобретения - повышение быс родействия ведения анализа частоты использования блоков памяти вычисли тельного комплекса. На чертеже представлена структур ная схема предлагаемого устройства. Устройство содержит генератор 1 импульсов, первый, второй и третий блоки 2, 3, 4 счетчиков, регистр 5, дешифратор 6, первьй и второй триггеры 7 и 8, первый и второй блоки элементов И 9, 10, элемент И 11, первую, вторую и третью группы блоков элементов И 12 - 14, блок 15 элементов ИЛИ, первый и второй элементы 16 и 17 задержки, вход 18 запуска устройства, вход 19 адреса блока памяти устройства, первый, второй входы 20 и 21 идентификации блока памяти устройства, вход 22 сброса устройства, информационный выход 23 устройства. Устройство работает следующим образом. В исходном состоянии регистр 5, счетчики 2 - 4, триггеры 7 и 8 обнулены. По входу 19 в регистр 5 заносится код А адреса блока информации, по входу 18 триггер 7 устанавливается в единичное состояние, триггер 8 устанавливается по левому (по схеме) входу 20 в единичное состояние, если соответствующий блок информации хранится во внешней памя ти, и по правому входу 20 в нулевое состояние, если соответствующий бло информации хранится в оперативной п мяти. Если триггер 8 установлен в единичное состояние, то импульс с гене ратора I проходит через элемент И 1J I Л-й элемент И 9 и увеличивает содержи мое А-х счетчиков 2 и 4 (А-й счетчик 4 определяет общее количество обращеНИИ к А-му блоку информации, счетчи 2 - если А-й блок хранится во внешней памяти, счетчик 3 - соответстве но в оперативной памяти). Если триг гер 8 установлен в нулевое состояние, то импульс с генератора 1 увел чивает содержимое А-х счетчиков 3 и 4. Импульс с выхода элемента И 11 7 . через элемент 16 задержки обнуляет триггер 7. При очередном поступлении кода адреса блока информации в регистр 5 триггер 7 по входу 18 устанавливается в единичное состояние и указанный процесс повторяется. После анализа всех блоков информации по входу 21 поступает сигнал, который разрешает выдачу содержимого счетчи- ков 2 - выход 22 устройства и через элемент 17 задержки обнуляет регистр 5 и триггер 8. На этом работа устройства заканчивается. Формула изобре.тения Устройство для анализа частоты использования блоков информации в вычислительных комплексах, содержащее генератор импульсов, первый, второй и третий блоки счетчиков, дешифратор, первый, второй блоки элементов И, блок элементов ИЛИ, элемент И и регистр, причем выход генератора импульсов подключен к первому входу элемента И, выход регистра соединен свходом дешифратора, выход которого подключен к первым входам первого и второго блоков элементов И, выход первого блока элементов И соединен с первым входом блока элементов ИЛИ, второй вход которого соединен с выходом второго блока элементов И, выходы первого и второго блоков элементов И соединены со счетными входами соответственно первого и второго блоков счетчиков, выход блока элементов ИЛИ подключен к счетному входу третьего блока счетчиков, отличающееся тем, что, с целью повышения быстродействия, в него введены первый, второй триггеры, первая, вторая, третья группы блоков элементов И, первый, второй элементы задержки, причем вход запуска устройства соединен с единичным входом первого триггера, единичный выход и нулевой вход которого соединены соответственно с вторым входом элемента И и с выходом первого элемента задержки, выход элемента И соединен с вторыми входами первого и второго блоков элементов И и с входом первого элемента задержки, первый, второй входы идентификации блока памяти устройства соединены соответственно с единичным и нулевым входами второго триггера, единичный и нулевой выходы которого соединены с третьими

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для анализа частоты использования блоков информации в вычислительных комплексах | 1990 |

|

SU1793442A1 |

| Устройство для перезапуска вычислительного комплекса при обнаружении сбоя | 1988 |

|

SU1541608A1 |

| Устройство для вывода информации | 1983 |

|

SU1200308A1 |

| Устройство для перезапуска вычислительного комплекса при обнаружении сбоя | 1988 |

|

SU1594543A1 |

| Устройство для контроля информации | 1990 |

|

SU1764055A1 |

| Устройство для распределения ресурсов памяти в вычислительном комплексе | 1985 |

|

SU1288705A1 |

| ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ АНАЛОГ - КОД | 1991 |

|

RU2027303C1 |

| Устройство для фиксации сбоев | 1983 |

|

SU1151968A1 |

| Устройство для ввода информации | 1984 |

|

SU1259241A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

Изобретение относится к области вычислительной техники, в частности к устройствам для анализа информации, и может быть использовано при проектировании быстродействующих вычислительных комплексов. Целью изобретения является повышение быстродействия введения анализа частоты использования блоков памяти вычислительного комплекса. Устройство содержит генератор импульсов, с первого по третий блоки счетчиков, регистр, дешифратор, первый, второй триггеры, первый, второй блоки элементов И, элемент И, с первой по третью группы блоков элементов И, блок элементов ИЛИ, первый, второй элементы задержки. Устройство анализирует частоту использования блоков как оперативной, так и внешней пас мяти с целью их оптимального перераспределения для повышения произ(Л водительности вычислительного комплекса. 1 ил.

| Устройство для сопряжения | 1979 |

|

SU881722A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для ввода информации | 1980 |

|

SU885987A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-30—Публикация

1985-06-26—Подача