Cfp .

Фие }

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах диагностики для контроля последовательности цифровых данных при обработке автоматизированным способом.

Цель изобретения-повышение быстродействия устройства.

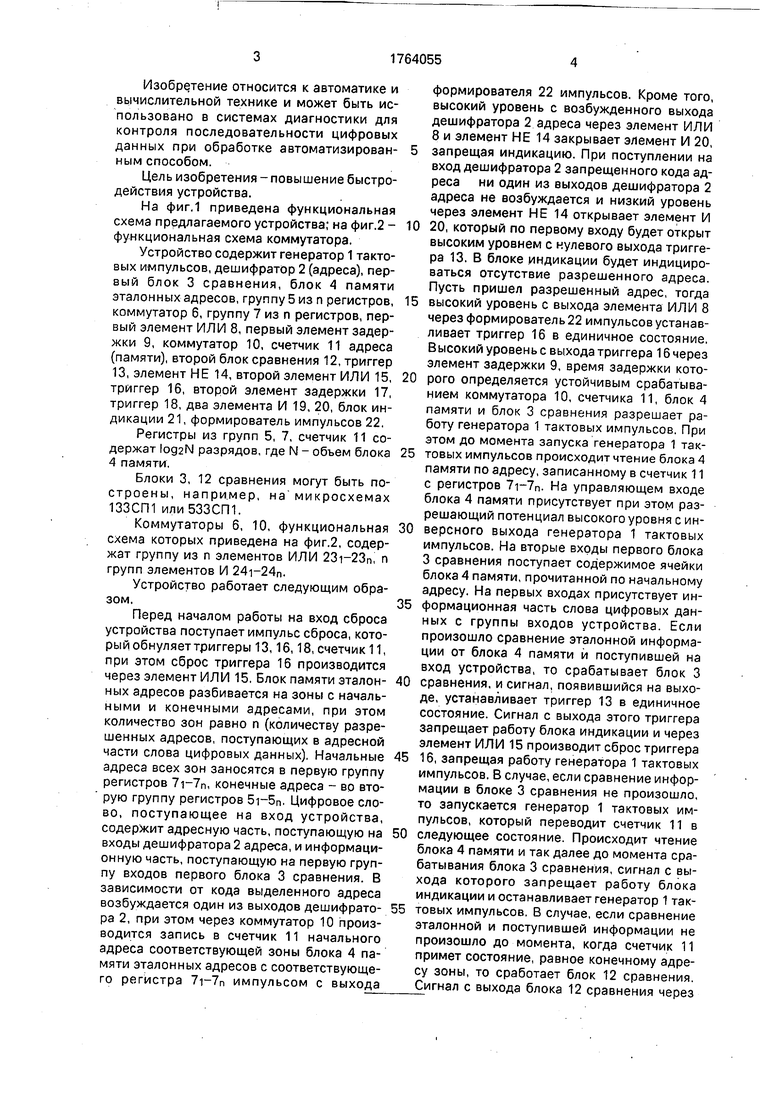

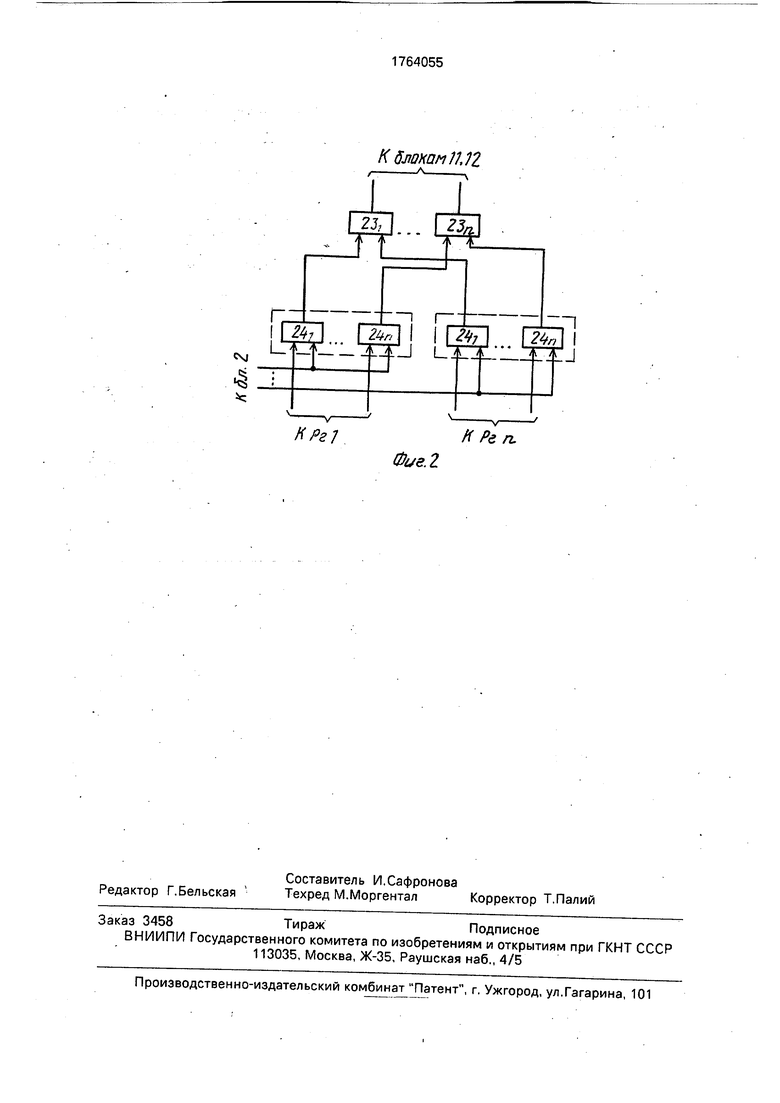

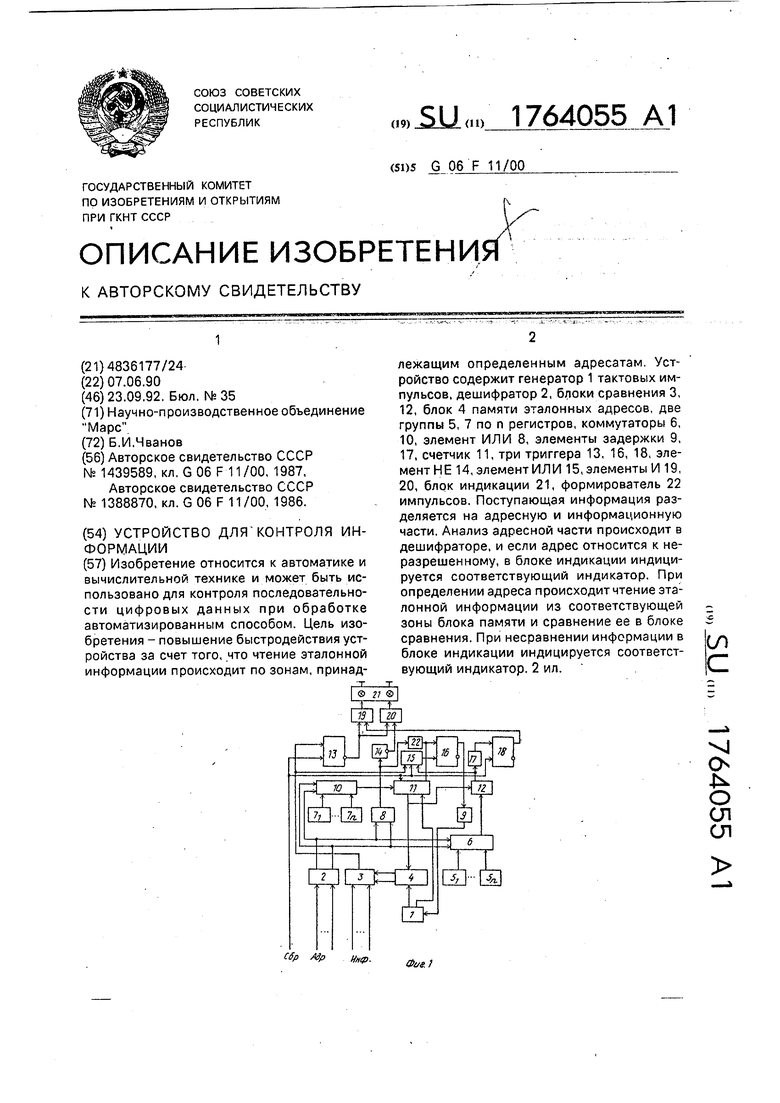

На фиг.1 приведена функциональная схема предлагаемого устройства; на фиг.2 - функциональная схема коммутатора.

Устройство содержит генератор 1 тактовых импульсов, дешифратор 2 (адреса), первый блок 3 сравнения, блок 4 памяти эталонных адресов, группу 5 из п регистров, коммутатор 6, группу 7 из п регистров, первый элемент ИЛИ 8, первый элемент задержки 9, коммутатор 10, счетчик 11 адреса (памяти), второй блок сравнения 12, триггер 13, элемент НЕ 14, второй элемент ИЛИ 15, триггер 16, второй элемент задержки 17, триггер 18, два элемента И 19, 20, блок индикации 21, формирователь импульсов 22.

Регистры из групп 5, 7, счетчик 11 содержат log2N разрядов, где N - объем блока 4 памяти.

Блоки 3, 12 сравнения могут быть построены, например, на микросхемах 133СП1 или533СП1.

Коммутаторы 6, 10, функциональная схема которых приведена на фиг.2, содержат группу из п элементов ИЛИ 23i-23n, n групп элементов И 24i-24n.

Устройство работает следующим образом.

Перед началом работы на вход сброса устройства поступает импульс сброса, который обнуляет триггеры 13,16,18, счетчик 11, при этом сброс триггера 16 производится через элемент ИЛИ 15. Блок памяти эталонных адресов разбивается на зоны с начальными и конечными адресами, при этом количество зон равно п (количеству разрешенных адресов, поступающих в адресной части слова цифровых данных). Начальные адреса всех зон заносятся в первую группу регистров 7i-7n, конечные адреса - во вторую группу регистров 5i-5n. Цифровое слово, поступающее на вход устройства, содержит адресную часть, поступающую на входы дешифратора 2 адреса, и информационную часть, поступающую на первую группу входов первого блока 3 сравнения. В зависимости от кода выделенного адреса возбуждается один из выходов дешифратора 2, при этом через коммутатор 10 производится запись в счетчик 11 начального адреса соответствующей зоны блока 4 памяти эталонных адресов с соответствующего регистра 7i-7n импульсом с выхода

формирователя 22 импульсов. Кроме того, высокий уровень с возбужденного выхода дешифратора 2 адреса через элемент ИЛИ 8 и элемент НЕ 14 закрывает элемент И 20,

запрещая индикацию. При поступлении на вход дешифратора 2 запрещенного кода адреса ни один из выходов дешифратора 2 адреса не возбуждается и низкий уровень через элемент НЕ 14 открывает элемент И

0 20, который по первому входу будет открыт высоким уровнем с нулевого выхода триггера 13. В блоке индикации будет индицироваться отсутствие разрешенного адреса. Пусть пришел разрешенный адрес, тогда

5 высокий уровень с выхода элемента ИЛИ 8 через формирователь 22 импульсов устанавливает триггер 16 в единичное состояние. Высокий уровень с выхода триггера 16 через элемент задержки 9, время задержки кото0 рого определяется устойчивым срабатыванием коммутатора 10, счетчика 11, блок 4 памяти и блок 3 сравнения разрешает работу генератора 1 тактовых импульсов. При этом до момента запуска генератора 1 так5 товых импульсов происходит чтение блока 4 памяти по адресу, записанному в счетчик 11 с регистров . На управляющем входе блока 4 памяти присутствует при этом разрешающий потенциал высокого уровня с ин0 версного выхода генератора 1 тактовых импульсов. На вторые входы первого блока 3 сравнения поступает содержимое ячейки блока 4 памяти, прочитанной по начальному адресу. На первых входах присутствует ин5 формационная часть слова цифровых данных с группы входов устройства. Если произошло сравнение эталонной информации от блока 4 памяти и поступившей на вход устройства, то срабатывает блок 3

0 сравнения, и сигнал, появившийся на выходе, устанавливает триггер 13 в единичное состояние. Сигнал с выхода этого триггера запрещает работу блока индикации и через элемент ИЛИ 15 производит сброс триггера

5 16, запрещая работу генератора 1 тактовых импульсов. В случае, если сравнение информации в блоке 3 сравнения не произошло, то запускается генератор 1 тактовых импульсов, который переводит счетчик 11 в

0 следующее состояние. Происходит чтение блока 4 памяти и так далее до момента срабатывания блока 3 сравнения, сигнал с выхода которого запрещает работу блока индикации и останавливает генератор 1 так5 товых импульсов. В случае, если сравнение эталонной и поступившей информации не произошло до момента, когда счетчик 11 примет состояние, равное конечному адресу зоны, то сработает блок 12 сравнения. Сигнал с выхода блока 12 сравнения через

элемент задержки, время которого определяется срабатыванием блока 4 памяти, блока 3 сравнения, устанавливает триггер 18 в единичное состояние, открывая элемент И 19 по второму входу, на первом входе которого присутствует высокий уровень с выхода триггера 13. В блоке индикации будет индицироваться несравнение информационной части цифрового слов,а с эталоном. При поступлении следующего слова цифровых данных работа происходит аналогично описанной.

Таким образом, если эталонная информация записана в i-ю ячейку блока 4 памяти, то быстродействие повышается на время Т(И), где i принимает значение от 1 до N; Т - время чтения одной ячейки блока 4 памяти прототипа и обработки информации прочитанной ячейки; N - число ячеек блока 4 памяти,

Формула изобретения Устройство для контроля информации, содержащее блок индикации, два элемента И, элемент НЕ, два блока сравнения, блок памяти эталонных адресов, причем группа информационных выходов устройства соединена с первой группой входов первого блока сравнения, выход первого элемента И соединен с первым входом блока индикации, отличающееся тем, что, с целью повышения быстродействия, устройство содержит дешифратор, генератор тактовых импульсов, две группы регистров, первый и второй коммутаторы, счетчик адреса, первый и второй элементы ИЛИ, первый, второй и третий триггеры, первый и второй элементы задержки, формирователь импульсов, причем группа адресных выходов устройства соединена с группой входов дешифратора, выходы которого соединены с управляющими входами первого, второго коммутаторов и входами первого элемента ИЛИ, выход которого соединен с входами

элемента НЕ и формирователя импульсов, выход которого соединен с входом разрешения счетчика адреса и единичным входом первого триггера, выход которого соединен

через первый элемент задержки с входом запуска генератора тактовых импульсов, прямой выход которого соединен со счетным входом счетчика адреса, а инверсный выход - с входом считывания блока памяти

эталонных адресов, группа выходов которого соединена с второй группой входов первого блока сравнения, выход которого соединен с единичным входом второго триггера и первым входом второго элемента

ИЛИ, второй вход которого соединен с нулевыми входами второго и третьего триггеров, входом сброса счетчика адреса и входом сброса устройства, третий вход второго элемента ИЛИ соединен с выходом

второго блока сравнения и через второй элемент задержки - с единичным входом третьего триггера, выход которого соединен с первым входом первого элемента И, вторые входы первого и второго элементов И

соединены с инверсным выходом второго триггера, первый вход второго элемента И соединен с выходом элемента НЕ, выход второго элемента ИЛИ соединен с нулевым входом первого триггера, выходы регистров

первой и второй групп соединены с информационными входами первого и второго коммутаторов соответственно, группа выходов первого коммутатора соединена с группой информационных входов счетчика

адреса, группа информационных выходов которого соединена с первой группой входов второго блока сравнения и группой адресных входов блока памяти эталонных адресов, первая группа входов второго блока сравнения соединена с группой выходов второго коммутатора, выход второго элемента И соединен с вторым входом блока индикации.

К блохам Ш2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля цифровых узлов | 1987 |

|

SU1425682A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Логический анализатор | 1987 |

|

SU1476474A1 |

| УСТРОЙСТВО ТЕСТОВОГО КОНТРОЛЯ | 2014 |

|

RU2565474C1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Устройство для контроля постоянной памяти | 1987 |

|

SU1451781A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство тестового контроля | 1989 |

|

SU1691842A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Устройство для проверки функциональных блоков | 1980 |

|

SU1008745A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля последовательности цифровых данных при обработке автоматизированным способом. Цель изобретения - повышение быстродействия устройства за счет того, что чтение эталонной информации происходит по зонам, принадлежащим определенным адресатам. Устройство содержит генератор 1 тактовых импульсов, дешифратор 2, блоки сравнения 3, 12, блок 4 памяти эталонных адресов, две группы 5, 7 по п регистров, коммутаторы 6, 10, элемент ИЛИ 8, элементы задержки 9, 17, счетчик 11, три триггера 13, 16, 18, элемент НЕ 14, элемент ИЛИ 15, элементы И 19, 20, блок индикации 21, формирователь 22 импульсов. Поступающая информация разделяется на адресную и информационную части. Анализ адресной части происходит в дешифраторе, и если адрес относится к неразрешенному, в блоке индикации индицируется соответствующий индикатор. При определении адреса происходит чтение эталонной информации из соответствующей зоны блока памяти и сравнение ее в блоке сравнения. При несравнении информации в блоке индикации индицируется соответствующий индикатор. 2 ил. СП С

Г.

LT

г

- ,.. I I III I . I II

М/1 | (

S-i

/г/%;

23,

Л

А

У I

К Реп.

Й/е.2

| Устройство для анализа данных | 1986 |

|

SU1439589A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-09-23—Публикация

1990-06-07—Подача