2. Микропроцессор по п. 1, о т личающийся тем, что блок :маскирования кода операции содержит де иифратор и элементы И, первые входы KOTOpHJi соединены со входом данных блока, вторые входы подключены к соответствующим выходам дешифратора, а выходы соединены с выходом блока, при этом вход дешифратора подключен ко входу управления маскированием блока.

-3. Микропроцессор по п. 1, от-: лишающийся тем, что блок микропрограммного управления содержит коммутатор адреса, регистр команд, коммутатор состояний, регистр адреса микрокоманд и формирователи адреса микрокоманд -выходы которых соединены с адресным выходом блока.

а выходы подключены к выходам регистра адреса микрокоманд, входы которого соединены с выходами коммутатора адреса, первый и второй входы коммутатора состояний подключены соответственно ко входу переноса и входу управления режимом блока, а первый и второй выходы коммутатора состояний соединены соответственно с выходом переноса vблока и первым входом коммутатора адреса, второй, третий, четвертый, пятый и шестой входы которого подключены соответственно к выходу регистра команд, входу кода операции, входу разраиения загрузки и входу управления конф утацией блока и выходам регистра адреса микрокоманд, причем вход регистра команд соединен со входом операции блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор | 1982 |

|

SU1037263A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Процессор | 1985 |

|

SU1280378A1 |

| Микропроцессор | 1985 |

|

SU1273939A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968813A1 |

| Процессор с микропрограммным управлением | 1982 |

|

SU1124298A1 |

| Микропрограммное устройство управления | 1980 |

|

SU934473A1 |

1. МИКРОПРОЦЕССОР, содержащий блок.памяти микропрограмм, регругтр микрокоманд,операционный блок и блок микропрограммного управления, адресйый выход которого соединен с адресНы1м входом блока памяти микропрограмм, а вход и выход переноса подключены соответственно к выходу и входу переноса операционiHpro блока, выход управления ком- ; мутацией и выход Шкрокоманд блока памяти микропрограмм соединены соответственно со входом управления коммутацией блока микропрограмлюого управления и входом регистра микрокоманд, первый, второй, третий и четвертый выходы которого подключены соответственно ко входу дешифрации микроопераций и управляющему входу операционного блрка, а тайже входу разрешения загрузки и входу управления режимом блока микропрограммного уп|завлени я, причемвход данных операционного блока соединен со входом данных микропроцессора, отличающийся тем, что с целью увеличения быстродействия, он содержит блок маскирования кода 0 операции, вход данных которого подключен ко входу данных микропроцесС сора, выход соединен со входом кода операц|(и блока микропрограммного управления, а вход управления маскированием подключен к пятому выходу регистра микрокоманд. INO to C3f5 о:

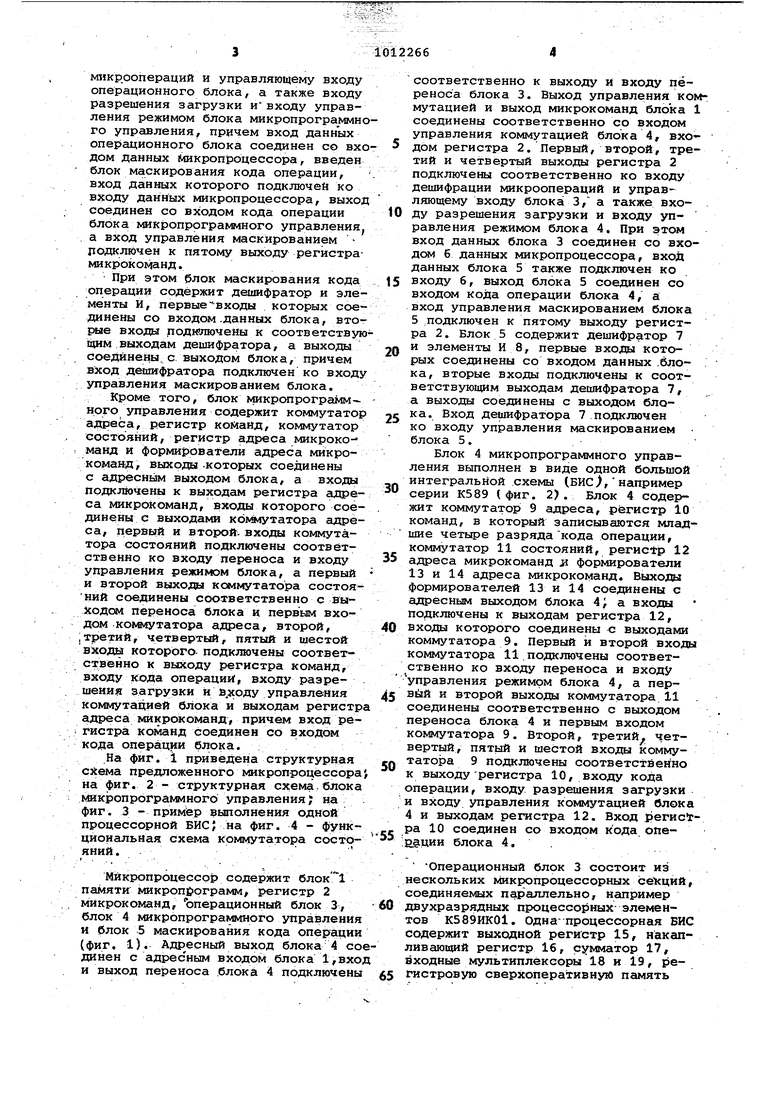

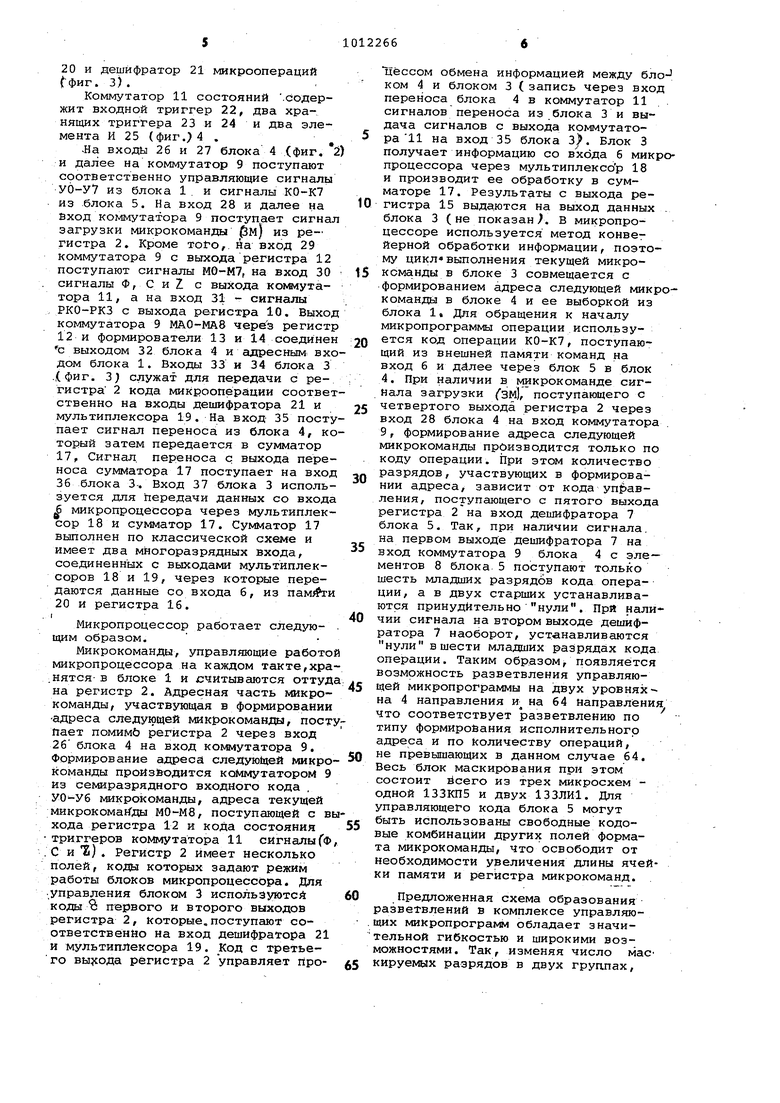

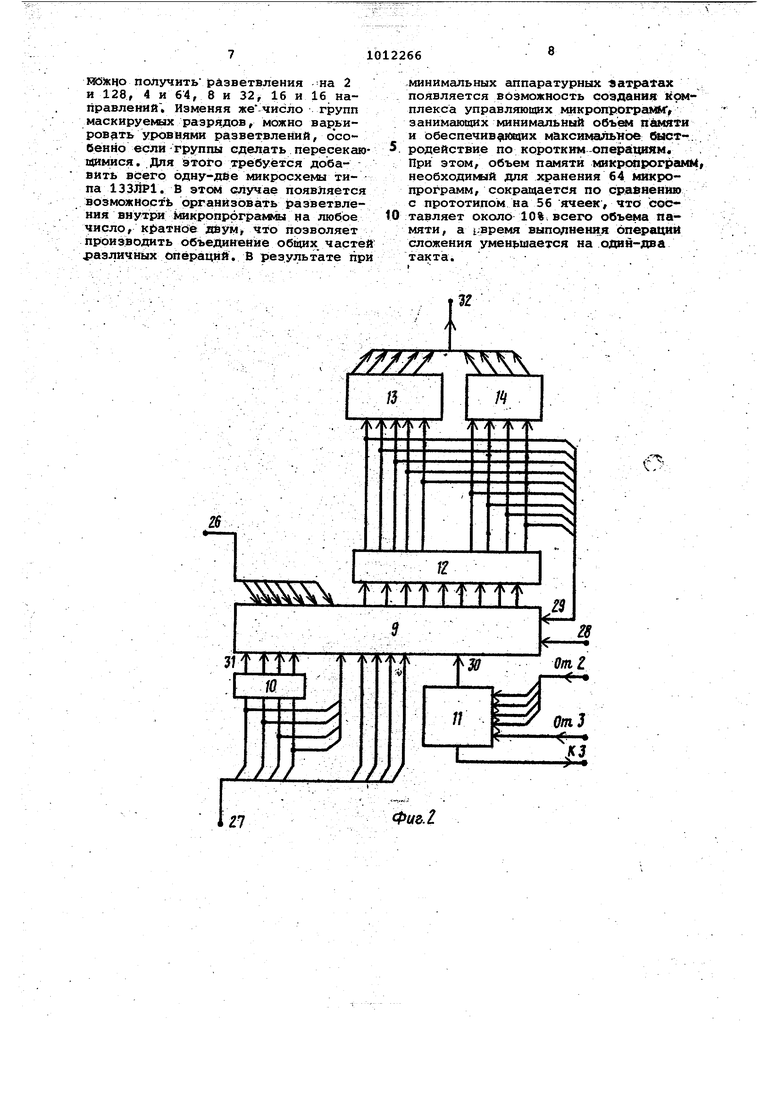

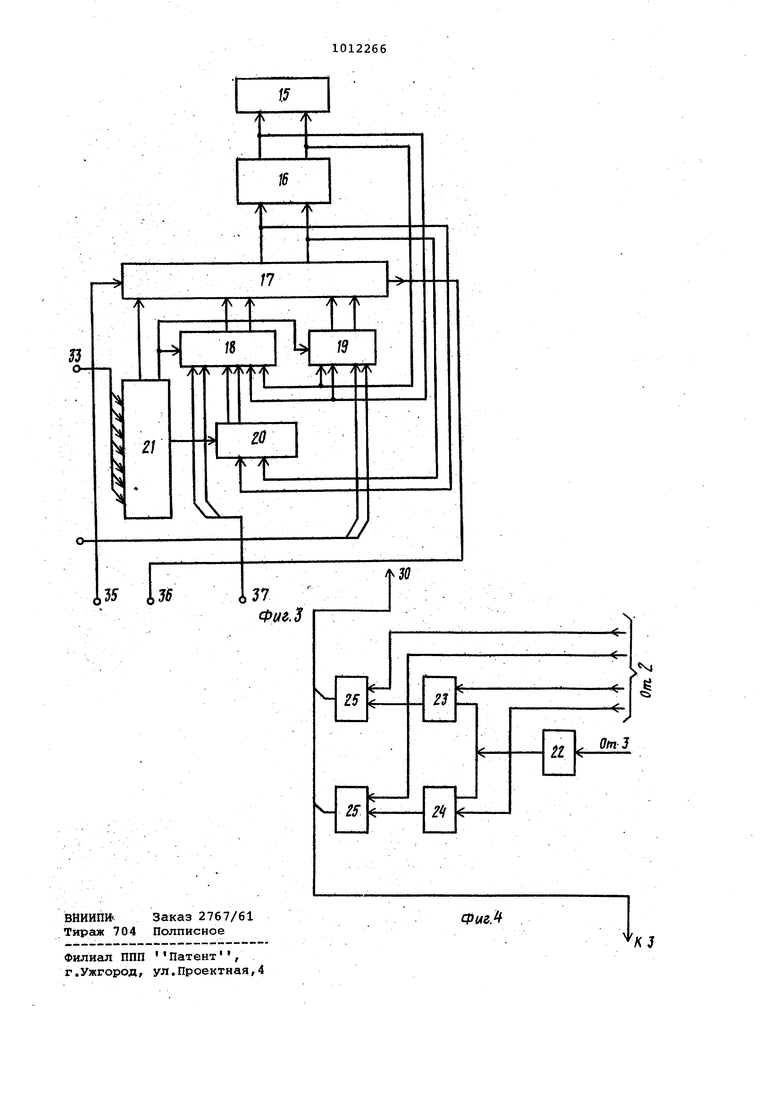

Изобретение относится к вычислительной технике и может быть исполь зовано в специализированных микро-Э для летательных аппаратов. Известны микропроцессоры, постро енные на одной или нескольких больших интегральных схемах (БИС), использование которых обеспечивает ма лые габариты и вес аппаратуры ij и С2. Основньоми недостатками этих микр процессоров является низкое быстрсэдействие и ограниченные вычислител ные возможности, что затрудняет их применение в системах обработки дан ных для летательных аппаратов. Наиболее близким по технической сущности к изобрет-ению является мик ропроцессор, который состоит из бло ка памяти микропрограмм, блока цент рального процессора, блока микропрограммного управления и регистра микрокоманд. Этот микропроцессор обладает достаточно высокой скорост обработки информации и гибкостью применения за счет использования в нем микропрограммного управления С ЗОднако при реализации в нем универсальной системы команд, что характерно для бортовых систем обработки данных, из-за, ограниченных возможностей системы адресации микр команд происходит усложнение управляющей микропрограммы и соответственно снижается быстродействие. Так например, для начального обращения к микропрограммам каждой команды используется непосредственная адресация по коду операции, при этом число разветвлений микропрограмм может быть равно только 4, 16 и 256. Отсутствие промежуточных .значений числа разветвлений приводит к тому, что приходится повторять в некоторых микропрограммах общие части или же вводить, дополнительные холостые микрокоманды, осуществляющие переход между 6т:дельными частями микропрограмм. В первом случае увеличивается необходимый объем памяти микропрограмм, или же уменьшается количество реализуемых (при ограничениях на объем памяти) микрокоманд, во втором случае понижается быстродействие по коротким операциям. Цель изобретения - уменьшение объема управляющей памяти микропрограмм и увеличение быстродействия. С этой целью в микропроцессор, содержащий блок памяти микропрограмм, регистр микрокоманд, операционный блоК и блок микропрограммного управления, адресный выход которого соединен с адресным входом блока памяти микропрограмм, а вход и выход переноса подключены соответственно к выходу и входу переноса операционного блока, выход управления коммутацией и. выход микрокоманд блока памяти микропрограмм соединены соответственно со входом управления коммутацией блока микропрограммного управления и входом регистра микрокоманд, первый, второй,;третий и четвертый выходы которого подключены соответственно ко входу дешифрации микроопераций и управляющему входу операционного блока, а также входу разрешения загрузки ивходу управления режимом блока микропрограммно го управления причем вход данных операционного блока соединен со вхо дом данных Микропроцессора, введен блок маскирования кода операции, вход данных которого подключей ко входу данных микропроцессора, выход соединен со входом кода операции блока микропрограммного управления, а вход управления маскированием подключен к пятому выходу регистрамикрокоманд. При этом блок маскирования кода операции содержит дешифратор и элементы И, первые -входы которых соединены со входе .данных блока, вторые входы подкэтючейы к соответствую щим, выходам дешифратора, а выходы соединены,С- выходом блока, причем вход дешифратора подключен ко входу управления маскированием блока. Кроме того, блок микротхрограммного управления содержит коммутатор адреса., регистр команд, коммутатор состояний, регистр адреса микрокоманд и формирователи адреса микрокоманд, выходы -которых соединены с адресным выходом блока, а входа подключены к выходам регистра адреса микрокоманд, входы которого соединены с выходами к6д мутатора адреса, первый и второй, входы коммутатора состояний подключены соответственно ко входу переноса и входу управления режимом блока, а первый и второй выходы коммутатора состояний соединены соответственно с выХодслл переноса блока и первым входом ко1имутатора адреса, второй, .третий, четвертый, пятый и шестой входы которого подключены соответственно к выходу регистра команд, входу кода операции, входу разрешения загрузки и й.ходу управления коммутацией блока и выходам регистр адреса микрокоманд, причем вход регистра команд соединен со входом кода операции блока. На фиг. i приведена структурная предложенного микропроцессора на фиг. 2 - структурная схема,блока мик|ропрограммного управления; на фиг. 3 - пример выполнения одной процессорной БИС; на фиг. 4 - функциоиальйая схема коммутатора состояний. . Микропроцессор содержит блок 1 памяти микропрограмм, регистр 2 микрокоманд, операционный блок 3, блок 4 микропрограммного управления и блок 5 маскирования кода операции (фиг. 1). Адресный выход блока 4 со динен с адресным входом блока 1,вхо и выход переноса блока 4 подключены соответственно к выходу и входу переноса блока 3. Выход управления коммутацией и выход микрокоманд блока 1 соединены соответственно со входе управления коммутацией блока 4, входом регистра 2. Первый, второй, третий и четвертый выходы регистра 2 подключены соответственно ко входу дешифрации микроопераций и управляющему входу блока 3/ а также вхо- . ду разрешения загрузки и входу управления режимом блока 4. При этом вход данных блока 3 соединен со входом 6 данных микропроцессора, вход данных блока 5 также подключен ко входу 6, выход блока 5 соединен со входом кода операции блока 4, а вход управления маскированием блока 5 подключен к пятому выходу регистра 2. Блок 5 содержит дешифратор 7 и элементы И 8, первые входы которых соединены со входом данных .блока, вторые входы подключены к соответствующим выходам дешифратора 7, а выходы соединены с выходом блока. Вход дешифратора 7 подключен ко входу управления маскированием блока 5. Блок 4 микропрограммного управления выполнен в виде одной большой интегральной .схемы (БИС,например серии К589 (фиг. 2). Блок 4 содержит коммутатор 9 адреса, регистр 10 команд, в который записываются младшие четыре разрядакода операции, коммутатор 11 состояний, perHCtp 12 адреса микрокоманд л формирователи 13 и 14 адреса микрокоманд. Выходы формирователей 13 и 14 соединены с адресным выходом блока 4; а входы подключены к выходам регистра 12, входа которого соединены с выходами коммутатора 9. Первый и второй входы коммутатора 11 подключены соответственно ко входу переноса и входу Vпpaвлeния режимом блока 4, а первйй и второй выходы коммутатора 11 соединены соответственно с выходом переноса блока 4 и первым входом коммутатора 9. Второй, третий, четвертый, пятый и шестой входы коммутатора 9 подключены соответственно к выходурегистра 10, входу кода операции, входу разрешения загрузки и входу управления коммутацией блока 4 и выходам регистра 12. Вход регистра 10 соединен со входом кода опе2§ции блока 4. Операционный блок 3 состоит из нескольких микропроцессорных секций, соединяемых параллельно, например двухразрядных процессорных элементов К589ИК01. Одна- процессорная БИС содержит выходной регистр 15, накапливающий регистр 16, сумматор 17, входные мультиплексоры 18 и 19, регистровую сверхоперативную память

20 и дешифратор 21 микроопераций ( фиг. 3) .

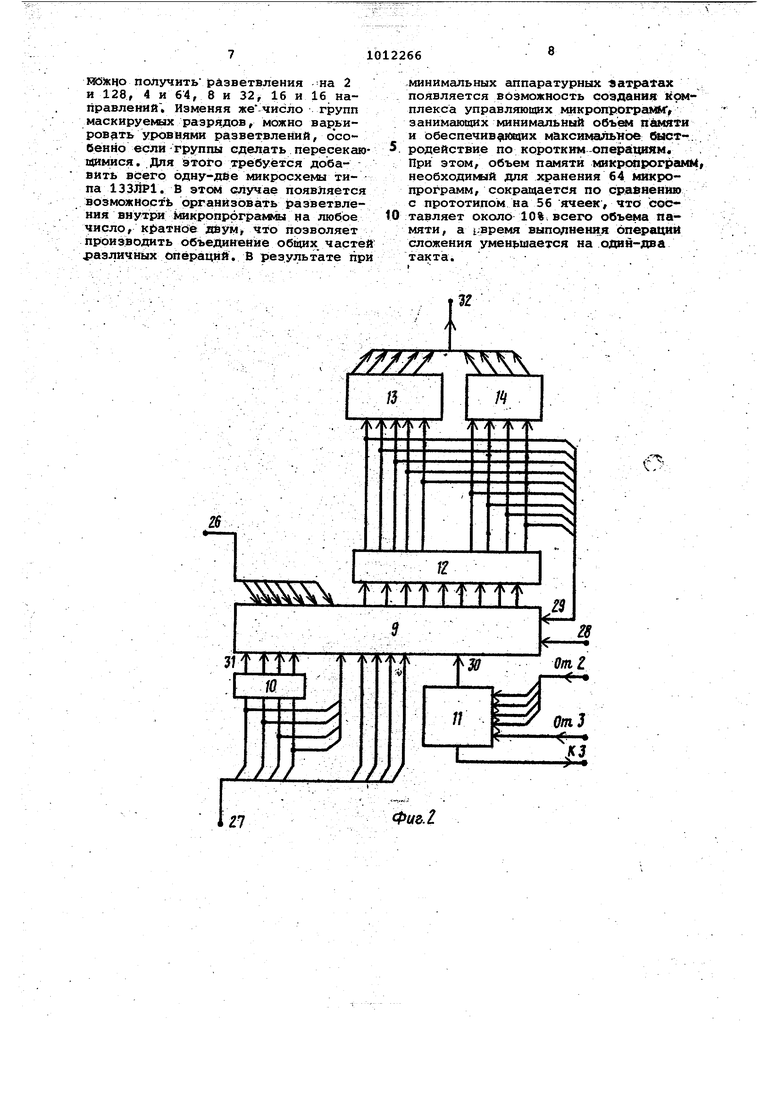

Коммутатор 11 состояний .содержит входной триггер 22, два хранящих триггера 23 и 24 и два элемента И 25 (фиг.) 4 ,

-На входы 26 и 27 блока 4 (фиг, 2) и далее на коммутатор 9 поступают соответственно управляющие сигналы У6-У7 из блока 1. и сигналы КО-К7 из блока 5. На вход 28 и далее на Вход коммутатора 9 поступает сигнал загрузки микрокоманды (5м) из регистра 2. Кроме ToJfo,. На вход 29 коммутатора 9 с выхода регистра 12 поступают сигналы МО-М7, на вход 30 сигналы Ф, С и Z с выхода коммутатора 11, а на вход 31 - сигналы РКО-РКЗ с выхода регистра 10. Выход коммутатора 9 МАО-МА8 через регистр 12 и формирователи 13 и 14 соединен с выходом 32 блока 4 и адресным, входом блока 1. Входы 33 и 34 блока 3 (фиг. 3) служат для передачи с регистра 2 кода микрооперации соответственно на входы дешифратора 21 и мультиплексора 19. На вход 35 поступает сигнал переноса из блока 4, который затем передается в сумматор 17, Сигнал, переноса с выхода переноса сумматора 17 поступает на вход 36 блока 3-. Вход 37 блока 3 используется для передачи данных со входа микропроцессора через мультиплексор 18 и сумматор 17. Сумматор 17 выполнен по классической схеме и имеет два многоразрядных входа, соединенных с выходами мультиплексоров 18 и 19, через которые передаются данные со входа б, из

20 и регистра 16.

Микропроцессор работает следую- . щим образом.

Микрокоманды, управляющие работой микропроцессора на каждом такте,хранятся- в блоке 1 и считываются оттуда: на регистр 2. Адресная часть микрокоманды/ участвующая в формировании адреса следующей микрокоманды, постур йает помимЬ регистра 2 через вход 26 блока 4 на вход коммутатора 9. Формирование адреса следующей микрокоманды проИзЬодится коммутатором 9 Из семиразрядного входного кода , УО-Уб микрокоманды, адреса текущей микрокомай ды МО-М8, поступающей с выхода регистра 12 и коДа состояния триггеров коммутатора 11 сигналы(Ф, С и Z) . Регистр 2 имеет несколько полей, коды которых задают режим работы блоков микропроцессора. Для управления блоком 3 используютсй коды первого и второго выходов регистра 2, которые.поступают соответственно на вход дешифратора 21 и мультиплексора 19. Код с третьего регистра 2 управляет rtpo цессом обмена информацией между блоком 4 и блоком 3 (запись через вход переноса блока 4 в коммутатор 11 . сигналов переноса из блока 3 и выдача сигналов с выхода коммутатора 11 на вход 35 блока З). Блок 3 получает информацию со входа 6 микрпроцессора через мультиплексор 18 и производит ее обработку в сумматоре 17. Результаты с выхода регистра 15 выдаются на выход данных блока 3 (не показан), В микропроцессоре используется метод конвейерной обработки информации, поэтому цикл выполнения текущей микрокоманды в блоке 3 совмещается с формированием адреса следующей микркоманды в блоке 4 и ее выборкой из блока 1. Для обращения к началу микропрограммы операции используется код операции КО-К7, поступающий из внешней памяти команд на вход 6 и далее через блок 5 в блок 4. При наличии в микрокоманде сигнала загрузки ЗМ), поступающего с четвертого выхода регистра 2 через вход 28 блока 4 на вход коммутатора 9, формирование адреса следующей микрокоманды производится только по коду операции. При этом количество разрядов, участвующих в формировании адреса, зависит от кода управления, поступающего с пятого выхода регистра 2 на вход дешифратора 7 блока 5. Так, при наличии сигнала. на первом выходе дешифратора 7 на вход коммутатора 9 блока 4 с элементов 8 блока 5 поступают только шесть младших разрядов кода операции, а в двух старших устанавливаются принудительно нули. При наличии сигнала на втором выходе дешифратора 7 наоборот, устанавливаются нули в шести младших разрядах кода операции. Таким образом, появляется возможность разветвления управляющей микропрограммы на двух уровняхна 4 направления и на 64 направлени что соответствует разветвлению по типу формирования исполнительного адреса и по Количеству операций, не превышающих в данном случае 64. Весь блок маскирования при этом состоит йсего из трех микросхем одной 133КП5 и двух 133ЛИ1. Для управляющего кода блока 5 могут быть использованы свободные кодовые комбинации других полей формата микрокоманды, что освободит от необходимости увеличения длины ячейки памяти и регистра микрокоманд.

Предложенная схема образования разветвлений в комплексе управляющих микропрограмм обладает значительной гибкостью и широкими возможностями. Так, изменяя число маС кируемых разрядов в двух группах.

RKJiKHo получитьразветвления -на 2 и 128, 4 и 64, 8 и 32, 16 и 16 направлений« Изменяя же число riaynn маскируеьвлх разрядов, можно вар ьировать уровнями разветвлений, с собенно если -группы сделать пересекаюгцимися. Для этого требуется добавить всего одну-дбе микросхемы типа 13 ЗЛР1. В эт(ш случае появляется возможность организовать разветвления внутри toiKponporpaMsflj на любое число/ Kf aTHde двум, что позволяет П1 оизводить объединение общих частей различных операций. В результате при

минимальных аппаратурных затратах появляется возможность создания комплекса управляющих мнкропрргралЛГ занимающих минимальный объ памяти и обеспечив иощих максимальн ое быст- . родействие по коротким-операциям. При этом, объем памяти микрся1рогрг 1 4, необходимый для хранения 64 микроnporpciMM, сокращается по сравнению с прототипом на 56 ячеек, что составляет около 10%.всего объема памяти, а 1;время выполненная операций сложения уменьшается на один-два такта.

л

Щ

/ г/ /V/VVk /

27

фцъ.1

/ЛЛЧ

/

Id

W

,/ -1

/fvА

2tf

Z1

35 AJ5

57 0i/eJ

J(

/

Г|

ОтЗ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США 4010449, КЛ.6 Об F 15/00, опублик | |||

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Микропроцессоры и микро-ЭВМ | |||

| М., Энергия / 1979, с | |||

| Способ приготовления пищевого продукта сливкообразной консистенции | 1917 |

|

SU69A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Микропроцессоры в цифровых системах | |||

| М., Энергия, 1979, с | |||

| Шкив для канатной передачи | 1920 |

|

SU109A1 |

Авторы

Даты

1983-04-15—Публикация

1981-09-28—Подача