Изобретение относится к вычислительной технике, а именно к запоминающим устройствам со средствами самоконтроля, и может быть использовано для обнаружения однонаправленных ошибок в двух модулях памяти и исправления однонаправленных ошибок в одном модуле памяти.

Цель изобретения - повышение достоверности контроля и увеличение информационной емкости устройства.

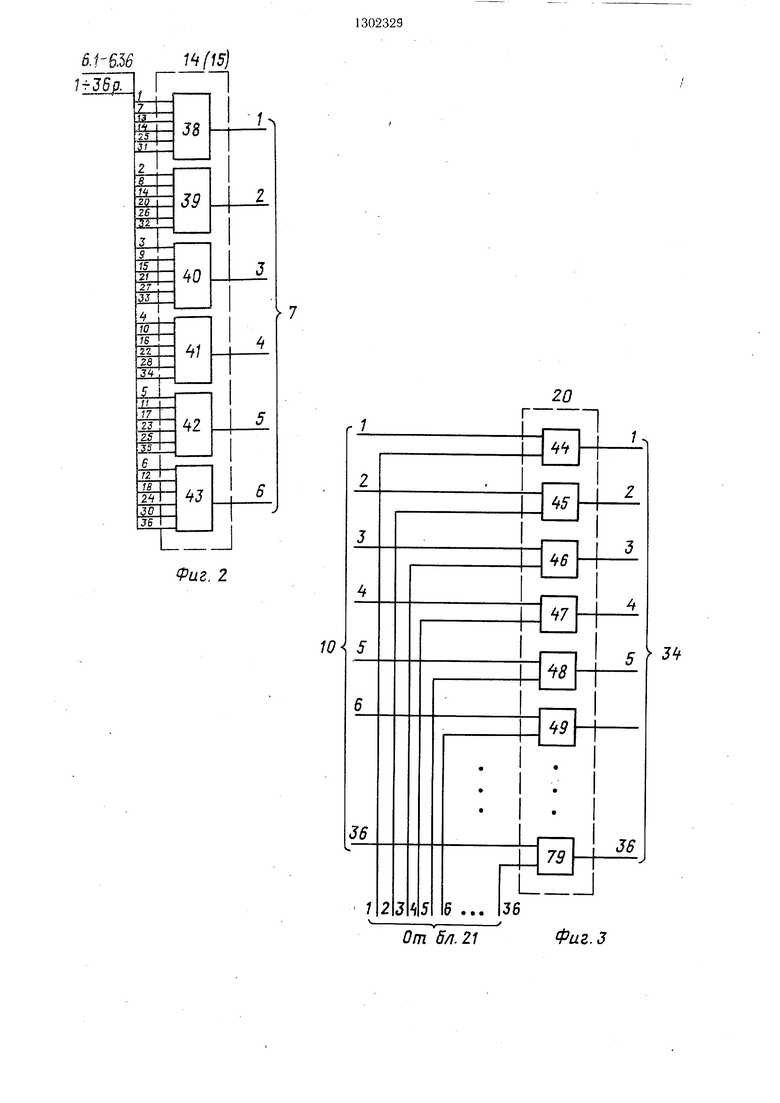

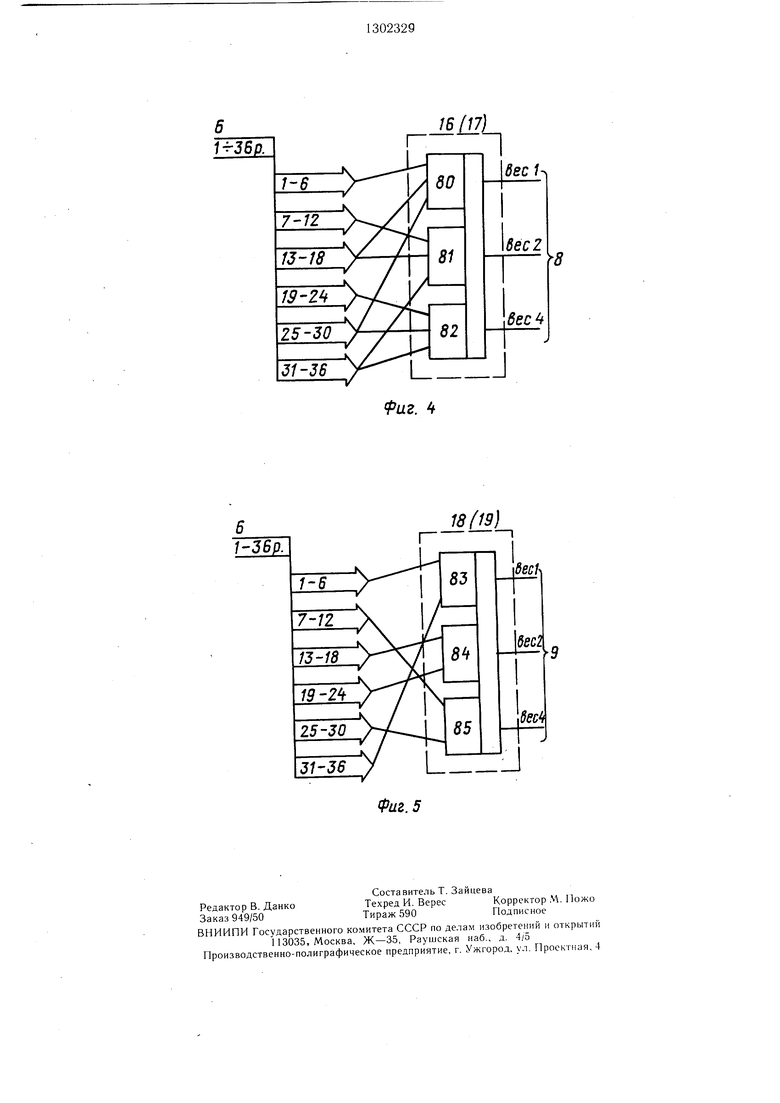

На фиг.1 представлена функциональная схема устройства; на фиг.2-5 - структурные схемы наиболее предпочтительных вариантов выполнения соответственно группы формирователей четности, блока коррекции ошибок, первой (второй) группы и третьей (четвертой) группы блоков свертки по нечетному модулю.

Устройство содержит (фиг. 1) блок 1 модульной памяти, состоящий из модулей 2 памяти, имеющий входы 3 адреса, вход 4 записи-считывания, вход 5 обращения, информационные входы 6, группы с первой по третью контрольных входов 7-9, информационные выходы 10 и группы с первой по третью контрольных выходов 11 -13, первую и вторую группы 14 и 15 формирователей четности, группы 16-19 с первой по четвертую блоков свертки по нечетному модулю, блок 20 коррекции ошибок, мультиплексор 21, блок 22 поразрядного сравнения, первый блок 23 сравнения, первый и второй блоки 24 и 25 сравнения кодов, второй блок 26 сравнения, первый и второй блоки 27 и 28 локализаии ошибок, элементы НЕ 29, коммутатор 30, первый 31 и второй 32 элементы ИЛИ и элемент ИЛИ-И 33.

На фиг.1 обозначены информационные выходы 34 и контрольные выходы 35-37 устройства.

На фиг.2 показаны формирователи 38- 43 четности и принцип их подключения к входам 6.1-6.36 1 модульной памяти.

Блок 20 коррекции ошибок содержит (фиг.З) формирователи 44-79 четности.

На фиг.4 показан принцип разбиения информационных разрядов на модули и подключения информационных входов 6.1-6.36 к блокам 80-82 свертки по нечетному модулю первой группы 16.

Аналогично подключаются выходы 10.1 - 10.36 к второй группе 17 блоков свертки по нечетному модулю. На фиг.5 показан принцип подключения входов 6.1-6.36 к блокам 83-85 свертки по нечетному модулю третьей группы 18. Аналогично подключаются выходы 10.1 -10.36 к входам второй группы 19 блоков свертки по нечетному модулю. Блоки 27 и 28 локализации ошибок могут быть выполнены, например, в виде ПЗУ с адресной выборкой.

Блок 1 модульной памяти может содержать, например, шесть шестиразрядных информационных модулей 2 памяти и три контрольных модуля 2 памяти, имеющие раз

5

0

5

0

0

5

0

5

рядность соответственно шесть, три и три бита.

Устройство работает следующим образом.

В режиме записи на входы 3 поступают коды адресов ячеек памяти, в которые необходимо записать информацию, поступающую по входам 6. На вход 4 подают сигнал управления записью, например лог.О, а на вход 5 обращения - сигнал выборки, например лог.О, длительность которого превосходит задержки в блоке 1 и блоках 14, 16 и 18, в которых происходит выработка трех групп контрольных разрядов, записывающихся по входам 7-9 в блок 1 в режиме записи в каждую ячейку.

В режиме считывания на входы 3 поступают коды адресов ячеек, информацию из которых необходимо считать. На входе 4 устанавливают код операции считывания, например лог.1. На вход 5 подают сигнал обращения, например лог.О, длительность которого должна быть больше времени выборки из блока 1 и задержек в блоках декодирования. Считанная информация по выходам 10 поступает через блок 20 на выход 34 устройства и на входы блоков 15, 17 и 19, в которых образуются три группы контрольных разрядов так же, как и при записи. В блоках 22, 23 и 26 происходят сравнения полученных контрольных разрядов с теми, которые хранились в блоке 1 и считываются по выходам 11 -13.

В зависимости от результатов сравнения возможны следующие варианты продолжения работы устройства:

На выходах всех блоков 22, 23 и 26 нули, что означает, что ошибок нет и информацию с выходов 34 можно использовать. На выходе 36 элемента ИЛИ 32 будет присутствовать лог.О.

На выходе одного или нескольких блоков 22, 23 и 26 имеются единичные сигналы-индикаторы наличия ощибок. В этом случае на выходе 36 будет единичный сигнал, который свидетельствует о том, что считанную информацию использовать нельзя, пока не будет выяснен характер ощибок.

Если имеются единичные сигналы на выходе всех блоков 22, 23 и 26, это означает отказ в информационных разрядах, и через некоторое время на выходе блоков 27 и 28 будет выработан номер отказавшего модуля 2 памяти. После этого на выходе элемента 37 появится единичный сигнал, что означает, что произошел отказ в информационных разрядах блока 1. Если через время, необходимое для срабатывания блоков 27 и 28, а также элемента ИЛИ-И 33, единичного сигнала на выходе 37 нет, то это означает, что произошел отказ в контрольных разрядах блока 1 в одной или двух группах одновременно. В этом случае информация с выходов 34 можт быть использована.

В том случае, когда первоначально на выходе 36, а затем и на выходе 37 появляется единичный сигнал (признак отказа в информационных разрядах) возможны две ситуации.

Если произошел отказ в одном модуле 2 памяти - в этом случае в блоках 24 и 25 произойдет сравнения кодов, записанных в блоках 27 и 28, и через элемент ИЛИ 31 будет послан сигнал на выход 35, который означает, что имеет место исправляемая ошибка. Номера отказавших разрядов блока 1 поступают на мультиплексор 21 из блока 22, а номер отказавшего модуля 2 памяти через коммутатор 30 поступает на другие входы мультиплексора 21, вследствие чего в нужных разрядах произойдет в блоке 20 инвертирование считанной информации, и ее можно использовать.

Если произошли отказы в двух модулях 2 памяти, тогда в блоках 24 и 25 не произойдет совпадения и на входе 35 не появится стробирующий сигна.т, показывающий одновременно, что информацию использовать нельзя.

Формула изобретения

Запоминающее устройство с самоконтролем, содержащее группы формирователей четности, группы блоков свертки по нечетному модулю, блок коррекции ойлибок, мультиплексор, блок поразрядного сравнения, блоки сравнения, первый блок локализации ошибок и блок модульной памяти, информационные входы которого соединены с входами формирователей четности первой группы и блоков свертки по нечетному модулю первой группы, выходы которых подключены соответственно к контрольным входам первой и второй групп блока модульной памяти, информационные выходы которого соединень с одними из входов блока коррекции ошибок, входами блоков свертки по нечетному модулю второй группы и входами формирователей четности второй группы, выходы которых подключены к одним из входов блока поразрядного сравнения, другие входы которого соединены с контрольными выходами первой группы блока модульной памяти, контрольные выходы второй группы которого подключены к одним их входов первого блока сравнения, другие входы которого соединены с выходами блоков свертки по нечетному модулю, выходы первого блока поразрядного сравнения подключены к одним из входов мультиплексора и первого блока локализации ошибок, другие входы которого соединены с выходами первого бло0

ка сравнения, выходы мультиплексора подключены к другим входам блока коррекции ошибок, выходы которого являются информационными входами устройства, информа- ционными и адресными входами которого являются информационные и адресные входы блока модульной памяти, вход «записи-считывания и вход «обращения которого являются входом «записи-считывания и входом «обращения устройства, отличающееся тем, что, с целью повышения достоверности контроля и увеличения информационной емкости устройства, в него введены третья и четвертая группы блоков свертки по нечетному модулю, блоки сравнения кодов, второй блок сравнения, второй блок локализации ошибок, коммутатор, элемент ИЛИ-И, элементы НЕ и элементы ИЛИ, причем входы и выходы блоков свертки по нечетному модулю третьей группы подключены соответственно к информацион0 ным входам и к контрольным входам третьей группы блока модульной памяти, информационные выходы которого соединены с входами блоков свертки по нечетному модулю четвертой груи- nbiv выходы которого подключены к одним из

5 входов второго блока сравнения, другие входы которого соединены с контрольными выходами третьей группы блока модульной памяти, а выходы - с одними из входов второго блока локализации ошибок, выходы первой группы которого подключены к одним из входов первого блока сравнения кодов, а выходы второй группы второго блока локализации ошибок - к одним из входов второго блока сравнения кодов, выходы блоков сравнения кодов соединены с входами первого элемента ИЛИ, выход которого подключен к первому управляющему входу коммутатора, одни из информационных входов которого соединены с выходами элементов НЕ, второй управляющий вход коммутатора подключен к выходу второго

блока локализации ошибок, другие входы которого соединены с выходами блока поразрядного сравнения, выходы первого блока локализации ошибок соединены с другими входами третьего и четвертого блоков сравнения, входами элементов НЕ и другими

5 информационными входами коммутатора, выходы которого подключены к другим входам мультиплексора, входы элемента ИЛИ-И соединены с выходами блоков локализации ошибок, входы второго элемента ИЛИ подключены к выходам блока поразрядного

сравнения первого и второго блоков сравнения, выходы элементов ИЛИ и элемента ИЛИ-И являются контрольными выходами устройства.

0

6.1-6.6

)

От 5л. 21

Фиг.З

8

1 36p.

fuz.

18fl9)

1-6

7-12

13-18

19-2

25-30

31-36

Фиг. 5

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с самоконтролем (его варианты) | 1982 |

|

SU1117714A1 |

| Модульное запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1320848A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

| САМОКОРРЕКТИРУЮЩЕЕСЯ УСТРОЙСТВО | 1999 |

|

RU2210805C2 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1096697A1 |

| Запоминающее устройство с коррекцией ошибок | 1982 |

|

SU1161990A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Запоминающее устройство с исправлением модульных ошибок | 1985 |

|

SU1302327A1 |

| Запоминающее устройство с обнаружением многократных ошибок | 1982 |

|

SU1156143A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам. Целью изобретения является повышение достоверности контроля и увеличение информационной емкости устройства. Устройство содержит блок 1 модульной памяти, содержащий, например, щесть инфор15- 1 Р .ж мационных шестиразрядных модулей 2 памяти с входами 6 и выходами 10 и три контрольных модуля 2 памяти с входами 7-9 и выходами 11 -13 и число разрядов, равным шести, трем и трем битам соответственно, группы 14 и 15 формирователей четности, группы 16-19 блоков свертки по нечетному модулю, блок 20 коррекции ошибок, мультиплексор 21, блоки 22, 23, 26 поразрядного сравнения, блоки 24, 25 сравнения кодов, блоки 27, 28 локализации ошибок, элементы НЕ 29, коммутатор 30, элементы ИЛИ 31, 32 и элемент ИЛИ-И 33. Устройство обеспечивает обнаружение однонаправленных ошибок в двух модулях 2 памяти и исправление однонаправленных ошибок в одном модуле 2 памяти при увеличении разрядности слова в два раза. Блоки 27 и 28 вырабатывают коды номеров отказавших модулей 2 памяти. 5 ил. с S (Л со о ьо СлЭ ю со

| Запоминающее устройство с самоконтролем (его варианты) | 1982 |

|

SU1117714A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU875456A1 |

| Солесос | 1922 |

|

SU29A1 |

Авторы

Даты

1987-04-07—Публикация

1985-12-30—Подача