Изобретение относится к вычислительной технике и может быть использовано при создании вычислительных систем с высокой стененью надежности.

Цель изобретения - расширение области применения устройства за счет доступа к операндам различной разрядности.

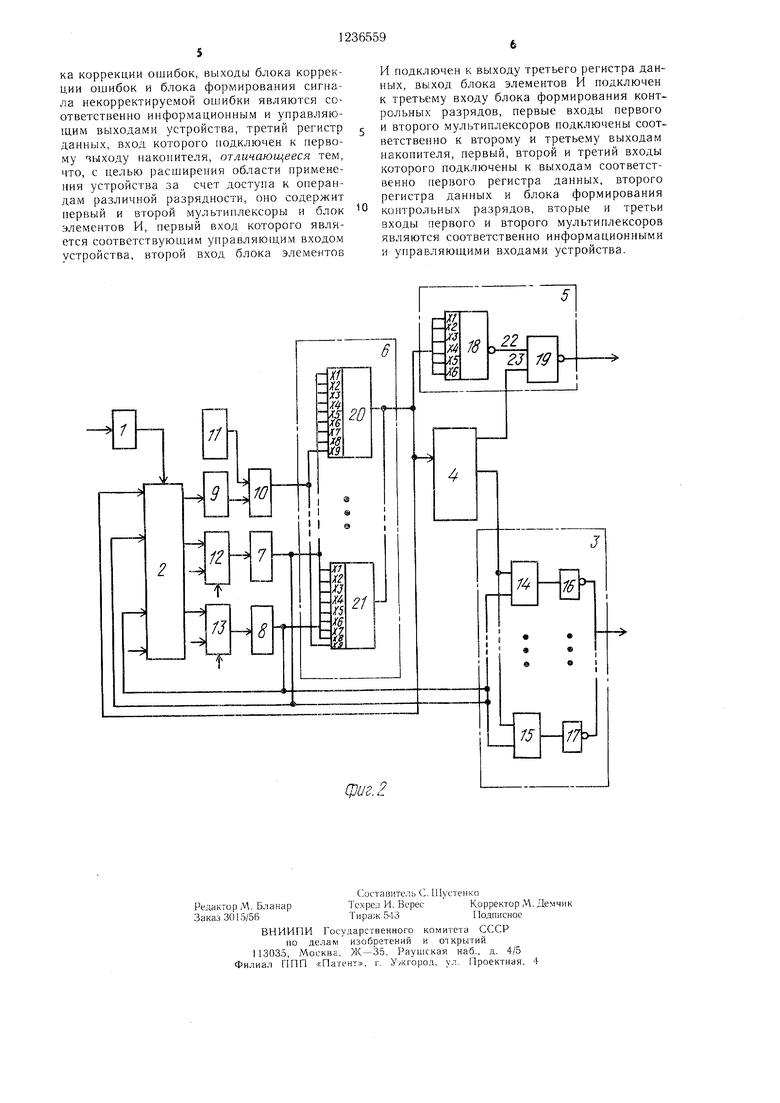

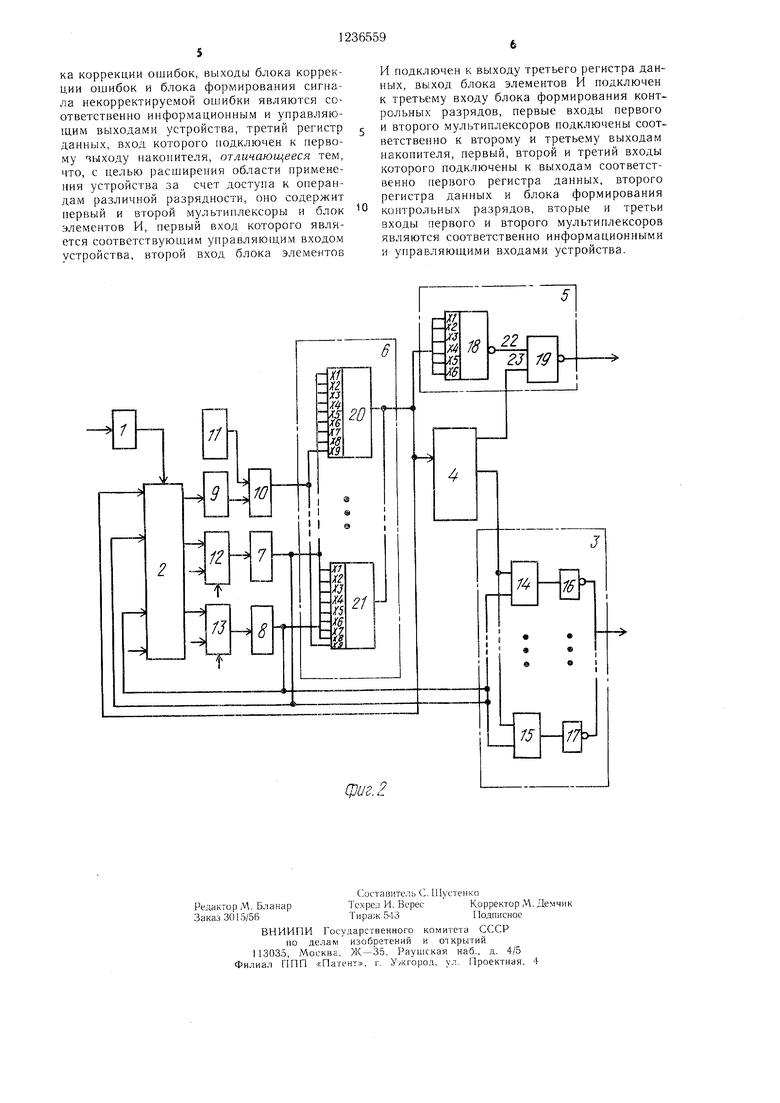

На фиг. 1 изображена функциональная схема; на фиг. 2 - реализация запоминающего устройства с исправлением ошибок.

Запоминающее устройство с исправлени- ем ощибок содержит регистр 1 адреса, накопитель 2, блок 3 коррекции ощибок, дещифра- тор 4,блок 5 формирования сигнала некорректируемой ошибки, блок 6 формирования контрольных разрядов, регистры 7-9 данных,, блок 10 элементов И, формирователь i 1 сигналов управления, мультиплексоры 12 и 13.

Блок 3 коррекции ошибок содержит логические элементы исключающие ИЛИ 14 и 15 и элементы НЕ 16 и 17, а блок 5 формирования сигнала некорректируемой ошибки со- держит блок 18 контроля четности и соединенный с ним элемент И-НЕ 19. Блок 6 формирования контрольных разрядов имеет в своем составе блоки 20 и 21 контроля четности.

Запоминающее устройство с исправле- нием ошибок работает следующим образом.

При записи слова информационные разряды с вторых входов мультиплексоров 12 (младщий байт), 13 (старший байт) заносят в регистры данных 7 (младший байт) и 8 (старший байт). С выходов регистров 7 и 8 данные поступают на вход накопителя 2 и вход блока 6 формирования контрольных разрядов.

Во время операции записи формирователь 11 сигналов управления подает на вто- рые входы блока 10 низний уровень, блокируя таким образом выход регистра 9, содержащий контрольные разряды. В это время на выходе блока 6 формируются контрольные разряды Хэмминга, соответствующие кодовому слову в регистрах 7 и 8. После этого контрольные биты и биты данных записывают в накопитель 2 по адресу, определяемому регистром 1 адреса.

Запись байта отличается от записи слова тем, что записываемый байт данных че- рех второй вход соответствующего мульти- плексора 12(13) заносят в регистр данных 7(8), второй байт в это время считывают из ячейки накопителя 2 по адресу, хранящемуся в регистре I адреса, и через первый вход другого мультиплексора 13(12) поступает в регистр 8(7) данных. Дальнейшее

прохождение информации такое же как и при записи слова.

В режиме считывания кодовое слово из накопителя 2, через одни входы мультиплексоров 12 и 13 заносят в регистры 7 и 8 данных, а контрольные разряды в регистр 9. Во время операции чтения формирователь 11 сигналов управления подает на вход блока 10 единичный уровень, подключая таким образом на вход блока 6 формирования контрольных разрядов выход регистра 9. Блок 6 производит формирование новых контрольных разрядов для данных фактически считанных из памяти. Однако на этот раз на вход блока 6 с регистра 9 поступают также контрольные разряды, сформированные во время операции записи. Старые контрольные биты складываются по модулю 2 с вновь сформированными контрольными битами, образуя таким образом биты синдрома, которые поступают на дешифратор 4, определяющий однократную ошибку, и на вход блока 5 формирования сигнала некорректируемой ошибки. Дешифратор 4 производит преобразование битов синдрома в биты состояния. При появлении однократной ошибки на линии одного из битов состояния появляется низкий уровень, обозначающий ошибку, бита.

Биты состояния поступают на первые входы логических элементов исключающее ИЛИ 14 и 15. На вторые входы этих элементов поступают соответствующие биты данных, хранящиеся в регистрах данных 7 и 8. За элементами 14 и 15 следуют элементы НЕ 16 и 17, тем самым обеспечивается исправление ошибки. Если ошибки нет, то бит, хранящийся в регистре 7(8) данных, передается через логические элементы исключающее ИЛИ 14 и 15 и элементы НЕ 16 и 7 без изменения. При появлении двукратной ошибки на выходе блока 5 формирования сигнала некорректируемой ошибки появляется активный уровень, который свидетельствует о том, что происходит неисправимая ошибка. Преобразование информационного слова в блоке 6 производится в соответствии с модифицированным кодом Хэмминга.

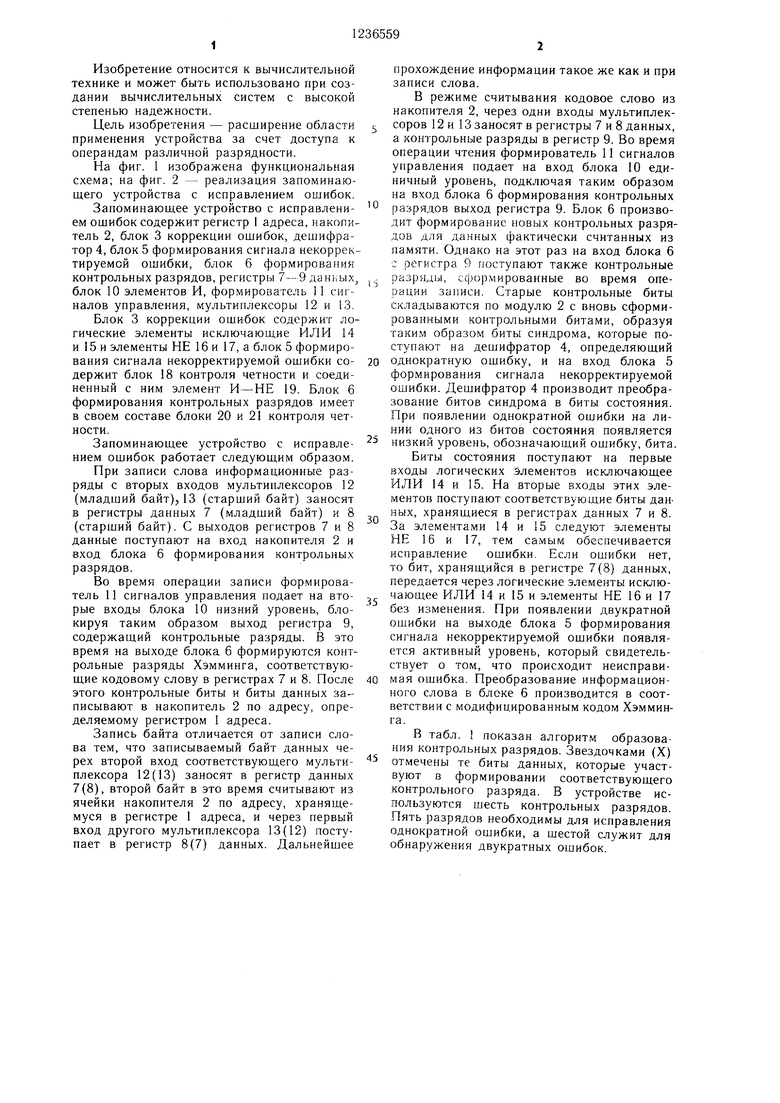

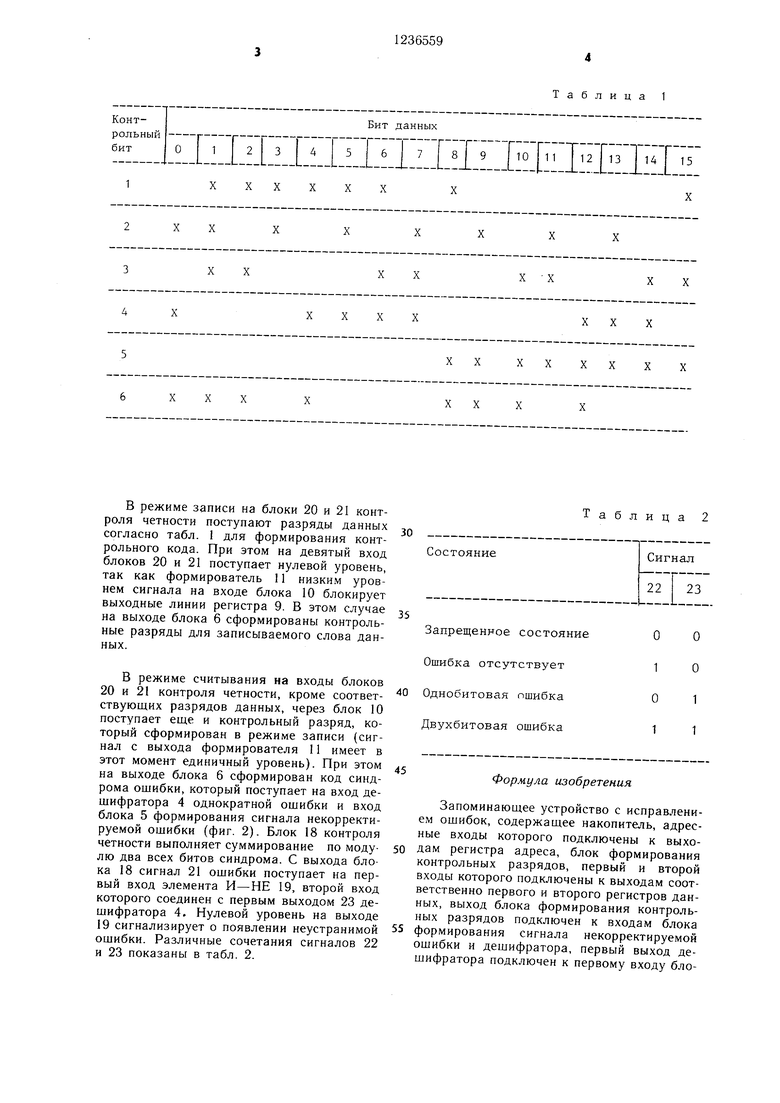

В табл. показан алгоритм образования контрольных разрядов. Звездочками (X) отмечены те биты данных, которые участвуют в формировании соответствующего контрольного разряда. В устройстве используются шесть контрольных разрядов. Пять разрядов необходимы для исправления однократной ошибки, а шестой служит для обнаружения двукратных ошибок.

В режиме записи на блоки 20 и 21 контроля четности поступают разряды данных согласно табл. 1 для формирования контрольного кода. При этом на девятый вход блоков 20 и 21 поступает нулевой уровень, так как формирователь 11 низким уровнем сигнала на входе блока 10 блокирует выходные линии регистра 9. В этом случае на выходе блока 6 сформированы контрольные разряды для записываемого слова данных.

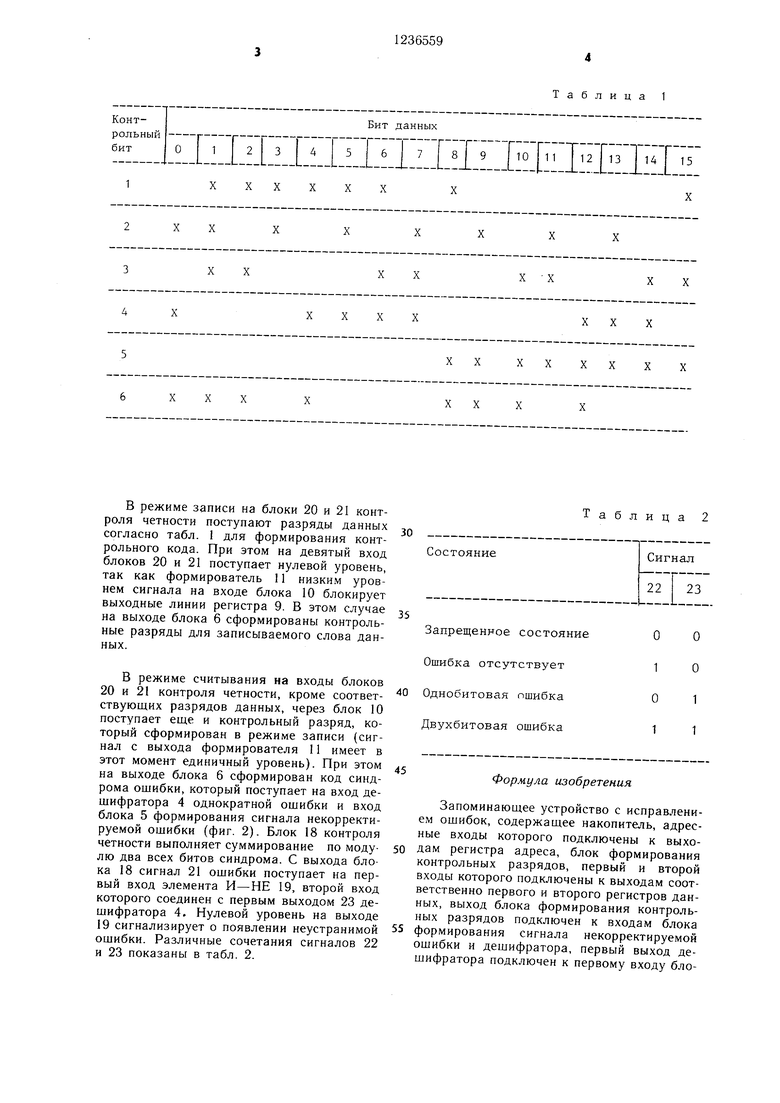

В режиме считывания на входы блоков 20 и 21 контроля четности, кроме соответствующих разрядов данных, через блок 10 поступает еще и контрольный разряд, который сформирован в режиме записи (сигнал с выхода формирователя 11 имеет в этот момент единичный уровень). При этом на выходе блока б сформирован код синдрома ошибки, который поступает на вход дешифратора 4 однократной ошибки и вход блока 5 формирования сигнала некорректируемой ошибки (фиг. 2). Блок 18 контроля четности выполняет суммирование по модулю два всех битов синдрома. С выхода блока 18 сигнал 21 ошибки поступает на первый вход элемента И-НЕ 19, второй вход которого соединен с первым выходом 23 дешифратора 4. Нулевой уровень на выходе 19 сигнализирует о появлении неустранимой ошибки. Различные сочетания сигналов 22 и 23 показаны в табл. 2.

Таблица 1

Таблица 2

30

Состояние

Сигнал

г

22 23

Запрещенное состояние

Ошибка отсутствует

Однобитовая ошибка

Двухбитовая ошибка

0О

1О

01

11

45

Формула изобретения

Запоминающее устройство с исправлением ошибок, содержащее накопитель, адресные входы которого подключены к выходам регистра адреса, блок формирования контрольных разрядов, первый и второй входы которого подключены к выходам соответственно первого и второго регистров данных, выход блока формирования контрольных разрядов подключен к входам блока

формирования сигнала некорректируемой ошибки и дешифратора, первый выход дешифратора подключен к первому входу блока коррекции ошибок, выходы блока коррекции ошибок и блока формирования сигнала некорректируемой ошибки являются соответственно информационным и управляющим выходами устройства, третий регистр данных, вход которого нодключен к нерво- му выходу накопителя, отличающееся тем, что, с целью расширения области применения устройства за счет доступа к операндам различной разрядности, оно содержит первый и второй мультиплексоры и блок элементов И, первый вход которого является соответствующим управляющим входом устройства, второй вход блока элементов

И подключен к выходу третьего регистра данных, выход блока элементов И подключен к третьему входу блока формирования контрольных разрядов, первые входы первого и второго мультиплексоров подключены соответственно к второму и третьему выходам накопителя, первый, второй и третий входы которого подключены к выходам соответственно первого регистра данных, второго регистра данных и блока формирования Koin-рольных разрядов, вторые и третьи входы первого и второго мультиплексоров являются соответственно информационными и управляющими входами устройства.

Г

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и исправления ошибок в блоках вычислительной машины | 1982 |

|

SU1111169A1 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372367A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737510A1 |

| Устройство для коррекции ошибок в информации | 1986 |

|

SU1372365A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1985 |

|

SU1274006A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737511A1 |

| Запоминающее устройство с самоконтролем | 1987 |

|

SU1432613A1 |

| Запоминающее устройство с исправлением ошибок | 1981 |

|

SU982098A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| САМОКОРРЕКТИРУЮЩЕЕСЯ УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ | 2004 |

|

RU2297030C2 |

Изобретение относится к вычислительной технике и может быть использовано при создании вычислительных систем с высокой степенью надежности. Целью изобретения является расширение области применения устройства за счет осуществления доступа к операндам различной разрядности. Устройство содержит регистр 1 адреса, накопитель 2. блок 3 коррекции ошибок, дешифратор 4, блок Бформирования сигнала некорректируемой ошибки, блок 6 формирования контрольных разрядов, регистры 7-9 данных, блок 10 элементов И, формирователь И сигналов управления, мультиплексоры 12 и 13. Цель изобретения достигается введением мультиплексоров и блока элементов И с соответствующими функциональными связями. 2 ил, 2 табл. 5 и /Г Ь (Л 12 ю со О5 ел СП СО /J J

| Электроника, 1979, № 24, с | |||

| Скоропечатный станок для печатания со стеклянных пластинок | 1922 |

|

SU35A1 |

| Устройство для бескольцевого прядения | 1968 |

|

SU282098A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-06-07—Публикация

1984-09-28—Подача