to ел

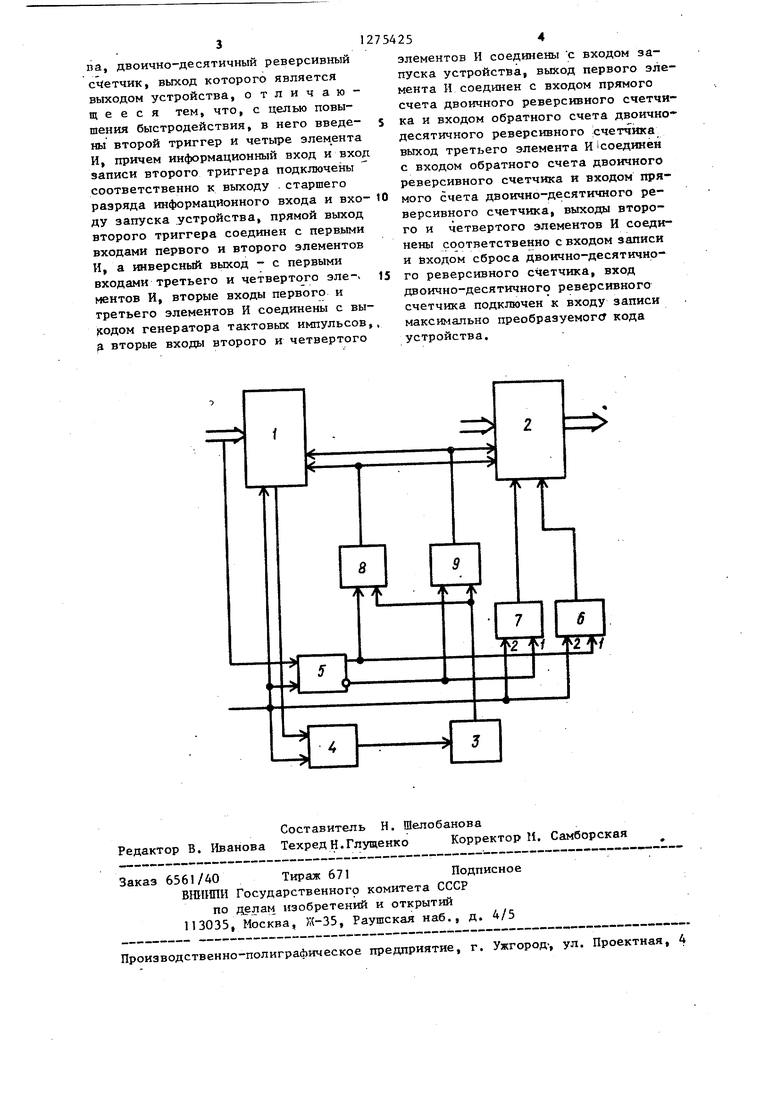

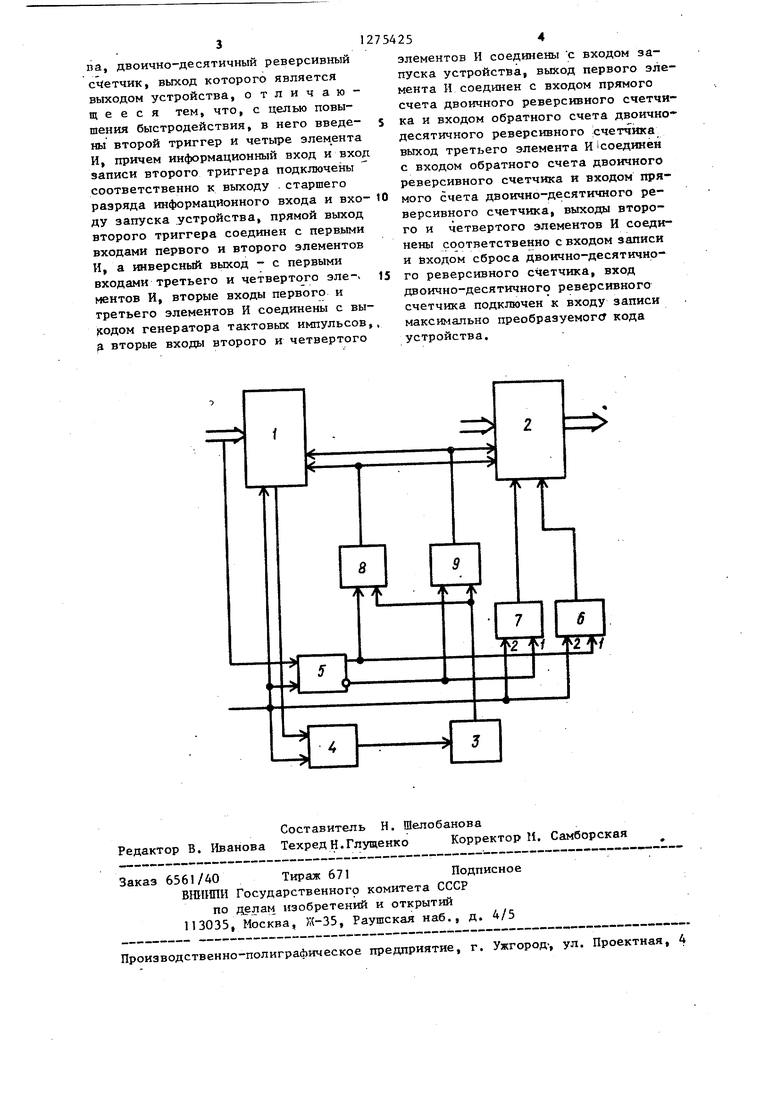

ю сд Изобретение относится к вычислительной технике и может быть исполь зовано для сопряжения большинства периферийных устройств при преобразовании чисел большой разрядности. Цель изобретения - повышение быстродействия при обработке чисел большой разрядности. На чертеже показана структурная схема предлагаемого устройства для преобразования кодов. Устройство содержит двоичный реверсивный счетчик 1, двоично-деся тичный реверсивный счетчик 2, генератор 3 тактовых импульсов, первый и второй триггеры 4и 5, элементы Н 6-9, На входе двоично-десятичного Сче чика установлен двоично-десятичный код максимального чиЪла N , которому соответствуют все единицы на вхо де устройства. Такое конструктивное выполнение устройства для преобразования кодов сокращает максимальное время преобр зования кодов за счет того, что в зависимости от состояния старшего разряда двоичный c4eT4Hk досчитьгоае N импульсов до нуля, либо N импульсов до N.. При .этом двоичнодесятичный счетчик начинает считать соответственно либо от нуля и досч тывает до числа N. либо от N и до ( читывает до числа . Таким обра , зом, в обоих случаях на выходе двоично-десятичного счетчика устанавли вается двоично-десятичный код преоб разуемого числа N, а генератор так товых импульсов вырабатывает импуль сы, максимальное количество которых не превьппает , т,е, время преобразования максимального числа уменьшается в 2 раза. Устройство работает следующим образом. Преобразуемый двоичный код числа .N установлен на входе устройства. По команде, поступившей на управляю щий вход, этот код записывается в двоичный реверсивный счетчик 1, уст навливает триггер 4 в единичное состояние, записьтает старший разряд двоичного кода преобразуемого числа N в триггер 5, Единичное состояние .триггера Д разрешает генератору 3 тактовых импульсов работу. Если преобразуемое число то в триггер 5 запишется О, При этом единица на инверсном выходе 25 . триггера 5 подается на вход элемента И 7 и вход Элемента И 9; команда, поступившая на вход запуска устройства, проходит через элемент И 7 и обнуляет двоично-десятичный счетчик, а импульсы с генератора 3,тактовых импульсов через элемент И 9 поступают на счетчики 1 и 2, После того, как двоичный реверсивный счетчик 1, работающий в режиме вычитания, отсчитывает N импульсов, импульс переноса двоичного реверсивного счетчика I сбросит триггер 4 в нулевое состояние и генератор 3 тактовых импульсов прекратит работу. При этом двоично-десятичный счетчик 2, работающий в режиме прямог счета, отсчитывает N импульсов и на выходе устройства установится двоично-десятичный код.числа N, Если преобразуемое число , то в триггер 5 запишется 1, При этом команда с управляющего входа устройства не поступает на вход обнуления двоично-десятичного счетчика, а через элемент И 6 поступает на вход записи двоично-десятичного счетчика 2, в котором запишется число N . При этом импульсы генератора тактовых импульсов 3 через элемент И 8 поступают на счетчики 1 и 2, После того, как двоичный реверсивный счетчик 1, работающий в режиме прямого счета, досчитает до N , сигнал переноса обнулит триггер 4 и генератор 3, тактовых импульсов, выработавший N N -N импульсов, прекратит работу. Двоично -десятичньй счетчик 2, работающий в режиме вычитания, пропустит N импульсов и на выходе устройства установливается двоично-десятичный код числа N N., Формула изобретения Устройство для преобразования двоичного кода в двоично-десятичный Код, содержащее двоичный реверсивный счетчик, информационный вход которого соединен с информационным входом устройства, выход переноса двоичного реверсивного счетчика подключен к входу сброса первого триггера, выход которого соединен с входом генератора тактовых импульсов, вход установки первого триггера и вход записи двоичного реверсивного счетчика соединены с входом запуска устройстпа, двоично-десятичный реверсивный с етчик, выход которого является выходом устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены второй триггер и четьфе элемента И, причем информационный вход и вход записи второго триггера подключены соответственно к выходу . старшего разряда информационного входа и входу запуска устройства, прямой выход второго триггера соединен с первыми входами первого и второго элементов И, а инверсный выход - с первыми входами третьего и четвертого элементов И, вторые входы первого и третьего элементов И соединены с вы(содом генератора тактовых импульсов вторые входы второго и четвертого 254 элементов И соединены с входом запуска устройства, выход первого элемента И соединен с входом прямого счета двоичного реверсивного счетчика и входом обратного счета двоично десятичного реверсивного счетчика выход третьего элемента Исоединен с входом обратного счета двоичного реверсивного счетчика и входом прямого счета двоично-десятичного реверсивного счетчика, выходы второго и четвертого элементов И соединень соответственно с входом записи и входом сброса двоично-десятичного реверсивного счетчика, вход двоично-десятичного реверсивного счетчика подключен к входу записи максимально преобразуемого кода устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1974 |

|

SU620975A1 |

| Устройство для преобразования двоичного кода в двоично-десятичношестидесятиричный | 1977 |

|

SU734668A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1983 |

|

SU1124282A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1982 |

|

SU1086424A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1986 |

|

SU1349008A2 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1989 |

|

SU1667259A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1984 |

|

SU1266008A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1977 |

|

SU732853A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

Изобретение относится к области вычислительной техники и мЫкет быть использовано для сопряжения большинства йериферийных устройств при преобразовании чисел большой разрядности. Цель изобретения повьшение быстродействия преобразования при обработке чисел большой разрядности. Указанная цель достигается благодаря введению в преобразователь второго триггера и четырех злементов И с соответствующими связями. 1 ил.

| Справочник по интегральным микросхемам | |||

| /Под ред | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Тарабрина | |||

| М.: Энергия, 1981, с | |||

| Счетная линейка для вычисления объемов земляных работ | 1919 |

|

SU160A1 |

| Преобразователь двоичного кода в десятичный | 1973 |

|

SU504200A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-07—Публикация

1983-12-30—Подача