Изобретение относится к вычислительной технике и может быть использовано в устройствах предварительной обработки информации, в частности в анализаторах спектра, а также в качестве операционного блока аналоговых и аналого-цифровых вычислительных систем.

Цель изобретения - упрощение устройства и расширение функциональных возможностей за счет реализации режима хранения результата.

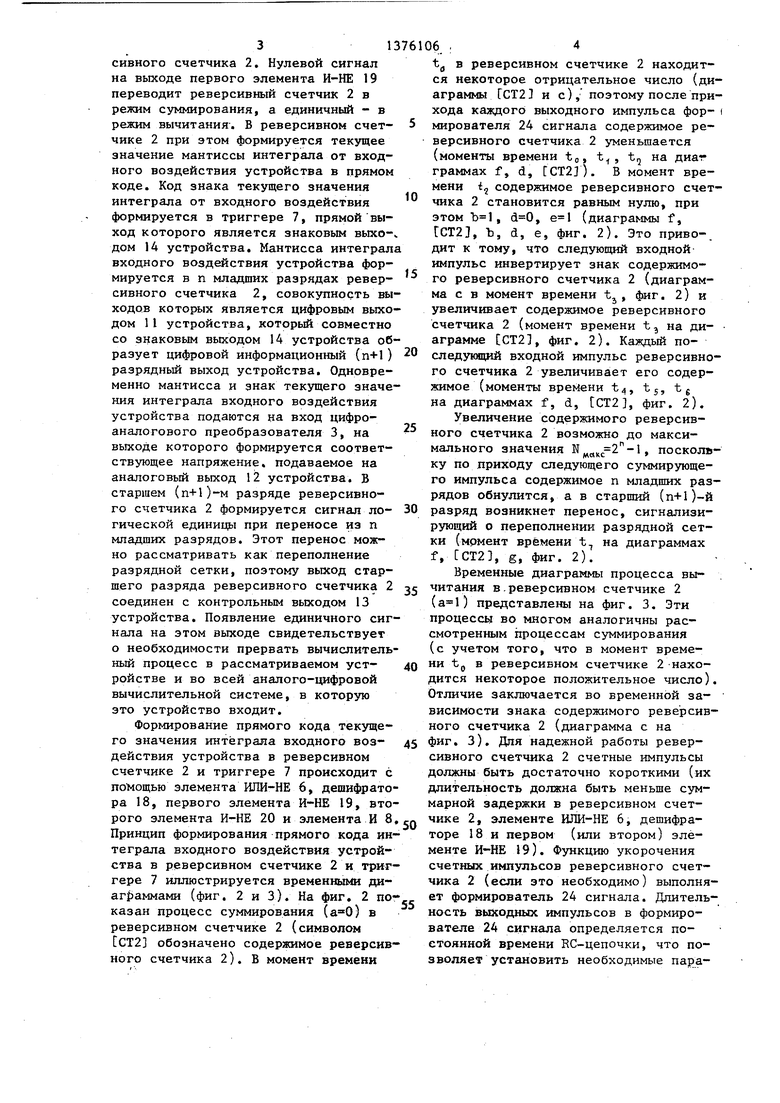

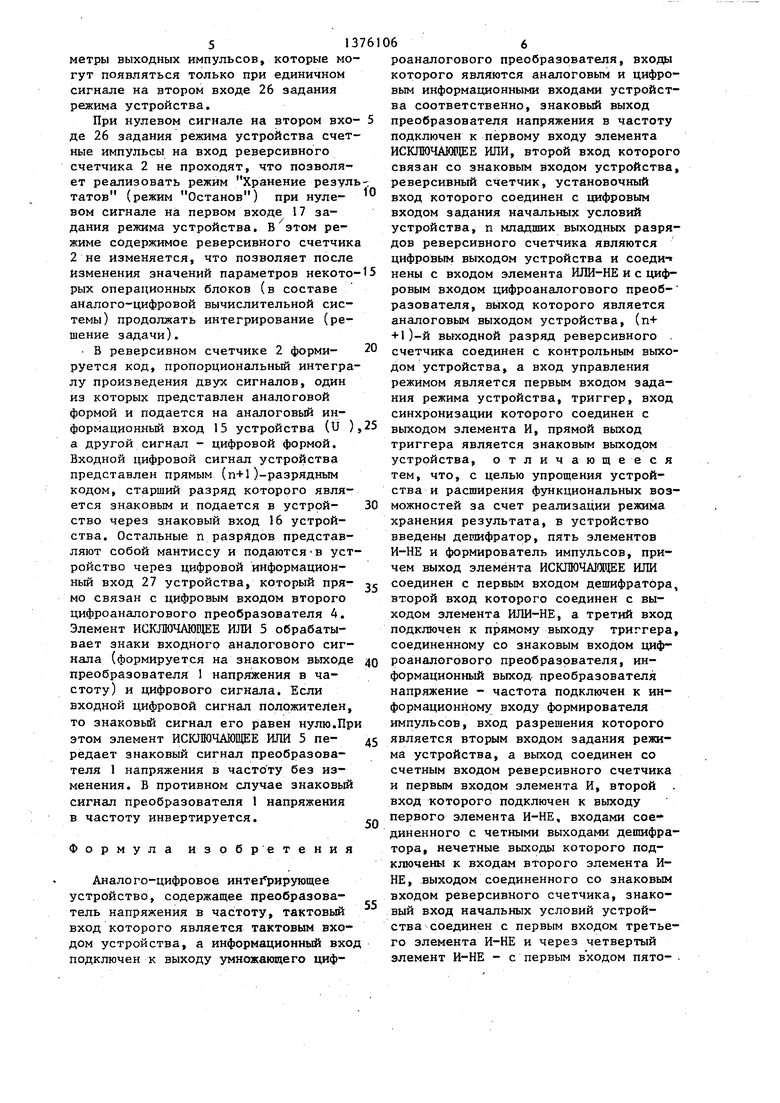

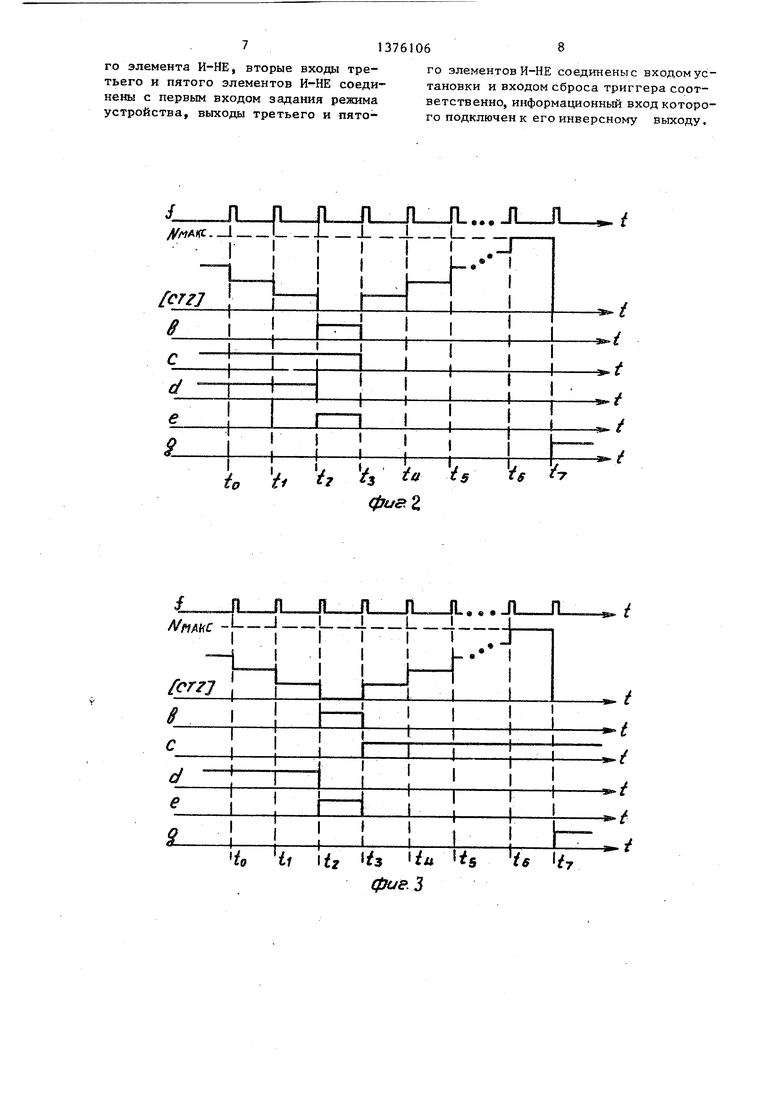

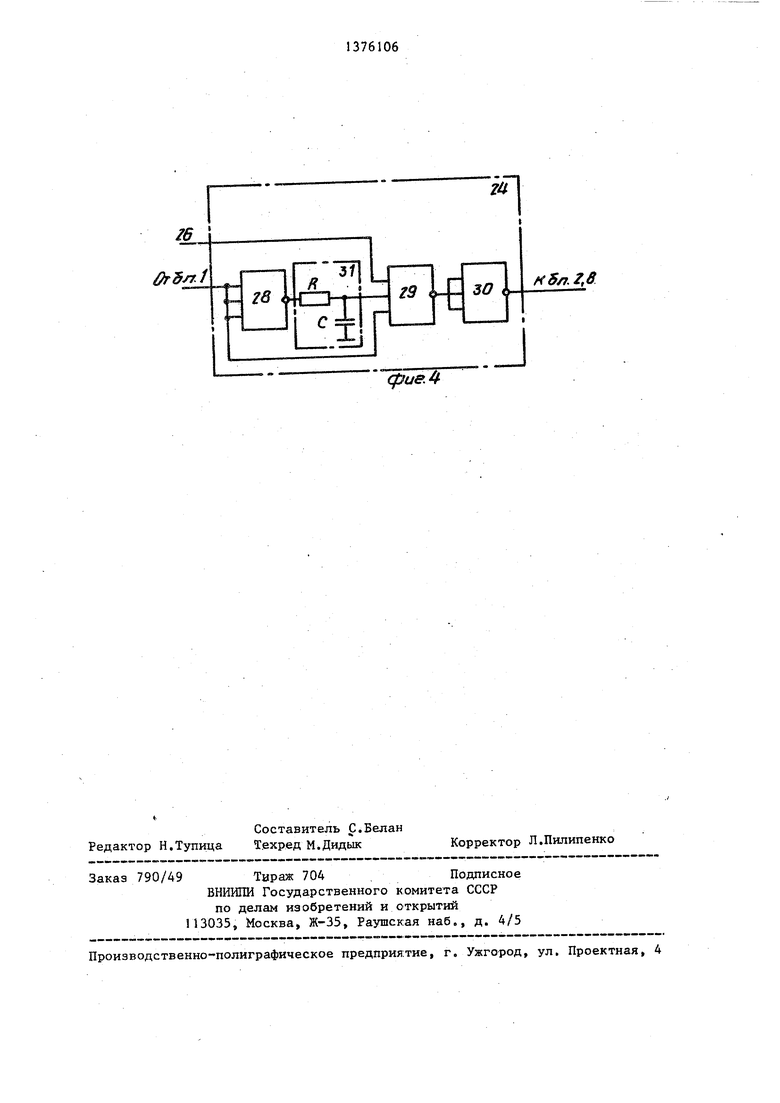

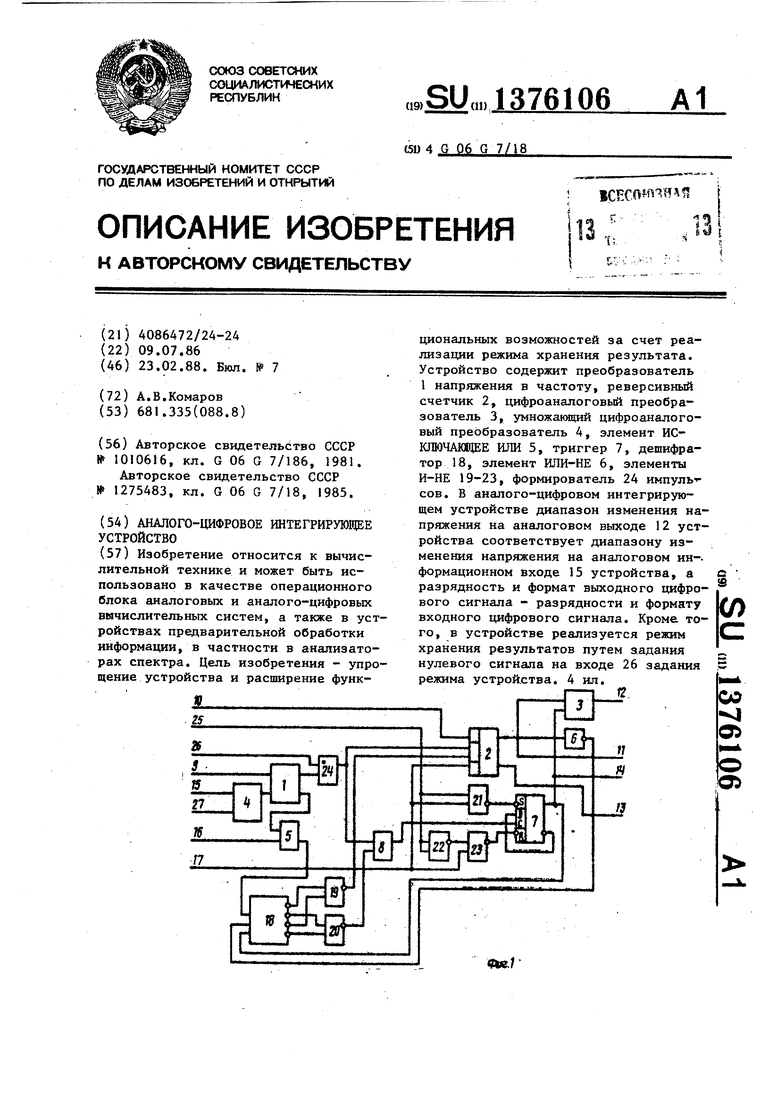

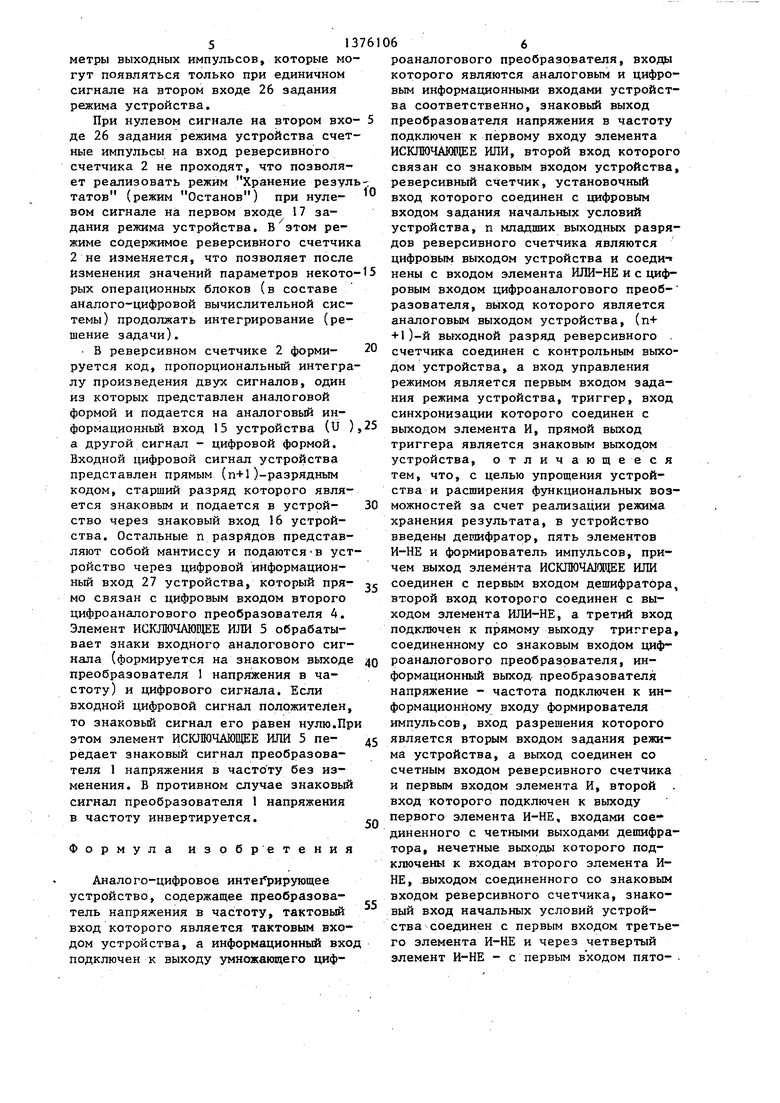

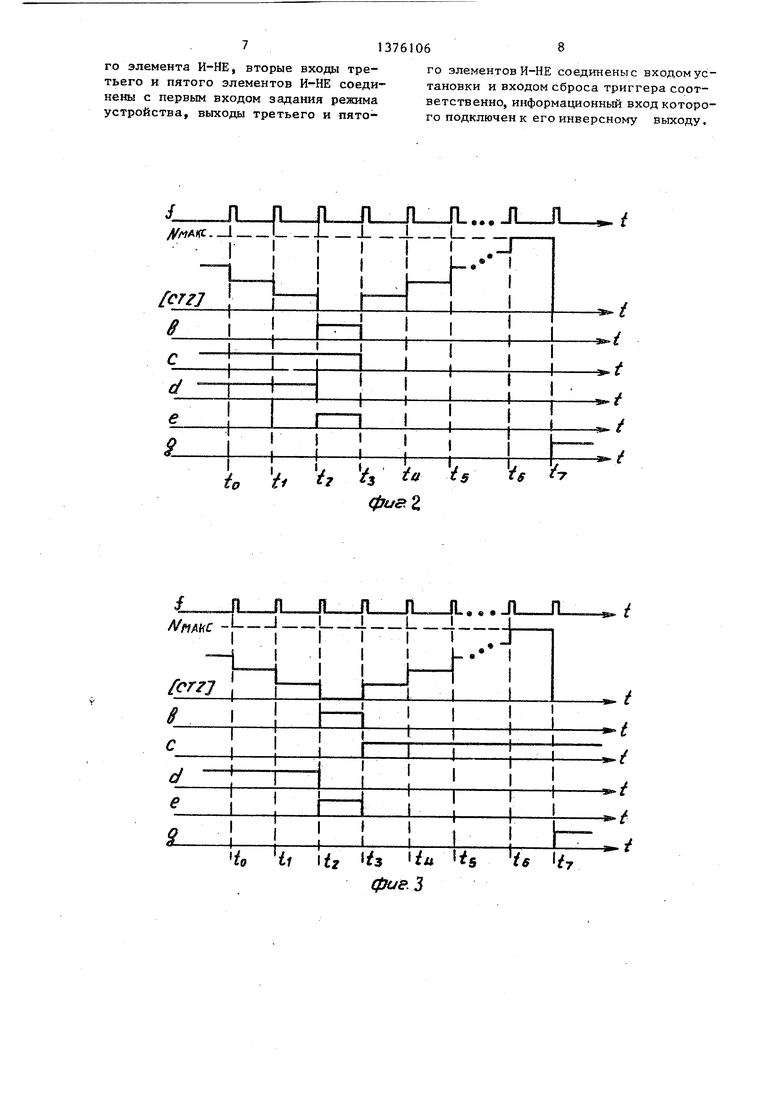

На фиг. 1 представлена функциональ ная схема аналого-цифрового интегрирующего устройства; на фиг. 2 - временные Диаграммы работы реверсивного счетчика, триггера и дешифратора при выполнении операции суммирования в реверсивном счетчике; на фиг. 3 - то же, при выполнении операции вычитания -в реверсивном счетчике; на фиг.4 принципиальная схема формирователя импульсов.

Аналого-цифровое интегрирующее устройство (фиг. 1) содержит преобразователь 1 напряжения в частоту, реверсивный счетчик 2, цифроанало- говый преобразователь 3, умножающий цифроаналоговый преобразователь 4, элемент ИСКЛЮЧАЮВ ЕЕ ИЛИ 5, элемент ИЛИ-НЕ 6, триггер 7, элемент И 8, тактовый вход 9 устройства, цифровой вход 10 начальных условий устройства, цифровой выход И устройства, ан логовый выход 12 устройства, контрольный выход 13 устройства, знаковый выход 14 устройства, аналоговый информационный вход 15 устройства, знаковый вход 16 устройства, первый вход 17 задания режима устройства, дешифратор 18, пять элементов И-НЕ 19-23, формирователь 24 импульсов, знаковый вход 25 задания начальных условий устройства, второй вход 26 задания режима устройства, цифровой информационный вход 27 устройства.

Формирователь 24 импульсов (фиг.4 содержит три элемента И-НЕ 28-30 и интегрирующую КС-цепь 31, причем входы элемента И-НЕ 28 являются входом, а выход элемента И-НЕ 30 - выходом формирователя.

Устройство функционирует в трех режимах: Подготовка, Работа и Хранение результата. Режим Подготовка устанавливается единичными значениями сигналов на входах 17 и 26 устройства и используется для установки начальных условий в аналого

0

5

0

5

0

5

0

5

0

5

цифровом интегрирующем устройстве.- Начальные условия представлены прямым кодом, мантисса которого подается на цифровой вход 10 начальных условий устройства, а знак - на знаковый вход 25 начальных условий устройства. При единичном сигнале на входе 17 устройства реверсивный счетчик 2 переводится в режим приема информации с установочного входа, что позволяет записать в его младпте разряды любой п-разрядный код, подав его на вход 10 устройства. В старший (п+1)-й разряд при этом записывается нуль, поскольку (п+1)-й разряд установочного входа реверсивного счетчика 2 связан с общей точкой устройства. Единичное значение сигнала иа входе 17 устройства также позволяет записать в триггер 7 код знака начальных условий, подав его на вход 25 устройства. При этом используется канал предустановки триггера 7, в который входят третий 21, четвертый 22 и пятый 23 элементы И-НЕ. При йереходе сигнала на входе 17 устройства из единичного значения в нулевое (при единичном сигнале на входе 26 устройства) устройство переходит в режим Работа. Реверсивный счетчик 2 при этом переходит в счетный режим и его содержимое меняется после прихода каждого импульса на его счетный вход.

Эти импульсы формируются на информационном выходе преобразователя 1 напряжения в частоту и при необходимости, обостряются (укорачиваются) с помощью формирователя 24 сигнала. Импульсы на выходе формирователя 24 сигнала представляют собой приращения интеграла входного воздействия устройства. Знак приращения формируется на знаковом выходе преобразователя 1 напряжения в частоту в виде того или иного значения логической переменной. Так, нулевое значение этой переменной определяет приращение положительной величины интеграла, а единичное значение - приращение отрицательной величины интеграла. Значение логической переменной на знаковом выходе преобразователя 1 напряжения в частоту управляет режимом реверсивного счетчика 2, поскольку знаковый выход преобразователя 1 напряжения в частоту через первый вход элемента ИСКЛЮЧАЮЩЕ ИЛИ 5, дешифратор 18 и первый элемент И-НЕ 19 соединен со знаковым входом реверсивного счетчика 2. Нулевой сигнал на выходе первого элемента И-НЕ 19 переводит реверсивный счетчик 2 в режим суммирования, а единичный - в режим вычитания. В реверсивном счетчике 2 при этом формируется текущее значение мантиссы интеграла от входного воздействия устройства в прямом коде. Код знака текущего значения интеграла от входного воздействия формируется в триггере 7, прямой выход которого является знаковым выхо- дом 14 устройства. Мантисса интеграла входного воздействия устройства формируется в п младщих разрядах реверсивного счетчика 2, совокупность выходов которых является цифровым выходом 11 устройства, который совместно со знаковым выходом 14 устройства образует цифровой информационный (п+1) разрядный выход устройства. Одновременно мантисса и знак текущего значения интеграла входного воздействия устройства подаются на вход цифро- аналогового преобразователя 3, на выходе которого формируется соответствующее напряжение, подаваемое на аналоговый выход 12 устройства, В старшем (п+1)-м разряде реверсивного счетчика 2 формируется сигнал логической единицы при переносе из п младших разрядов. Этот перенос можно рассматривать как переполнение разрядной сетки, поэтому выход старшего разряда реверсивного счетчика 2 соединен с контрольным выходом 13 устройства. Появление единичного сигнала на этом выходе свидетельствует о необходимости прервать вычислительный процесс в рассматриваемом устройстве и во всей аналого-цифровой вычислительной системе, в которую это устройство входит.

Формирование прямого кода текущего значения интеграла входного воздействия устройства в реверсивном счетчике 2 и триггере 7 происходит с помощью элемента ИЛИ-НЕ 6, дешифратора 18, первого элемента И-НЕ 19, второго элемента И-НЕ 20 и элемента И 8, Принцип формирования прямого кода интеграла входного воздействия устройства в реверсивном счетчике 2 и триггере 7 иллюстрируется временными диаграммами (фиг, 2 и 3), На фиг. 2 показан процесс суммирования () в реверсивном счетчике 2 (символом СТ2 обозначено содержимое реверсивного счетчика 2), В момент времени

0

5

0

5

0

5

0

5

0

5

t|j в реверсивном счетчике 2 находится некоторое отрицательное число (диаграммы ГСТ2 и с), поэтому после прихода каждого выходного импульса фор- ( мирователя 24 сигнала содержимое реверсивного счетчика 2 уменьшается (моменты времени to, t, t на диаг граммах f, d, CT2i). В момент времени t содержимое реверсивного счетчика 2 становится равным нулю, при этом , , (диаграммы f, ГСТ2, Ъ, d, е, фиг, 2). Это приводит к тому, что следующий входной импульс инвертирует знак содержимого реверсивного счетчика 2 (диаграмма с в момент времени tj, фиг, 2) и увеличивает содержимое реверсивного счетчика 2 (момент времени t, на ди- аграмме СТ2, фиг, 2), Каждый по- следз ющий входной импульс реверсивного счетчика 2 увеличивает его содержимое ( моменты времени t, t5, tg на диаграммах f, d, ГСТ2, фиг, 2),

Увеличение содержимого реверсивного счетчика 2 возможно до максимального значения , поскольку по приходу следующего суммирующего импульса содержимое п младших разрядов обиулится, а в старщий (п+1)-й разряд возникнет перенос, сигнализирующий о переполнении разрядной сетки (мрмент времени t на диаграммах f, СТ2, g, фиг, 2).

Временные диаграммы процесса вычитания в.реверсивном счетчике 2 () представлены на фиг, 3, Эти процессы во многом аналогичны рассмотренным процессам суммирования (с учетом того, что в момент времени tp в реверсивном счетчике 2 находится некоторое положительное число), Отличие заключается во временной зависимости знака содержимого реверсивного сметчика 2 (диаграмма с на фиг, 3), Для надежной работы реверсивного счетчика 2 счетные импульсы должны быть достаточно короткими (их длительность должна быть меньше суммарной задержки в реверсивном счетчике 2, элементе ИЛИ-НЕ 6, дешифраторе 18 и первом (или втором) элементе И-НЕ 19), Функцию укорочения счетных импульсов реверсивного счетчика 2 (если это необходимо) выполняет формирователь 24 сигнала. Длительность выходных импульсов в формирователе 24 сигнала определяется постоянной времени RC-цепочки, что позволяет установить необходимые пара513

метры выходных импульсов, которые могут появляться только при единичном сигнале на втором входе 26 задания режима устройства.

При нулевом сигнале на втором вхо- де 26 задания режима устройства счетные импульсы на вход реверсивного счетчика 2 не проходят, что позволяет реализовать режим Хранение результатов (режим Останов) при нуле- вом сигнале на первом входе 17 задания режима устройства. В этом режиме содержимое реверсивного счетчика 2 не изменяется, что позволяет после изменения значений параметров некоторых операционных блоков (в составе аналого-цифровой вычислительной системы) продолжать интегрирование (решение задачи).

В реверсивном счетчике 2 форми- руатся код, пропорциональный интегралу произведения двух сигналов, один из которых представлен аналоговой формой и подается на аналоговый информационный вход 15 устройства (U ) а другой сигнал - цифровой формой. Входной цифровой сигнал устройства представлен прямым (п+1)-разрядным кодом, старший разряд которого является знаковым и подается в устрой- ство через знаковый вход 16 устройства. Остальные п разрядов представляют собой мантиссу и подаютсяв устройство через цифровой информационный вход 27 устройства, который пря- МО связан с цифровым входом второго цифроаналогового преобразователя 4. Элемент ИСКЛЮЧАЮВ ЕЕ ИЛИ 5 обрабатывает знаки входного аналогового сигнала (формируется на знаковом выходе преобразователя 1 напряжения в частоту) и цифрового сигнала. Если входной цифровой сигнал положителен, то знаковый сигнал его равен нулю.При этом элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5 пе- редает знаковый сигнал преобразователя 1 напряжения в частоту без изменения. В противном случае знаковый сигнал преобразователя 1 напряжения в частоту инвертируется.

Формула изоб ре тения

Аналого-цифровое инте1 рирующее устройство, содержащее преобразователь напряжения в частоту, тактовый вход которого является тактовым входом устройства, а информационный вход подключен к выходу умножающего циф

5

0 5 0 r 0 З

0

5

066

роаналогового преобразователя, входы которого являются аналоговьм и цифровым информационными входами устройства соответственно, знаковый выход преобразователя напряжения в частоту подключен к первому входу элемента ИСКЛЮЧАМЦЕЕ ИЛИ, второй вход которого связан со знаковым входом устройства, реверсивнь1й счетчик, установочный вход которого соединен с цифровым входом задания начальных условий устройства, п младших выходных разрядов реверсивного счетчика являются цифровым выходом устройства и соеди- нены с входом элемента ИЛИ-НЕ и с цифровым входом цифроаналогового преоб- разователя, выход которого является аналоговым выходом устройства, (п+ +1)-й выходной разряд реверсивного . счетчика соединен с контрольным выходом устройства, а вход управления режимом является первым входом задания режима устройства, триггер, вход синхронизации которого соединен с выходом элемента И, прямой выход триггера является знаковым выходом устройства, отличающееся тем, что, с целью упрощения устройства и расширения функциональных возможностей за счет реализации режима хранения результата, в устройство введены дешифратор, пять элементов И-НЕ и формирователь импульсов, причем выход элемента ИСКШ)ЧА1 ЯЦЕЕ ИЛИ соединен с первым входом дешифратора, второй вход которого соединен с выходом элемента ИЛИ-НЕ, а третий вход подключен к прямому выходу триггера, соединенному со знаковым входом цифроаналогового преобразователя, информационный выход преобразователя напряжение - частота подключен к информационному входу формирователя импульсов, вход разрешения которого является вторым входом задания режима устройства, а выход соединен со счетным входом реверсивного счетчика и первым входом элемента И, второй вход которого подключен к выходу первого элемента И-НЕ, входами соединенного с четными выходами дешифратора, нечетные выходы которого подключены к второго элемента И- НЕ, выходом соединенного со знаковым входом реверсивного счетчика, знаковый вход начальных условий устройства соединен с первым входом третьего элемента И-НЕ и через четвертый элемент И-НЕ - с первым входом пято- .

71376106

го элемента И-НЕ, вторые входы третьего и пятого элементов И-НЕ соединены с первым входом задания режима устройства, выходы третьего и пято8

го элементов И-НЕ соединеныс входом установки и входом сброса триггера соответственно, информационный вход которого подключен к его инверсному выходу.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровое интегрирующее устройство | 1985 |

|

SU1275483A1 |

| Устройство для интегрирования функций | 1982 |

|

SU1070570A1 |

| Устройство для интегрирования функций | 1984 |

|

SU1242993A1 |

| Синхронный фильтр | 1985 |

|

SU1317649A2 |

| Синхронный фильтр | 1983 |

|

SU1131028A1 |

| Следящий аналого-цифровой преобразова-ТЕль | 1979 |

|

SU828401A1 |

| Аналого-дискретное интегрирующее устройство | 1986 |

|

SU1432563A2 |

| Преобразователь форматов данных | 1982 |

|

SU1092490A1 |

| Синхронный фильтр | 1984 |

|

SU1246343A1 |

| Многоканальная система для анализа формы и регистрации аналоговых процессов | 1983 |

|

SU1149242A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве операционного блока аналоговых и аналого-цифровых вмчислительных систем, а также в устройствах предварительной обработки ииформахщи, в частности в анализаторах спектра. Цель изобретения - упрощение устройства и расширение функциональных возможностей за счет реализации режима хранения результата. Устройство содержит преобразователь 1 напряжения в частоту, реверсивный счетчик 2, цифроаналоговый преобразователь 3, умножакяций цифроаналоговый преобразователь 4, элемент ИС- КШЗЧАЩЕЕ ИЛИ 5, триггер 7, дешифратор 18, элемент ИЛИ-НЕ 6, элементы И-НЕ 19-23, формирователь 24 импуль- сов. В аналого-цифровом интегрирующем устройстве диапазон изменения напряжения на аналоговом выходе 12 устройства соответствует диапазону изменения напряжения на аналоговом ин-- формационном входе 15 устройства, а разрядность и формат выходного цифрового сигнала - разрядности и формату входного цифрового сигнала. Кроме того, в устройстве реализуется режим хранения результатов путем задания нулевого сигнала на входе 26 задания режима устройства. 4 шт. С. (/) СО Од О5 .Г

п п п п

0U&Z

л

л

сриеЛ

| Интегрирующее устройство | 1981 |

|

SU1010616A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аналого-цифровое интегрирующее устройство | 1985 |

|

SU1275483A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-02-23—Публикация

1986-07-09—Подача