сл

Изобретение относится к вычислительной технике и может быть использовано для контроля и диагностики цифровых блоков и узлов, преимущественно для встроенного контроля.

Цель изобретения поззышение достоверности контроля за счет анализа сигнатур в промежуточных точках входной последовательности.

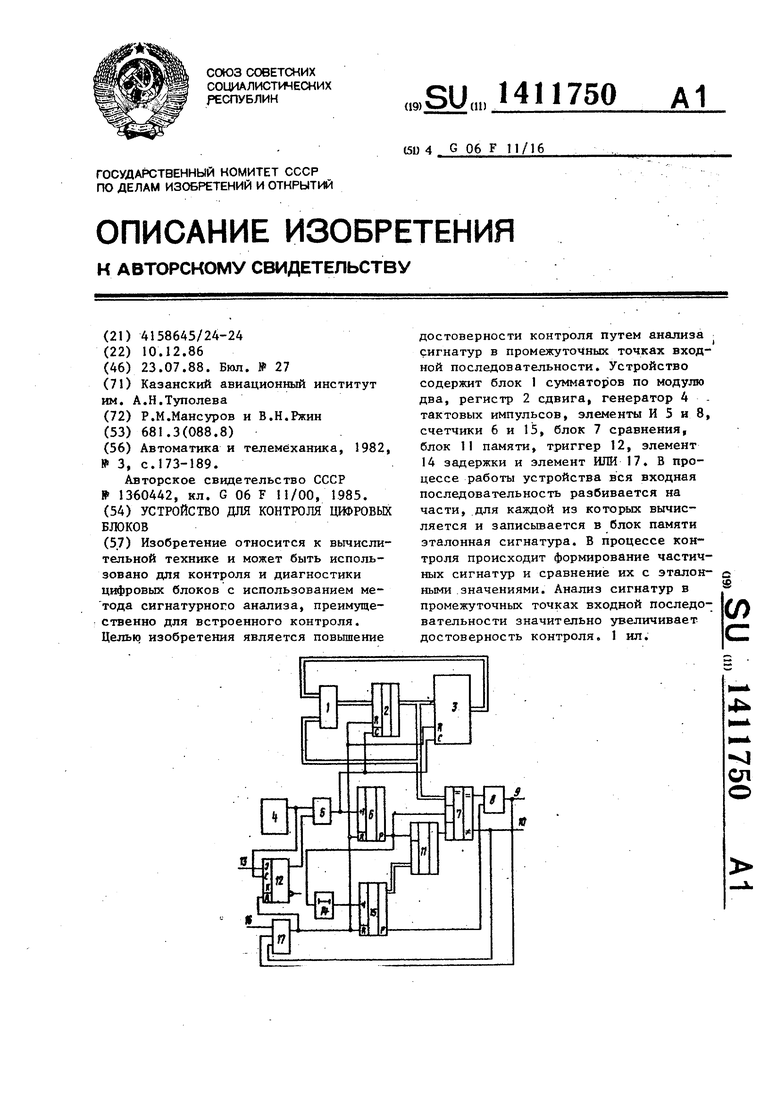

На чертеже представлена функциональная схема устройства.

Устройство содержит блок I сумматоров по модулю два, регистр 2 сдвига. Обозначен контролируемый цифровой блок 3с Кроме TorOs устройство содержит генератор 4 тактовых импульсов, первый элемент И 5;, первый счетчик 6, блок 7 cpaBHeHHHj второй элемент И 8э выход 9 сигнала исправности, выход 10 сигнале неисправности, блок 1 памяти, триггер 12,.вход 13 Пуск элемент 14 задержки, второй счетчик 15, вход 16 сброса и элемент ИЛИ 17.

Устройство работает следующим образом.

Перед началом работы в устройство поступает сигнал по входу 16 сброса, который проходит через элемент ИЛИ 17 и- згстанавливает в начальное состояние регистр 2 сдвига, сбрасьшает в кулевое состояние первый б и второй 15 счетчики (тактов), устанавливает в начальное состояние контролируеь-шгй блок 3 и в нулевое состояние триггер 12 Далее сигналов по входу 13 Пуск триггер 12 устанавливается в единичное состояние. Первый элемент И 5 открывается и импульсы с выхода генератора 4, проходя через первый элемент И 5, поступают на входы синхронизации регистра 2 сдвига, контролируемого блока 3 и на счетный вход первого счетчика б, инициируя их работу

Двоичные числа, порождаемые автономным генератором, с группы выходов регистра 2 сдвига поступают на пер- группу входов блока 7 сравнения, на группу входов контролируемого блока 3 и на первую грзп:шу входов блока I сз маторов ,по модулю два. Реакции на тестовые воздействия контролируе мого блока 3 поступают в виде двоичных комбинаций на вторую группу вхо- дон блока I сумматоров по модулю два участвуя тем самым в формировании очередного тестового числа в регистре 2 сдвига. Таким образом, регистр

0

5

0

5

е

0

5

O

2 сдвига вместе с блоком 1 сумматоров по модулю два. Реакции на тестовые воздействия контролируемого блока 3 поступают в виде двоичных комбинаций на вторую группу входов блока 1 суг1маторов по модулю два, участвуя тем самым в формировании очередного тестового числа в регистре 2 сдвига, Таким образом, регистр 2 сдвига вместе с. блоком 1 сз мматорбв ..по модулю два представляет собой сигнатурный анализатор, сворачивающий выходную информацию контролируемого блока 3,

Через определенное количество тактов импульс с выхода переполнения первого счетчика 6 (тактов) поступает на вход чтения блока 11 памяти и на стробирующий вход блока 7 сравнения. Тем самым сравнивается число, содержащееся в регистре 2 сдвига, с эталонной сигнатурой, находящейся в нулевой ячейке блока 11 памяти,При несовпадении указанных чисел на выходе несовпадения блока 7 сравнения формируется сигнал, который поступает на выход 10 сигнала неисправности и на третий вход элемента ИЛИ 17, что приводит устройство в исходное состояние. При совпадении чисел работа устройства не прерывается, а сигнал с выхода переполнения первого счетчика 6, пройдя через элемент 14 задержки, поступает на счетный вход второго счетчика 15, тем самым подготавливается к считьшанию следующая ячейка блока 11 памяти, так как груп па информационных выходов второго счетчика 15 (тактов) подключена к адресным входам блока I1 памяти,

При очередном переполнении первого счетчика 6 происходит очередное сравнение блоком 7 сравнения содержимого регистра 2 сдвига и следующей эталонной сигнатуры. Таким образом устройство производит неоднократное сравнение содержимого регистра 2 сдвига с эталонными сигнатурами. Число сравнений определяется -емкостью второго счетчика 15, Сигнал с выхода переполнения второго счетчика 15 разрешает прохождение через второй элемент И 8 импульса последнего сравнения с выхо- да блока 7 сравнения. Таким образом, на выходе 9 формрфуется сигнал исправности контролируемого блока 3, Этот же сигнал, поступая на второй вход элемента ШШ 17, прекращает работу устройства.

Таким образом, в предлагаемом устройстве в процессе контроля анализируется не только конечное состояние регистра сдвига, но и ряд промежуточных состоянийJ что повьгаает достоверность контроля.

Формула изобретения

Устройство для контроля цифровых блоков, содержащее регистр сдвига, блок сумматоров по модулю два, генератор тактовых импульсов, блок сравнения, первый элемент И, первый счетчик и триггер, причем группа выходов регистра сдвига подключена к первой группе информационных входов блока сравнения, к первой группе входов блока сумматоров по модулю два и является группой выходов стимуляции устройства для подключения к входам контролируемых блоков, вторая группа входов блока сумматоров по модулю два является группой информационных входов устройства для подключения вы ходов контролируемых блоков, группа выходов блока сумматоров по модулю два соединена с группой информационных входов регистра сдвига, выход генератора тактовых импульсов соединен с синхровходом триггера и первым вхо первого элемента И, второй вход которого соединен с выходом триггера а выход первого элемента И соединен, синхровходом регистра сдвига, счетным входом первого счетчика и являет- ся синхронизирующим выходом устройства для подключения к синхровходу контролируемого блока, единичный вход триггера является входом Пуск уст

ройства, выход переполнения первого

0

5

0

5 ,

0

счетчика соединен с входом строби- рования блока сравнения, выход несовпадения которого является выходом сигнала неисправности устройства, отличающееся тем, что, с целью повышения достоверности контроля за счет анализа сигнатур в промежуточных точках входной последовательности, устройство содержит второй счетчик, блок памяти, второй элемент И, элемент ИЛИ и элемент -задержки, вход которого объединен с входом чтения блока памяти и подключен к выходу переполнения первого счетчика, выход элемента задержки соединен со счетным входом второго счетчика,группа информационных выходов которого соединена с группой адресных входов блока памятиS группа выходов которого соединена с второй Группой информационных входов блока сравнения, вход сброса второго счетчика объединен с входом сброса триггера и подключен к выходу элемента ИЛИ, первый вход ко- торого является входом сброса устройства, выход совпадения блока сравнения соединен с первым входом второго элемента Ид второй вход которого подключен к выходу переполнения второго счетчика, выход второго элемента И соединен с вторым входом элемента ИЛИ и является выходом сигнала исправности устройства, йыход несовпадения блока сравнения соединен с третьим входом элемента ИЛИ, выход которого подключен к входам сброса триггера, регистр сдвига и первого счетчика и является выходом устройства для подключения к входу сброса контролируемого блока

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1987 |

|

SU1527636A1 |

| Устройство для тестирования цифровых блоков | 1988 |

|

SU1656540A1 |

| Сигнатурный анализатор (его варианты) | 1984 |

|

SU1252784A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1401462A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU868843A1 |

| Устройство для диагностирования аппаратуры обработки данных | 1985 |

|

SU1390610A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1278854A1 |

| Устройство для контроля логических блоков | 1982 |

|

SU1105897A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля и диагностики цифровых блоков с использованием ме- тода сигнатурного анализа, преимущественно для встроенного контроля. Целью изобретения является повышение достоверности контроля путем анализа сигнатур в промежуточных точках входной последовательности. Устройство содержит блок 1 сумматоров по модулю два, регистр 2 сдвига, генератор 4 тактовых импульсов, элементы И 5 и 8, счетчики 6 и 15, блок 7 сравнения, блок II памяти, триггер 12, элемент 14 задержки и элемеит ИЛИ 17. В процессе работы устройства вся входная последовательность разбивается на части, .для каждой из которых вычисляется и записьшается в блок памяти эталонная сигнатура. В процессе контроля происходит формирование частичных сигнатур и сравнение их с эталонными значениями. Анализ сигнатур в промежуточных точках входной последовательности значительно увеличивает достоверность контроля. I ил. с (Л

| Автоматика и телемеханика, 1982, 3, с.173-189 | |||

| Авторское свидетельство СССР 1360442, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-07-23—Публикация

1986-12-10—Подача