га с эталонной сигнатурой, содержащейся во втором блоке 6 памяти. В случае несовпадения сигнатур на выходе несравнения блока 7 сравнения появляется сигнал, который поступает на выход 10 сигнала неисправности устройства. Если сигнатуры, содержа- циеся во втором блоке 6 памяти и в регистре 2 сдвига, совпадают, то сигнал с выхода сравнения блока 7 сравнения поступает на суммируюп1ий

вход счетчика 5 адреса, инициируя новый цикл работы. Если все контролыме сигнатуры совпадают с соответствующими этаж) сигнатурами блока 6 памяти, то импульс переполнения с вы- кода счетчика 5 адреса поступает на выход 19 исправности устройства. За счет формирования и анализа нескольких сигнатур на нескольких кодовых кольцах значительно повышается достоверность контроля. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестирования цифровых блоков | 1988 |

|

SU1656540A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1411750A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1278854A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1354196A2 |

| Устройство для встроенного контроля блоков ЦВМ | 1987 |

|

SU1534463A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1302285A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU868843A1 |

| Устройство для контроля логических блоков | 1980 |

|

SU902018A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1589280A2 |

Изобретение может быть использовано в вычислительной технике и может найти применение при разработке устройств с встроенным контролем. Цель изобретения - повышение достоверности контроля цифровых блоков путем контроля проверяемых блоков на нескольких кодовых кольцах. Процесс контроля начинается с приходом сигнала по шине 15 пуска, вследствие чего содержимое нулевой ячейки первого блока 3 памяти поступает на вторую группу входов регистра 2 сдвига, который вместе с блоком 1 сумматоров по модулю два представляет собой сигнатурный анализатор, сворачивающий выходную информацию контролируемого блока 4. Блок 7 сравнения сравнивает итоговую сигнатуру в регистре 2 сдвига с эталонной сигнатурой, содержащейся во втором блоке 6 памяти. В случае несовпадения сигнатур на выходе несравнения блока 7 сравнения появляется сигнал, который поступает на выход 10 сигнала неисправности устройства. Если сигнатуры, содержащиеся во втором блоке 6 памяти и в регистре 2 сдвига, совпадают, то сигнал с выхода сравнения блока 7 сравнения поступает на суммирующий вход счетчика 5 адреса, инициируя новый цикл работы. Если все контрольные сигнатуры совпадают с соответствующими эталонными сигнатурами блока 6 памяти, то импульс переполнения с выхода счетчика 5 адреса поступает на выход 19 исправности устройства. За счет формирования и анализа нескольких сигнатур на нескольких кодовых кольцах значительно повышается достоверность контроля. 2 ил.

Изобретение относится к вычислительной технике и может найти применение при разработке устройств для контроля цифровой аппаратуры.

Цель изобретения - повышение достоверности контроля.

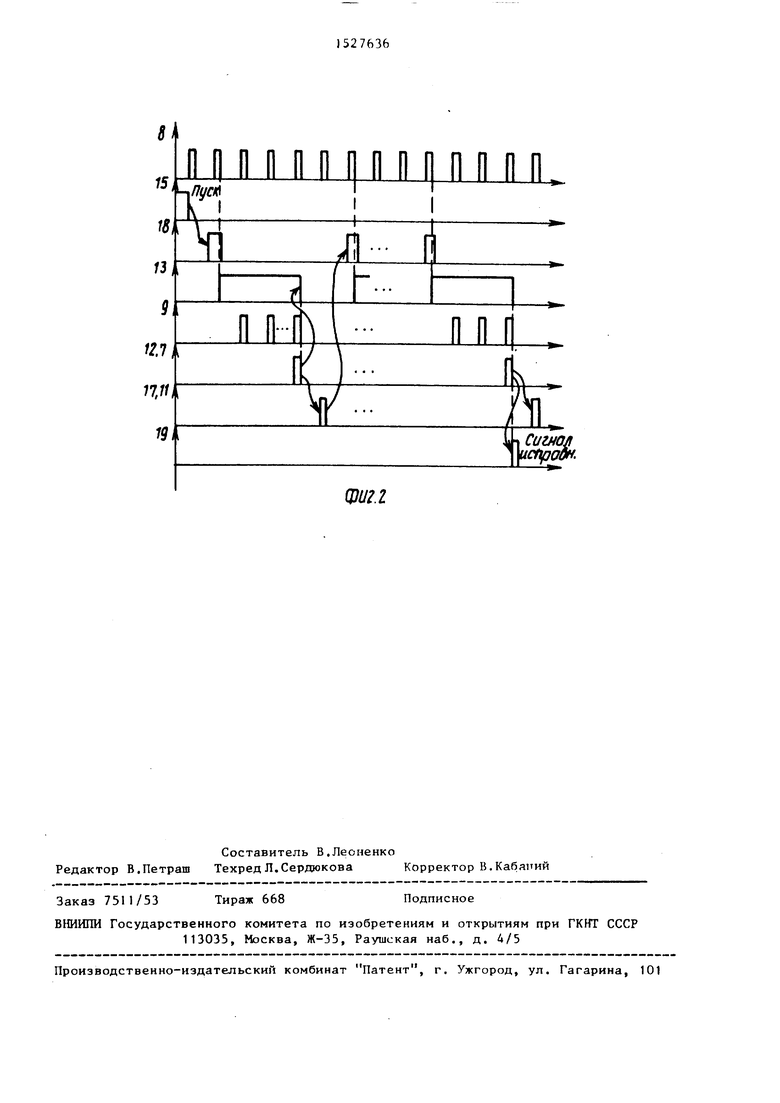

На фиг.1 представлена схема устройства контроля; на фиг.2 временная диаграмма работы устройства для случая исправного контролируемого блока.

Устройство содержит блок 1 сумматоров по модулю два, регистр 2 сдвига, блок 3 памяти, контролируемый блок 4, счетчик 5, блок 6 памяти, бло 7 сравнения, генератор 8 тактовых импульсов, элемент И 9, выход 10 сигнала неисправности устройства, элемент ИЛИ 11, счетчик 12, триггер 13, элемент ИЛИ 14, вход 15 пуска, вход 16 сброса, элементы 17 и 18 задержки, выход 19 исправности.

Устройство работает следуюидтм образом .

Перед началом работы в устройство поступает сигна. по входу 16, который проходит через элемент ИЛИ I4 и устанавливает в нт, левое состояние регистр

2,сбрасывает в нулевое состояние счетчик 12, устанавливает в начально состояние контролируемый блок 4 и в нулевое состояние триггер 13. Одновременно сигнал сброса устанавливает

в нулевое состояние счетчик 5. I

Сигнал пуска через элемент Ш1И 11

проходит на вход считывания блока 3, вследствие чего в регистр 2 записывается содержимое нулевой ячейки блока

0

5

0

5

0

5

0

5

элемент И 9, поступают на входы синхронизации регистра 2, контролируемого блока 4 и на суммирующий вход счетчика 12, инициируя их работу.

Двоичные числа, порождаемые автономным генератором, состоящим из регистра 2, блока 1 и контролируемого блока 4, с группы выходов регистра 2 поступают на группу входов контролируемого блока 4 и на вторую группу входов блока 1. Реакции контролируемого блока 4 на входные тестовые воздействия поступают в виде двоичных комбинаций на первую группу входов блока 1, участвуя тем самым в формировании очередного тестового числа в регистре 2. Таким образом, регистр 2 с блоком 1 представляют собой сигнатурный анализатор, сворачивающий выходную информацию контроли-руемого блока 4,

Через определенное количество так- тов испульс с выхода переполнения счетчика 12 поступает на вход считывания блока 6 и на управляющий вход блока 7. Тем самым сравнивается число, содержащееся в регистре 2, с эталонной сигнатурой, содержащейся в нулевой ячейке блока 6. Одновременно импульс переполнения, проходя через элемент ИЛИ 14, приводит устройство в исходное состояние. При несовпадении указанных чисел на выходе несравнения блок а 7 формируется сигнал, который поступает на выход 10.

Формула изобретения

Устройство для контроля цифровых блоков, содержащее регистр сдвига, генератор тактовых импульсов, блок сумматоров по модулю два, блок срав5

нения, первый счетчик, триггер и эле мент И, причем выход несравнения блока сравнения является выходом неис- равности устройства, отличающееся тем, что, с целью повьпие- нил достоверности контроля, в него ввeдe iы первый и второй элементы ИЛИ первый и второй элементы задержки, первый и второй блоки памяти, второй счетчик, причем первая группа входов блока сумматора по модулю два является информационн1 1ми входами устройства для подключения к выходам контролируемого блока, выходы блока сумматоров по модулю два соединены с первой группой информационных входов регистра сдвига, разрядные выходы которого соединены с второй группой входов блока сумматоров по модулю два, с первой группой информационных входов блока сравнения и являются выходами устройства для подключения к входам контролируемого цифрового блока, выход Равно блока сравнения соединен со счетным входом первого счетчика и входом первого элемента задержки, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого является входом пуска устройства, выход первого элемента ИЛИ соединен с входом второго элемента задержки и входом чтения

2

7636

первого блока памяти, выходы которого соединены с второй группой информационных входов регистра сдвига, разрядные выхоД 1Г первого счетчика соединены с адресными входами первого и второго блоков памяти, выходы второго блока памяти соединены с второй группой информационнъ Х входов блока

)Q сравнения, в(тход генератора тактовых импульсов соединен с первым входом элемента И и синхровходом триггера, выход которого соединен с вторым входом элемента И, выход второго эле-

.j мента задержки соединен с входом ус- тиовки триггера, выход элемента И является выходом устройства для подключения к синхровходу контролируемого цифрового блока и соединен с синхро20 входом регистра сдвига и счетным входом второго счетчика, выход зае- ма которого соединен с входом чтения второго блокад памяти, входом разрешения блока сравнения и первым входом

25 второго элемента РШИ, выход которого соединен с входами сбросов триггера, второго счетчика, регистра сдвига, второй вход второго элемента 11ЯИ является входом начальной установки

JQ устройства и соединен с входом уста НОНКИ первого счетчика, выход заема которого ярляется выходом исправности устройства.

тп

Составитель В.Лесиенко Редактор В.Петраш Техред Л.Сердюкова Корректор В. Каезаиий

Заказ 7511/53

Тираж 668

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Подписное

| Автоматика и телемеханика, 1982, № 3, 173-189 | |||

| Антенный коммутатор | 1985 |

|

SU1478195A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-12-07—Публикация

1987-06-15—Подача