(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1985 |

|

SU1257704A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1672527A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1163359A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1295451A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1444893A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1261010A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1249583A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1278979A2 |

| Буферное запоминающее устройство | 1984 |

|

SU1163357A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

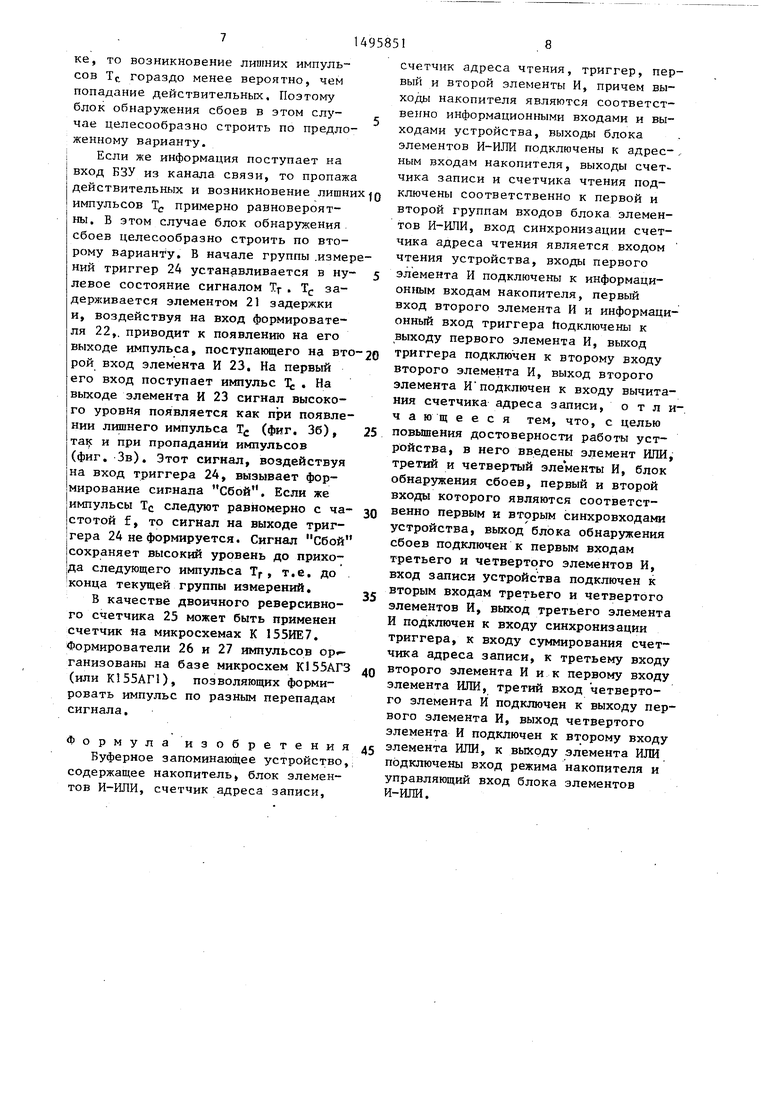

Изобретение относится к вычислительной технике и может быть использовано при построении буферных запоминающих устройств в системах сбора и обработки измерительной информации. Цель изобретения - расширение области применения за счет отбраковки измерений сбойных групп. Устройство содержит накопитель 1, блок 2 элементов И-ИЛИ, счетчики адреса записи 3 и чтения 4, элемент И 5, триггер 6, элементы И 7, 8, элемент ИЛИ 9, элемент И 10 и блок 11 обнаружения сбоев. 4 ил.

IS

Гг

4 со ел

00

ел

JZ«

Фиг.1

Тс П

Изобретение относится к области нычислительиой техники и может быть использовано при построении буферных запоминающих устройств (БЗУ) в сие- темах сбора и обработки измерительно информации.

Цель изобретения - расширение области применения за счет текущей отбраковки измерений сбойных групп.

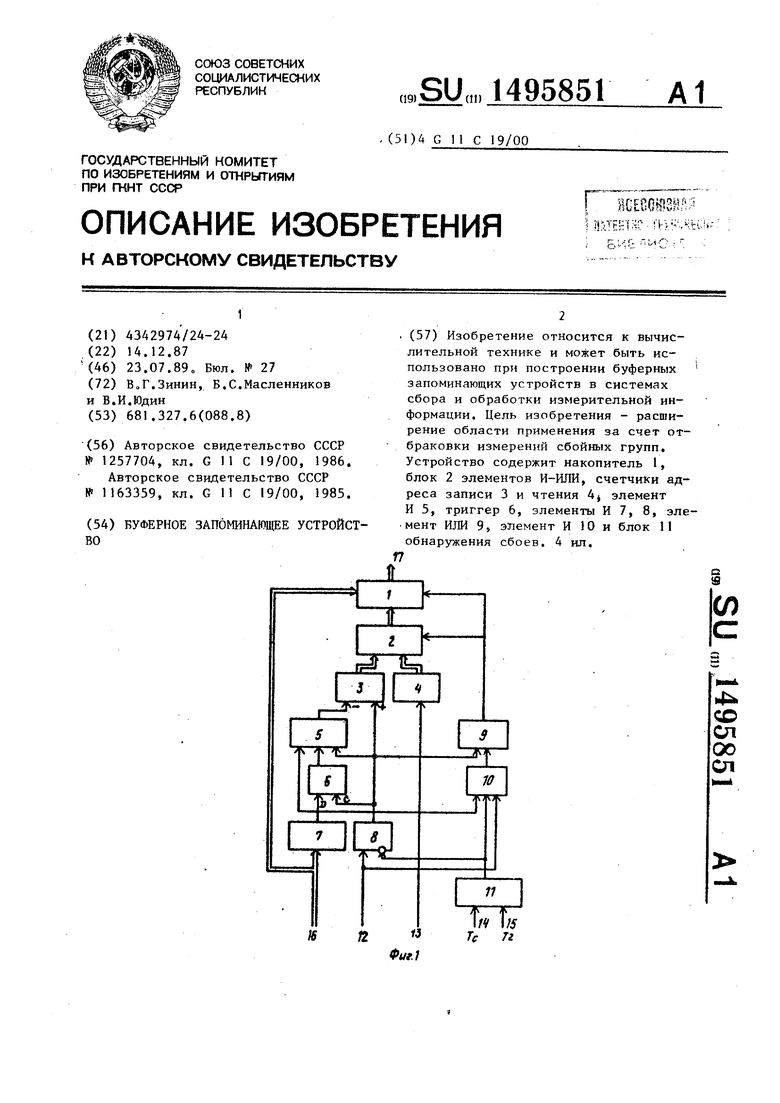

На фиг, 1 приведена структурная схема буферного запоминающего устройства; на фиг. 2 - структурная схема первого варианта блока определения сбоев и временная диаграмма его работы; на фиг, 3 - структурная схема второго варианта блока определения сбоев и временные диаграммы его работы; на фиг, 4 - схема счетчика адреса записи,

Устройство содержит накопитель 1, блок 2 элементов И-ИПИ, счетчик 3 адреса записи, счетчик 4 адреса чтения, элемент ИЗ, триггер .6, элементы И 7 и 8, элемент ИЛИ 9, элемент И 10, блок 11 обнаружения сбоев, вход 12 записи, вход 13 чтения, первый 14 синхровход устройства, второй 15 синхровход устройства, информационные входы 16 и выходы 17, формиро- ватель 18, элемент ИЛИ 19, триггер 20, элемент 21 задержки, формирователь 22, элемент И 23, триггер 24, реверсивный счетчик 25 и формирователи 26 и 27,

Устройство работает следукяцим образом.

Работа блока обнаружения сбоев основана на периодичности поступления импульсов Те. При пропадании внутри группы измерений хотя бы одного импульса TC на выходе узла обнаружения сбоев появляется высокий потенциал, сбрасываемый очередным сигналом Тр, Таким об разом-, при возникновении сбоя на выходе блока обнаружения сбоев до конца данной группы измерений устанавливается сигнал Сбой высокого уровня, свидетельствующий о том, что все Последующие измерения являются сбойными.

Работа устройства в режиме записи Перед началом работы счетчики 3 и 4 и трип ер 6 устанавливаются в вое состояние (цепь начальной уста- новки не показана). На входы элемента И 7 поступает часть входного-слова, содержащее разряды идентификатора. На выходе элемента И 7 формируется сигнал высокого уровня, если код идентификатора входного слова соответствует временной информации, и никого уровня, если код идентификатора соответствует измерительной информации. Выход элемента И 7 воздействует на информационный вход D-триггера 6, на первый вход элемента И 5 и на первый вход элемента И 10,

При отсутствии сбоя элемент И 8 открыт, а элемент И 10 закрыт для прохождения сигналов с входа 12 записи устройства,

В режиме записи информации на входе 12 записи устанавливается сигнал высокого уровня. Проходя через открытый при отсутствии сбоя элемент И 8 и элемент ИЛИ 9 он воздействует на третий вход .элементов И-ШШ 2, подключая к адресным входам накопителя 1 выходы счетчика 3 адреса записи. Высокий сигнал на выходе элемента ИЛИ 9, воздействуя на управляющий вход накопителя 1, переводит его в режим записи. По окончании записи сигнал на входе 12 принимает низкий уровень. Возникающий перепад сигнала на выходе элемента И 8, воздействуя на вход счетчика 3, увеличивает его содержимое до значения адреса следующей ячейки накопителя. Одновременно этот перепад сигнала, воздействуя на вход синхронизатора триггера 6, устанавливает его в единичное состояние, если на входе временная информация, и в нулевое состояние, если на входе -измерительная информация.

После записи информации в накопитель 1 на триггере 6 запоминается . вид записанной информации. Если при записи следукйцего слова его идентификатор принадлежит временной информации, то на выходе- элемента И 5 формируется сигнал высокого уровня. Возникший перепад сигнала на выходе элемента И 5, воздействуя на первый вход счетчика 3, уменьшает его содержимое до адреса записи предыдущего значения времени.

После записи слова времени в на- конитель 1 по заднему фронту сигнала на элементе И 8 содержимое счетчика 3 снова увеличивается до адреса следующей ячейки записи. Если входное слово содержит идентификатор измерительной информации, сигнал на -выходе элемента И 5 не формируется и со- .

держимое счетчика 3 перед записью информации в накопитель 1 не модифицируется.

Таким образом, если входной поток информации содержит участок, в котором между двумя измерениями содержатся несколько значений времени, то все эти значения записываются и хранятся по одному адресу. С приходом измерительной информации по адресу, куда записывается временная информация, запоминается последнее значение времени.

При появлении сбоя на выходе блока обнаружения сбоя появляется сигнал высокого уровня, закрывающий элемент И 8, для прохождения сигналов с входа 12 и воздействующий на второй вход элемента И 10. Если код идентификатора входного слова соответствует временной информации, на выходе элемента И 7 формируется сигнал высокого уровня, воздействующий на первый вход элемента И 10. Сигнал на вход 12 записи, проходя через элементы И 10 и ИЛИ 9, воздействует на вход управления блока 2 элементов И-ИЛИ, подключая к адресным входам накопителя 1 выходы счетчика 3 адреса записи. Высокий уровень сигнала с выхода элемента ИЛИ 9, воздействуя на вход режима накопителя 1, переводит его в режим записи. После записи временной информации в накопитель 1 содержимое счетчика 3 не модифицируется. Следующее значение времени записывается в ту же ячейку накопителя 1.

Если код идентификатора входного слова соответствует измерительной информации, а перед этим в данной группе фиксируется сбой, то сигнал на входе 12 не проходит ни через элемент И 8, закрытый при сбое, ни через схему И 10, закрытую при идентификаторе измерительной информации.

Таким образом, при возникновении внутри группы измерений сбоя в накопителе записьшаются измери - тельная информация, прошедшая до сбоя,и текущее значение времени.

В режиме чтения информации сигнал низкого уровня йа входе 12 воздействует на первый вход элемента И 8 и третий вход элемента И 10, что приводит к формированию сигнала низкого уровня на выходе элемента ИЛИ 9, который, воздействуя на третий вход

5851

элементов И-Ш1И 2, подключает к адресным входам накопителя 1 выход счетчика 4 адреса чтения. Одновременно низкий уровень сигнала на выходе элемента ШЖ 9, воздействуя на управляющий вход накопителя 1, переводит его в режим чтения. По концу чтения информации из накопителя 1 по сигна 0 лу на входе 13 чтения содержимое счетчика 4 адреса чтения увеличивается до адреса чтения следующей ячейки накопителя 1.

На первый и второй входы узла оп15 ределения сбоев поступают соответственно сигналы с первого (шина 14) и второго (шина 15) управляюпщх входов устройства. На выходе узла определения сбоев формируется сигнал

высокого уровня.

Работа первого варианта (фиг. 2) основана на периодичности поступле

ния импульсов TC с частотой f. Сигнал Т (шина 15) перекрывает по длительности сигнал Т. (шина 14), Формирователь 18 формирует по каждому заднему фронту импульсов Тс временной интервал длительностью, перекрывающей период следования импульсов Т. . Б начале группы измерений триггер 20 устанавливается в нулевое состояние сигналом Тг , при этом на его выходе присутствует сигнал низкого уровня. При равномерном поступлении с фиксированной частотой f импульсов 1 на выходе формирователя 18 будет постоянно держаться высокий уровень и сигнал Сбой на выходе триггера 20 формироваться не будет. При пропадании хотя бы одного импульса TC на выходе формирователя 18 на некоторое время установится низкий уровень, что вызовет, формирование сигнала Сбой на выходе триггера 18. Сигнал Сбой будет иметь высокий уровень до конца текущей группы измерений, т.е, до прихода следующего импульса Тр, Наличие в элементе ИЛИ 19 обусловлено Необходнмостью предварительной установки триггера 20 перед началом приема информации.

Эта схема не учитывает возможности возникновения лишних импульсов

TC, она анализирует лишь их пропадание. При этом,если информация поступает на вход БЗУ с какого-либо устройства магнитной регистрации, накопителя на магнитной ленте, диске, то возникновение лишних импульсов Те. гораздо менее вероятно, чем попадание действительных. Поэтому блок обнаружения сбоев в этом слу- чае целесообразно строить по предложенному варианту.

Если же информация поступает на вход БЗУ из канала связи, то пропажа действительных и возникновение лишни импульсов If, примерно равновероятны. В этом случае блок обнаружения сбоев целесообразно строить по второму варианту. В начале группы .измерний триггер 24 устанавливается в ну- левое состояние сигналом Т. Т задерживается элементом 21 задержки и, воздействуя на вход формирователя 22,. приводит к появлению на его выходе импульса, поступающего на вто рой вход элемента И 23. На первый его вход поступает импульс Ц, . На выходе элемента И 23 сигнал высокого уровня появляется как при появлении липнего импульса Т (фиг. Зб), та и при пропадании импульсов (фиг. Зв). Этот сигнал, воздействуя на вход триггера 24, вызывает фор- 1мирование сигнала Сбой. Если же I импульсы TC следуют равномерно с ча- |стотой f, то сигнал на выходе триг- jrepa 24 не формируется. Сигнал Сбой сохраняет высокий уровень до прихо- |да следующего импульса Tf, т.е. до конца текущей группы измерений.

В качестве двоичного реверсивного счетчика 25 может быть применен счетчик яа микросхемах К 155ИЕ7. Формирователи 26 и 27 импульсов ор.- ганизованы на базе микросхем К155АГЗ (или К155АГ1), позволяющих формировать импульс по разным перепадам сигнала.

Формула изобретен и я

Буферное запоминающее устройство содержащее накопитель блок элементов И-ИЛИ, счетчик адреса записи,

счетчик адреса чтения, триггер, первый и второй элементы И, причем выходы накопителя являются соответственно информационными входами и выходами устройства, выходы блока элементов подключены к адрес- ным входам накопителя, выходы счетчика записи и счетчика чтения подключены соответственно к первой и второй группам входов блока элементов И-ИЛИ, вход синхронизации счетчика адреса чтения является входом чтения устройства, входы первого элемента И подключены к информаци- ОН1СЫМ входам накопителя, первый вход второго элемента И и информационный вход триггера подключены к выходу первого элемента И, выход триггера подключен к второму входу второго элемента И, выход второго элемента И подключен к входу вычитания счетчика адреса записи, отличающееся тем, что, с целью повьшения достоверности работы устройства, в него введены элемент ИЛИ, третий и четвертый элементы И, блок обнаружения сбоев, первый и второй входы которого являются соответственно первым и вторым синхровходами устройства, выход блока обнаружения сбоев подключен к первым входам третьего и четвертого элементов И, вход записи устройства подключен к вторым входам третьего и четвертого элементов И, выход третьего элемента И подключен к входу синхронизации триггера, к входу суммирования счетчика адреса записи, к третьему входу второго элемента И и к первому входу элемента ИЛИ, третий вход четвертого элемента И подключен к выходу первого элемента И, выход четвертого элемента И подключен к второму входу элемента ИЛИ, к выходу элемента ИЛИ подключены вход режима накопителя и управляющий вход блока элементов

и-шш.

Элемент 20

а ге

i ,

SffHfteff

3 fMfftff9

Зяенвнт t3

ru

П....Л-.

фие.г

| Буферное запоминающее устройство | 1985 |

|

SU1257704A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1163359A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-07-23—Публикация

1987-12-14—Подача