1чЭ

00 со

(Х

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1983 |

|

SU1176382A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1287236A1 |

| Устройство для сопряжения абонентов с ЭВМ | 1986 |

|

SU1376091A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1658160A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1295451A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1455363A1 |

| Устройство для обмена данными между источником и приемником информации | 1988 |

|

SU1557566A1 |

| Устройство для ввода информации | 1987 |

|

SU1472912A1 |

| Устройство для буферизации информации | 1988 |

|

SU1541624A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1451775A1 |

Изобретение относится к запоминающим устройствам и может быть использовано в качестве буферного запоминающего устройства в системах обработки информации. Цель изобретения - повышение надежности устройства. Буферное запоминающее устройство содержит блок памяти, счетчик адреса записи, счетчик адреса чтения, реверсивный счетчик, первый и второй коммутаторы, триггер, первый и второй элементы ИЛИ, элемент И. Технико-экономические преимущества устройства заключаются в том, что повыщаются его показатели надежности за счет устранения потерь информации при выполнении операции чтения данны.х из буферного запоминающего устройства. Дополнительное к авт. св. № 1176382. 3 ил.

К)

Изобретение относится к запоминаюш.им устройствам, может быть использовано в качестве буферного запоминающего устройства в системах обработки информации, каналах и устройствах обмена и является усовершенствованием устройства по авт. св. № 1176382.

Цель изобретения - повышение надежности устройства.

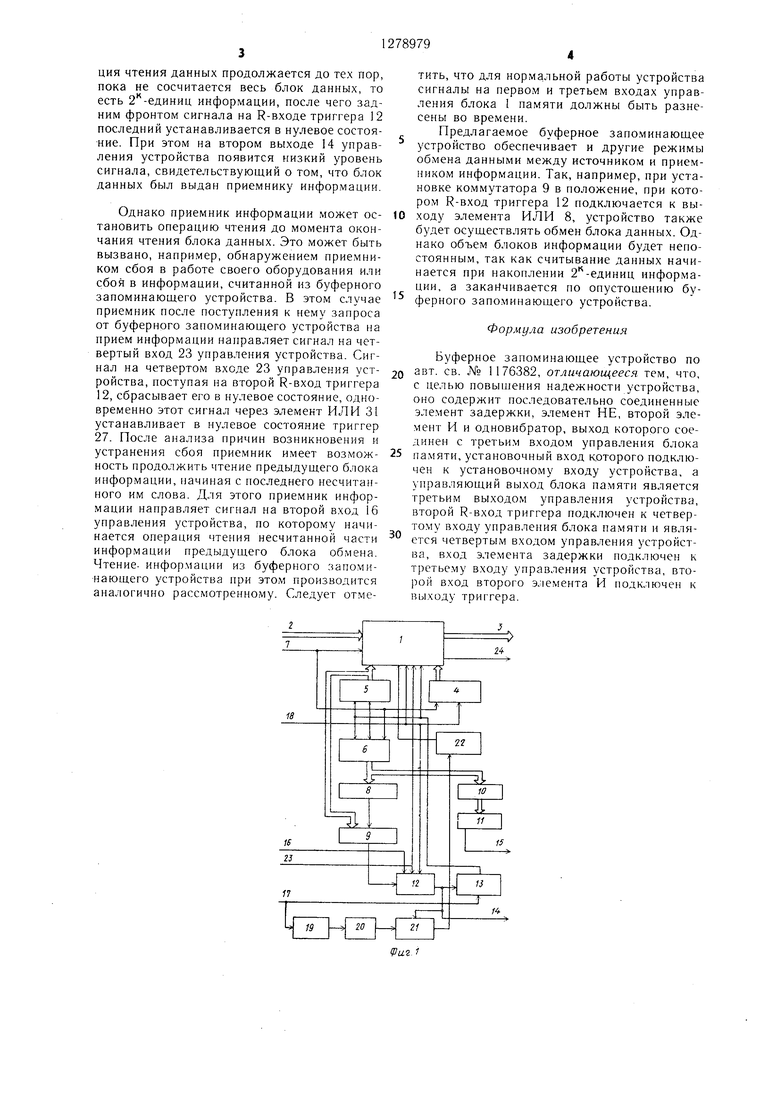

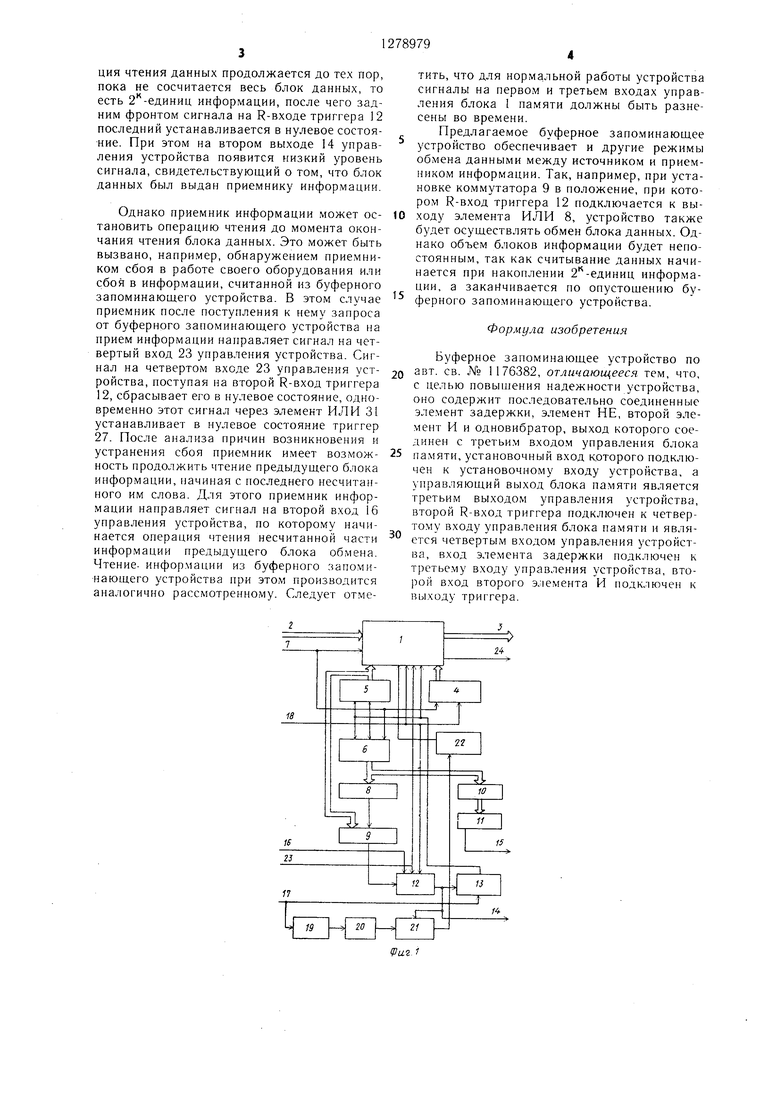

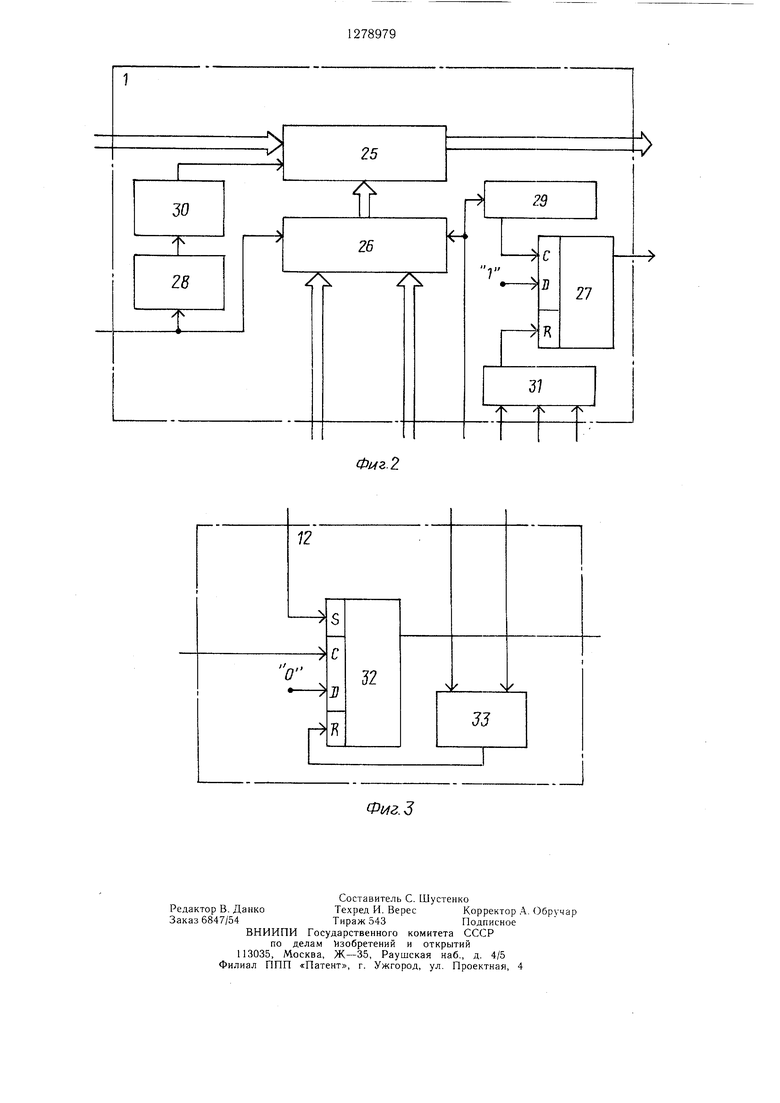

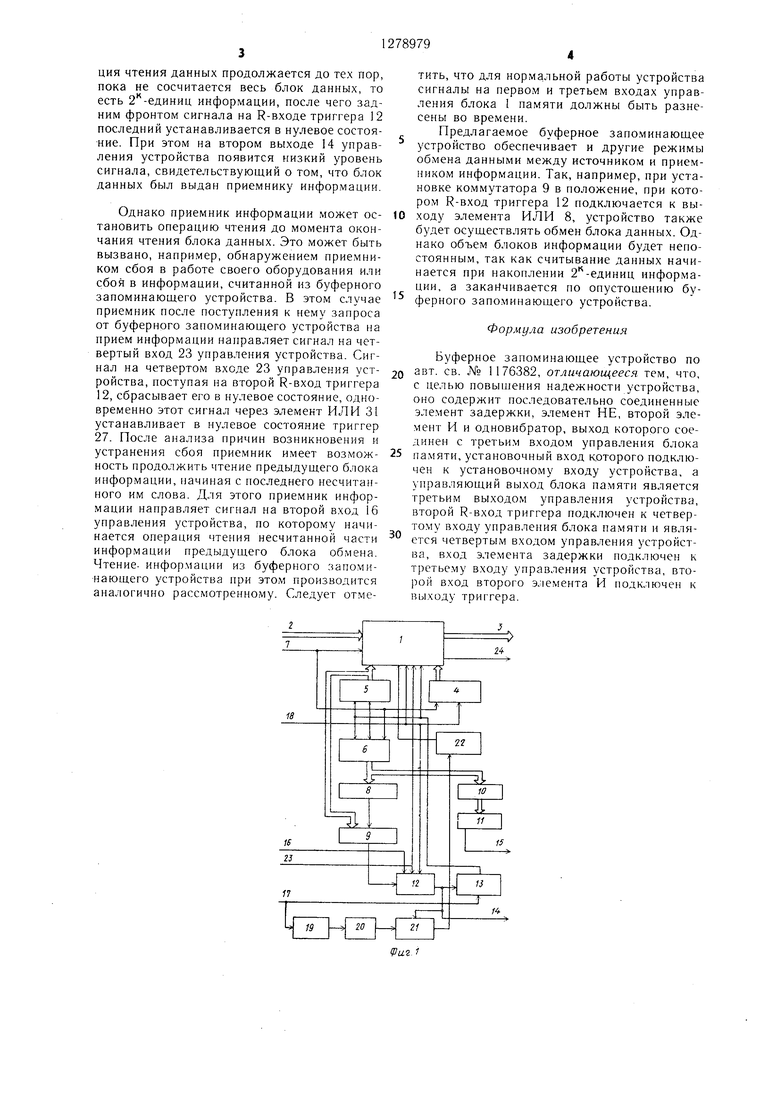

На фиг.1 приведена структурная схема буферного запоминающего устройства; на фиг.2 - структурная схе.ма блока памяти; на фи1.3 - структурная схема триггера.

Буферное запоминающее устройство содержит блок 1 памяти с информационными входами 2 и выходами 3, счетчик 4 адреса записи, счетчик 5 адреса чтения, реверсивьпзЖ счетчик б, первый вход 7 управления, первый элемент ИЛИ 8, первый коммутатор 9, второй коммутатор 10, второй элемент ИЛИ 11, триггер 12, элемент И 13, второй 14 и первый 15 выходы уиранлепия, второй 16 и третий 17 входы управ;|ения, вход 18 начальной установки, элемент 19 задержки, элемент НЕ 20, второй элемент И 21, одновибратор 22, четвертый ВХ0.1 23 управления и третий выход 24 унравления.

Блок 1 иамятн содержит накопитель 25, элементы И-ИЛИ 26, D-триггер 27, элементы 28 и 29 задержки, одновибратор 30 и элемент ИЛИ 31.

Триггер 12 содержит D-триггер 32 и элемент ИЛИ 33.

Устройство работает следующим образом.

Перед началом работы сигнало.м по вхо.;,у 18 начальной установки счетчик 4 адреса записи, счетчик 5 адреса чтения, реверсивный счетчик 6 и триггеры 27 и 32 устанавливаются в нулевые состояния.

Д.1Я организации обмена информацией между источником и приемником в режиме с предварительным накоплением блока данных коммутаторы 9 и 10 устанавливаются в положения, соответствую1цие требуемой величине блока обмепа, а именно: при блоке обмена, равном 2-единиц информации (где К 1,..,, п; п -- разрядность счетчиков 4- 6), коммутатор 9 устанавливается в положение, при котором к первому R-входу триггера 12 подключатся выход К-го раз|)яда счетчика 5 адреса чтепия, а коммутатор И) при этом устанавливается в но.ложение, при котором на входы элемо)гга ИЛИ 1 I подключаются выходы К-|- I,..., п разрядов реверсивного счетчика 6.

При вЬ)Пюлнении операции записи на информационные входы 2 устройства подается информация, нодлежащая записи, в сопровождении импульса записи на нервом входе 7 управления. на первом входе 7 управления устройства,воздействуя на первые входы элеме1-;тов И-ИЛИ 26 и через элемент 28 задержки и одновибратор 30 на вход управления накопителя 25, обеспечит подключепие к адресным входам накопителя 25 выходных сигналов счетчика 4 адреса заниси и запись по этому адресу данных с входных информационных 2 устройства. По заднему фронту сигнала на первом входе 7 улравления устройства производится модификация содержимого счетчика 4 адреса записи и реверсивного счетчика 6, т. е. к их содержимому добавляется единица. Запись последующих информационных носылок осу0 ществляется аналогично.

По наконлению в буферном запоминаюнлем устройстве требуемого блока обмена на выходе элемента ИЛИ 11, т. е. на первом выходе 15 управления устройства, появляется высокий уровень , свидетельствующий о том, что устройство готово к выполнению о 1ерации чтен1 я данных.

При необхо;1имости получения блока данных приемник пнфop ;aции посылает сигнал н.а второй вход 16 управления устройства,

0 который устанавливает тригге) 12 в единичное состояние. При этом на втором выходе 14 управления устройства появляется высокий урове)1Ь сигнала, сви;..ете.1ьствуюц1,ий ;) том, что устройство выполняет операцию чтепия блока данных. Следует отметить, ггo в это время устройство способно удовлетворять и запросы на запись данньгк. Одновременно с этим по nepe uieMy 4рочт сигна.па на выходе триггера 12 через открытый второй элемент И 21 одновибратор 22 формирует сигнал, который воздействует на вторые входы элементов И-ИЛИ 26 и подключает к адресным входам накопите.1я 25 выxoдliыe сигмалы счетчика 5 адрес;) чтения. Осущес-твляется чтение данных из нако.иитсль 25 по адресу, сфор.мированно.му на счегчиле 5 адреса чтения на выходньс im(.inp uuu-io iHbie выходы 3 устройства. По перед:1ему фпонт сигнала на выходе однозибр что)а 22, задержанного на элементе 29 за.держки, усганавливается в единичное состояние триггер 27, выходной сигнал которого псктупает на треО тий выход 24 управления устройства и является запросом к прием) инфс)р.;ации на выдачу данных.

Приемник информации, сч ггьц;ая данные с выходных информа 1ио1П1Ых входов 3 устройства, нос1.1лает сигнал подтвержде.иия приема на третий вход 17 управления устройства, который проходит через открытый элемент И 13 и модифицирует содержимое счетчика 5 адреса чтения (добав.ЯСТся еди;ница) и содержимое реверсивного счетчика 6

Q (вычитается единица) и через элемент ИЛИ 31 сбрасывает в нулевое состояние трип ер 27. После сброса сигнала на третьем входе 17 управления устройства через интервал времени, определяемый величиной задержки элемента 19 задержки, на выходе формиро5 вателя 22 снова появится сигнал, который воздействует на третий вход управления блока 1 памяти и обеспечивает чтение .яанных из еледующей ячейки накопите; я 25. Опеоация чтения данных продолжается до тех пор, пока не сосчитается весь блок данных, то есть 2 -единиц информации, после чего задним фронтом сигнала на R-входе триггера 12 последний устанавливается в нулевое состояние. При этом на втором выходе 14 управления устройства появится низкий уровень сигнала, свидетельствующий о том, что блок данных был выдан приемнику информации.

Однако приемник информации может остановить операцию чтения до момента окончания чтения блока данных. Это может быть вызвано, например, обнаружением приемником сбоя в работе своего оборудования или сбоя в информации, считанной из буферного запоминающего устройства. В этом случае приемник после поступления к нему запроса от буферного запоминающего устройства на прием информации направляет сигнал на четвертый вход 23 управления устройства. Сигнал на четвертом входе 23 управления устройства, поступая на второй R-вход триггера 12, сбрасывает его в нулевое состояние, одновременно этот сигнал через элемент ИЛИ 31 устанавливает в нулевое состояние триггер 27. После анализа причин возникновения и устранения сбоя приемник имеет возможность продолжить чтение предыдущего блока информации, начиная с последнего несчитанного им слова. Для этого приемник информации направляет сигнал на второй вход 16 управления устройства, по которому начинается операция чтения несчитанной части информации предыдущего блока обмена. Чтение, информации из буферного запоминающего устройства при этом производится аналогично рассмотренному. Следует отметить, что для нормальной работы устройства сигналы на первом и третьем входах управления блока 1 памяти должны быть разнесены во времени.

Предлагаемое буферное запоминающее устройство обеспечивает и другие режимы обмена данными между источником и приемником информации. Так, например, при установке коммутатора 9 в положение, при котором R-вход триггера 12 подключается к выходу элемента ИЛИ 8, устройство также будет осуществлять обмен блока данных. Однако объем блоков информации будет непостоянным, так как считывание данных начинается при накоплении 2 -единиц информации, а заканчивается по опустощению буферного запоминающего устройства.

Формула изобретения

Буферное запоминающее устройство по 0 авт. св. № 1176382, отличающееся тем, что, с целью повыщения надежности устройства, оно содержит последовательно соединенные элемент задержки, элемент НЕ, второй элемент И и одновибратор, выход которого соединен с третьим входом управления блока памяти, установочный вход которого подключен к установочному входу устройства, а управляющий выход блока памяти является третьим выходом управления устройства, второй R-вход триггера подключен к четвертому входу управления блока памяти и является четвертым входом управления устройства, вход элемента задержки подключен к третье.му входу управления устройства, второй вход второго элемента И подключен к выходу триггера.

Фиг.2

Фиг.З

| Буферное запоминающее устройство | 1983 |

|

SU1176382A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1986-12-23—Публикация

1985-02-04—Подача