со 00

01

со

Изобретение относится к вычислительной технике и может быть использовано в системах накопления и передачи информации.

Цель изобретения - расширение области применения.

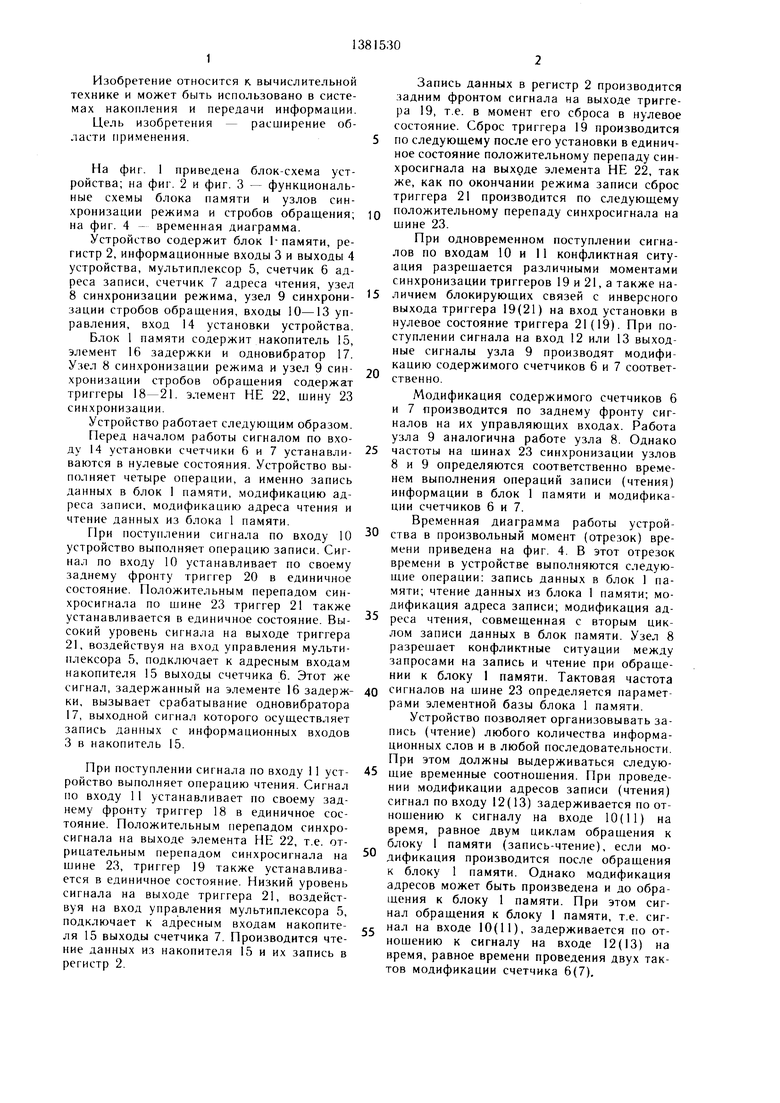

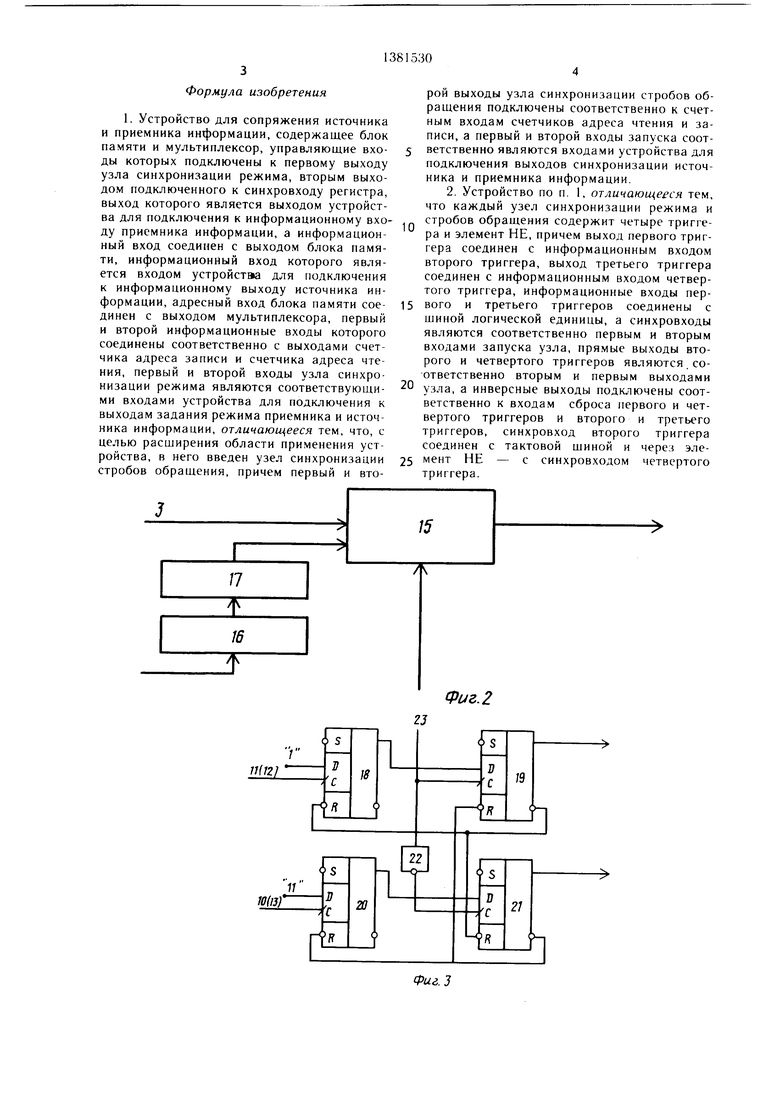

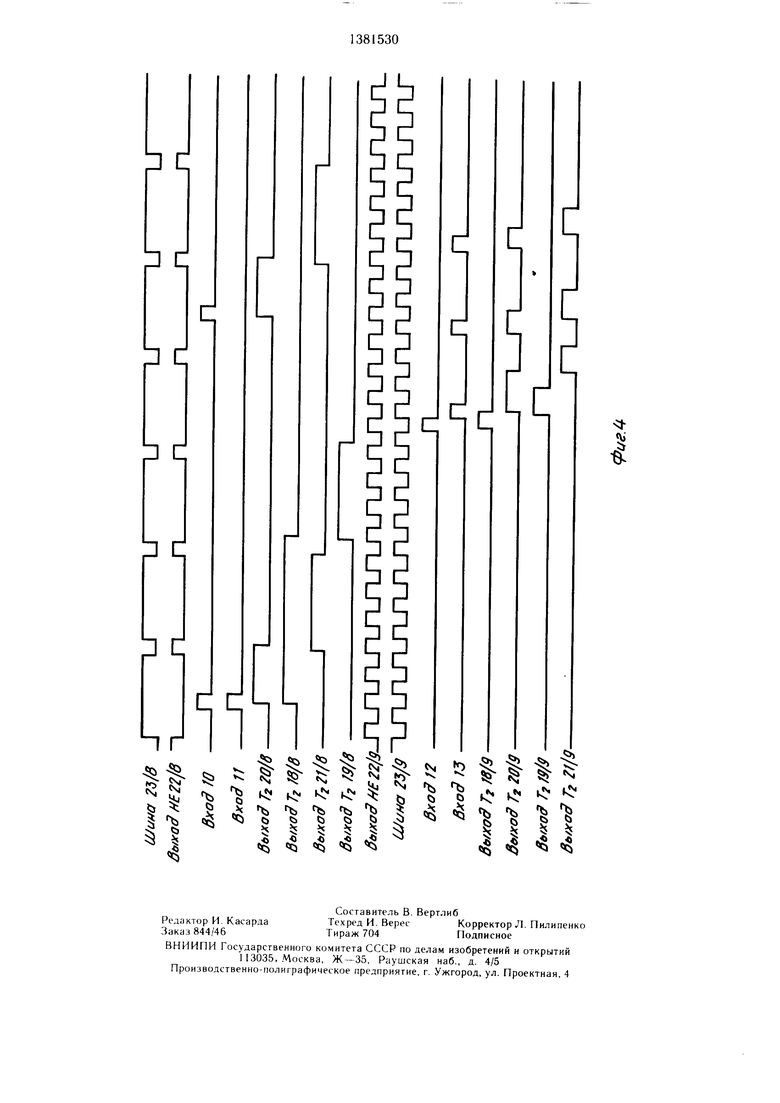

На фиг. 1 приведена блок-схема устройства; на фиг. 2 и фиг. 3 - функциональные схемы блока памяти и узлов синхронизации режима и стробов обращения; на фиг. 4 - временная диаграмма.

Устройство содержит блок 1-памяти, регистр 2, информационные входы 3 и выходы 4 устройства, мультиплексор 5, счетчик 6 адреса записи, счетчик 7 адреса чтения, узел 8 синхронизации режима, узел 9 синхронизации стробов обращения, входы 10-13 управления, вход 14 установки устройства.

Блок 1 памяти содержит накопитель 15, элемент 16 задержки и одновибратор 17. Узел 8 синхронизации режима и узел 9 синхронизации стробов обращения содержат триггеры 18-21. элемент НЕ 22, шину 23 синхронизации.

Устройство работает следующим образом.

Перед началом работы сигналом по входу 14 установки счетчики 6 и 7 устанавливаются в нулевые состояния. Устройство выполняет четыре операции, а именно запись данных в блок 1 памяти, модификацию адреса записи, модификацию адреса чтения и чтение данных из блока 1 памяти.

При поступлении сигнала по входу 10 устройство выполняет операцию записи. Сигнал по входу 10 устанавливает по своему заднему фронту триггер 20 в единичное состояние. Положительным перепадом синхросигнала по щине 23 триггер 21 также устанавливается в единичное состояние. Высокий уровень сигнала на выходе триггера 21, воздействуя на вход управления мультиплексора 5, подключает к адресным входам накопителя 15 выходы счетчика 6. Этот же сигнал, задержанный на элементе 16 задержки, вызывает срабатывание одновибратора 17, выходной сигнал которого осуществляет запись данных с информационных входов 3 в накопитель 15.

При поступлении сигнала по входу 11 устройство выполняет операцию чтения. Сигнал по входу 11 устанавливает по своему заднему фронту триггер 18 в единичное состояние. Положительным переп адом синхросигнала на выходе элемента НЕ 22, т.е. отрицательным перепадом синхросигнала на шине 23, триггер 19 также устанавливается в единичное состояние. Низкий уровень сигнала на выходе триггера 21, воздействуя на вход управления мультиплексора 5, подключает к адресным входам накопителя 15 выходы счетчика 7. Производится чтение данных из накопителя 15 и их запись в регистр 2.

Запись данных в регистр 2 производится задним фронтом сигнала на выходе триггера 19, т.е. в момент его сброса в нулевое состояние. Сброс триггера 19 производится

по следующему после его установки в единичное состояние положительному перепаду синхросигнала на выходе элемента НЕ 22, так же, как по окончании режима записи сброс триггера 21 производится по следующему

положительному перепаду синхросигнала на шине 23.

При одновременном поступлении сигналов по входам 10 и II конфликтная ситуация разрешается различными моментами синхронизации триггеров 19 и 21, а также наличием блокирующих связей с инверсного выхода триггера 19(21) на вход установки в нулевое состояние триггера 21(19). При поступлении сигнала на вход 12 или 13 выходные сигналы узла 9 производят модификацию содержимого счетчиков 6 и 7 соответственно.

Модификация содержимого счетчиков 6 и 7 производится по заднему фронту сигналов на их управляющих входах. Работа узла 9 аналогична работе узла 8. Однако

частоты на шинах 23 синхронизации узлов 8 и 9 определяются соответственно временем выполнения операций записи (чтения) информации в блок 1 памяти и модификации счетчиков 6 и 7.

Временная диаграмма работы устройства в произвольный момент (отрезок) времени приведена на фиг. 4. В этот отрезок времени в устройстве выполняются следующие операции: запись данных в блок 1 памяти; чтение данных из блока 1 памяти; модификация адреса записи; модификация адреса чтения, совмещенная с вторым циклом записи данных в блок памяти. Узел 8 разрешает конфликтные ситуации между запросами на запись и чтение при обращении к блоку I памяти. Тактовая частота

сигналов на шине 23 определяется параметрами элементной базы блока 1 памяти.

Устройство позволяет организовывать запись (чтение) любого количества информационных слов и в любой последовательности. При этом должны выдерживаться следующие временные соотношения. При проведении модификации адресов записи (чтения) сигнал по входу 12(13) задерживается по отношению к сигналу на входе 10(11) на время, равное двум циклам обращения к блоку 1 памяти (запись-чтение), если модификация производится после обращения к блоку 1 памяти. Однако модификация адресов может быть произведена и до обращения к блоку 1 памяти. При этом сигнал обращения к блоку 1 памяти, т.е. сигнал на входе 10(11), задерживается по отношению к сигналу на входе 12(13) на время, равное времени проведения двух тактов модификации счетчика 6(7),

Формула изобретения

1. Устройство для сопряжения источника и приемника информации, содержащее блок памяти и мультиплексор, управляющие входы которых подключены к первому выходу узла синхронизации режима, вторым выходом подключенного к синхровходу регистра, выход которого является выходом устройства для подключения к информационному входу приемника информации, а информационный вход соединен с выходом блока памяти, информационный вход которого является входом устройства для подключения к информационному выходу источника информации, адресный вход блока памяти соединен с выходом мультиплексора, первый и второй информационные входы которого соединены соответственно с выходами счетчика адреса записи и счетчика адреса чтения, первый и второй входы узла синхронизации режима являются соответствующими входами устройства для подключения к выходам задания режима приемника и источника информации, отличающееся тем, что, с целью расширения области применения устройства, в него введен узел синхронизации стробов обращения, причем первый и второй выходы узла синхронизации стробов обращения подключены соответственно к счетным входам счетчиков адреса чтения и записи, а первый и второй входы запуска соответственно являются входами устройства для подключения выходов синхронизации источника и приемника информации.

2. Устройство по п. 1, отличающееся тем, что каждый узел синхронизации режима и стробов обращения содержит четыре триггера и элемент НЕ, причем выход первого триггера соединен с информационным входом второго триггера, выход третьего триггера соединен с информационным входом четвертого триггера, информационные входы пер5 вого и третьего триггеров соединены с шиной логической единицы, а синхровходы являются соответственно первым и вторым входами запуска узла, прямые выходы второго и четвертого триггеров являются, соответственно вторым и первым выходами

0 узла, а инверсные выходы подютючены соответственно к входам сброса первого и четвертого триггеров и второго и третьего триггеров, синхровход второго триггера соединен с тактовой щиной и через эле5 мент НЕ - с синхровходом четвертого триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1647579A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1416988A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Буферное запоминающее устройство | 1987 |

|

SU1417039A1 |

| Устройство для сопряжения | 1985 |

|

SU1278861A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве устройства для сопряжения в системах накопления и передачи информации. Цель изобретения состоит в расширении области применения устройства за счет обеспечения раздельного выполнения операций записи в блок памяти и модификации адреса записи, а также чтения данных из блока памяти и модификации адреса чтения. Цель достигается тем, что в устройство, содержащее блок 1 памяти, регистр 2, мультиплексор 5, счетчики 6 и 7 адреса записи и чтения и y3evi 8 синхронизации обращения, введен узел 9 синхронизации стробов обращения. Устройство кроме обычных функций записи-чтения осуществляет последовательное многократное выполнение операции записи данных в произвольную ячейку блока 1 памяти, последовательное многократное чтение данных из любой ячейки блока 1 памяти, совмещение по времени выполнения операций записи и модификации адреса чтения, совмещение по времени выполнения операций чтения и модификации адреса записи, выполнение операций записи или чтения данных избирательно по определенным адресам блока памяти. 1 з.п. ф-лы, 4 ил. (Л

/7

10(аГ

11

15

/

Фиг. 2

4я

20

21

4i

Л

| Устройство для сопряжения источника и приемника информации | 1984 |

|

SU1236491A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения с памятью | 1984 |

|

SU1179362A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-15—Публикация

1986-04-03—Подача