fO

20

Изобретение относится к вычислиельной технике и предназначено для бмена информацией между ЭВМ, имеюей общую магистраль с совмещенными инами Адресные, и периферийным стройством.

Целью изобретения является повыение достоверности обмена информацией ,

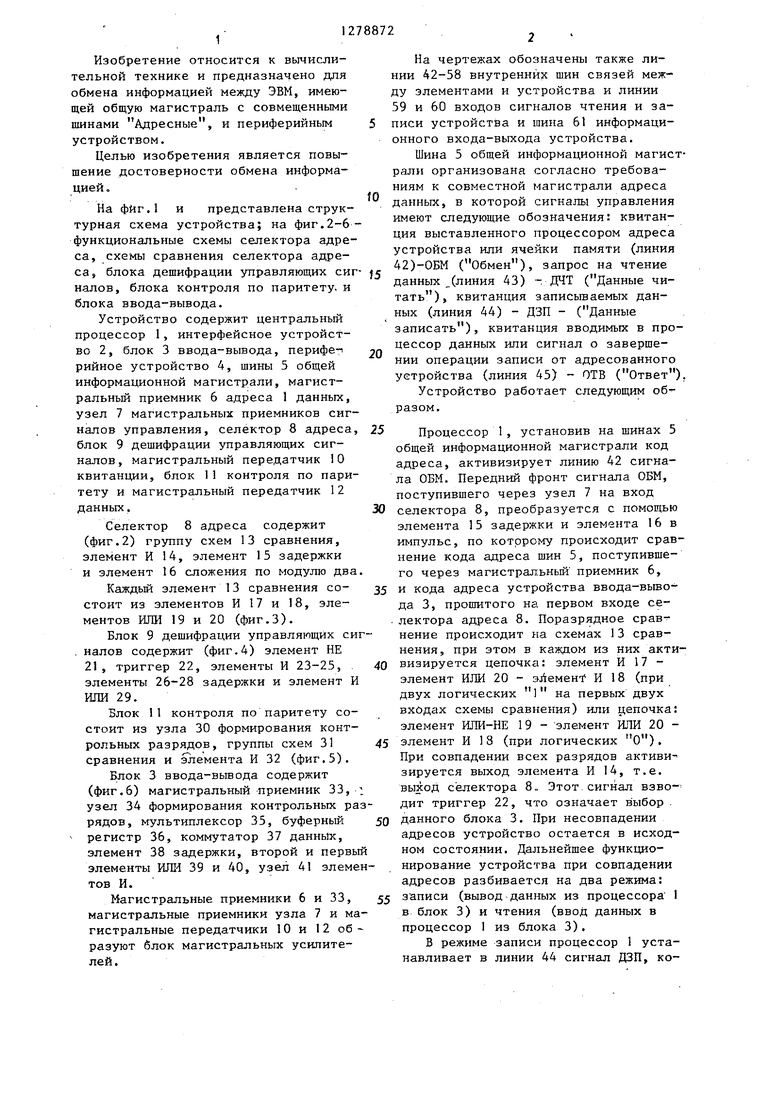

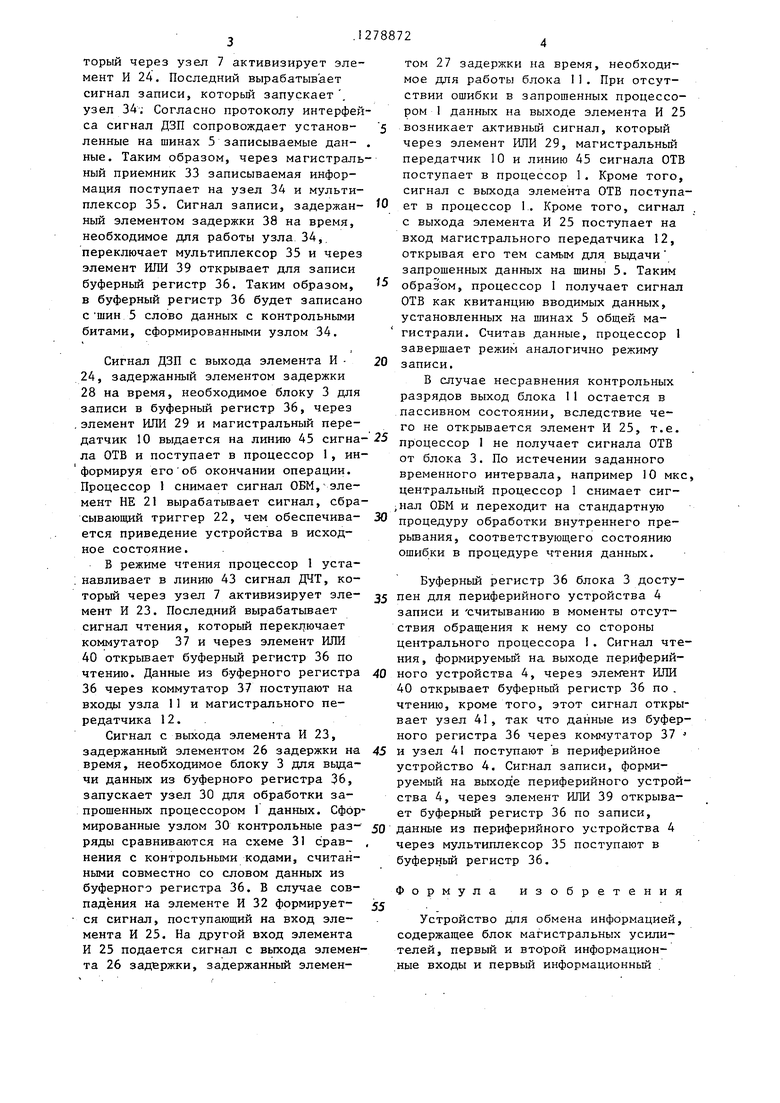

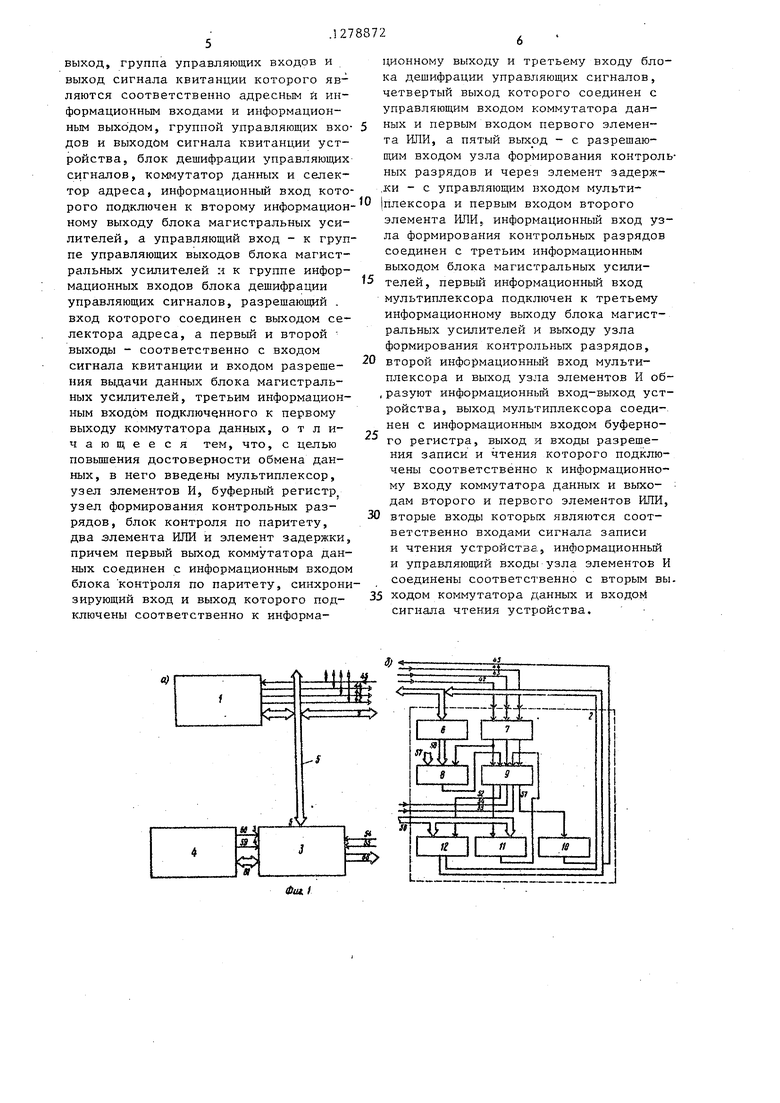

На фйг.1 и представлена структурная схема устройства; на фиг.2-6- функциональные схемы селектора адреса, схемы сравнения селектора адреса , блока дешифрации управляющих сиг- )5 налов, блока контроля по паритету, и блока ввода-вывода.

Устройство содержит центральный процессор 1, интерфейсное устройство 2, блок 3 ввода-вывода, периферийное устройство 4, шины 5 общей информационной магистрали, магистральный приемник 6 адреса 1 данных, узел 7 магистральных приемников сигналов управления, селектор 8 адреса, 25 блок 9 дешифрации управляющих сигналов , магистральный передатчик 0 квитанции, блок 11 контроля по паритету и магистральный передатчик 12 данных.

Селектор 8 адреса содержит (фиг.2) группу схем 13 сравнения, элемент И 14, элемент 15 задержки и элемент 16 сложения по модулю два.

Каждый элемент 13 сравнения состоит из элементов И 17 и 18, элементов ИЛИ 19 и 20 (фиг.З).

Блок 9 дешифрации управляющих сиг налов содержит (фиг.4) элемент НЕ 21, триггер 22, элементы И 23-25, элементы 26-28 задержки и элемент И ИЛИ 29.

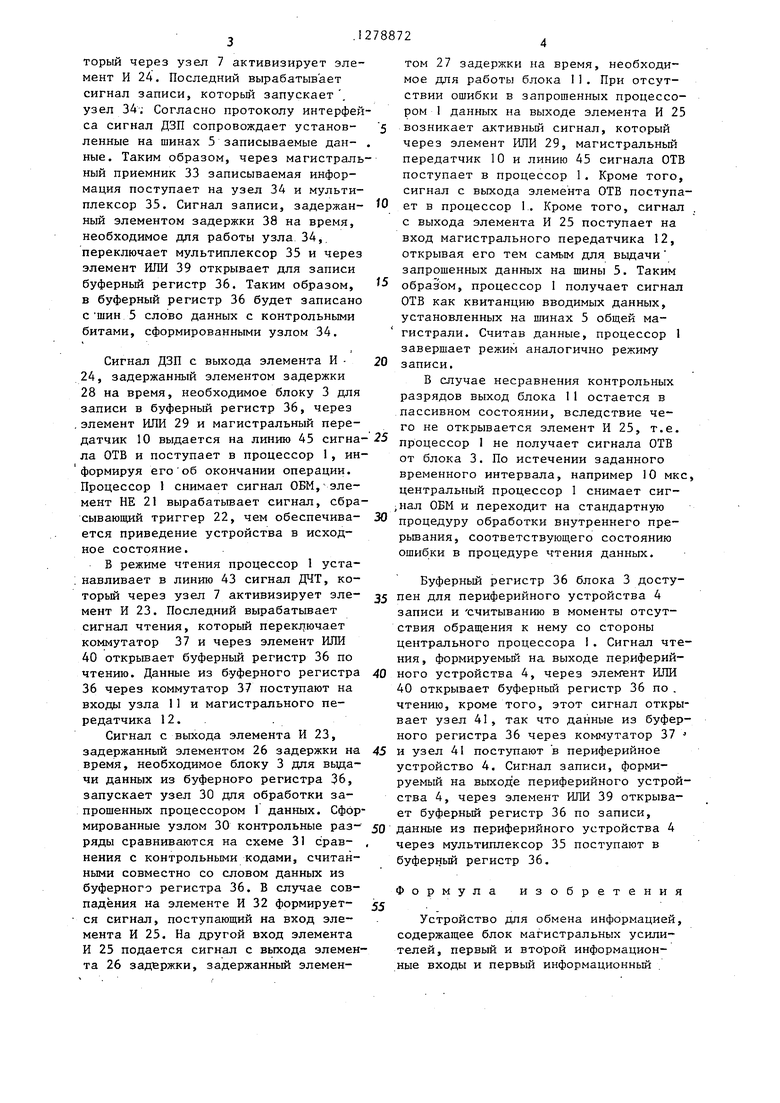

Блок 11 контроля по паритету состоит из узла 30 формирования контрольных разрядов, группы схем 31 сравнения и элемента И 32 (фиг.5).

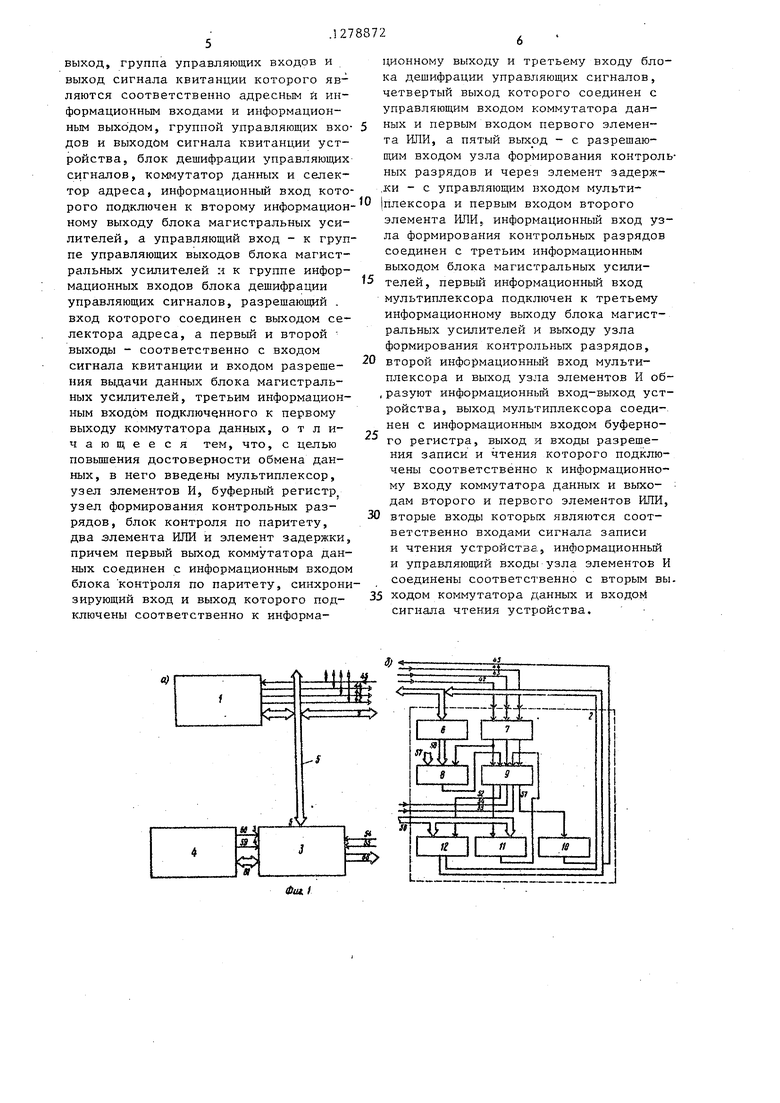

Блок 3 ввода-вьгоода содержит (фиг.6) магистральный приемник 33, : узел 34 формирования контрольных разрядов, мультиплексор 35, буферный 50 регистр 36, коммутатор 37 данных, элемент 38 задержки, второй и первый элементы ИЛИ 39 и 40, узел 41 элементов И.

МагистрсШьные приемники 6 и 33, магистральные приемники узла 7 и магистральные передатчики 10 и 12 об разуют ёлок магистральных усилителей .

30

35

40

45

55

На чертежах обозначены также линии 42-58 внутренних шин связей между элементами и устройства и линии 59 и 60 входов сигналов чтения и записи устройства и шина 61 информационного входа-выхода устройства.

Шина 5 общей информационной магистрали организована согласно требованиям к совместной магистрали адреса данных, в которой сигналы управления имеют следующие обозначения: квитанция выставленного процессором адреса устройства или ячейки памяти (линия 42)-ОБМ (Обмен), запрос на чтение данных (линия 43) - ДЧТ (Данные читать), квитанция записьшаемых данных (линия 44) - ДЗП - (Данные записать), квитанция вводимых в процессор данных ипи сигнал о завершении операции записи от адресованного устройства (линия 45) - ОТВ (Ответ).

Устройство работает следующим образом.

Процессор 1, установив на шинах 5 общей информационной магистрали код адреса, активизирует линию 42 сигнала ОБМ. Передний фронт сигнала ОБМ, поступившего через узел 7 на вход

селектора 8, преобразуется с помощью элемента 15 задержки и элемента 16 в импульс, по которому происходит сравнение кода адреса шин 5, поступившего через магистральньм приемник 6,

и кода адреса устройства ввода-вывода 3, прошитого на первом входе се- лектора адреса 8. Поразрядное срав- нение происходит на схемах 13 сравнения, при этом в каждом из них активизируется цепочка: элемент И 17 - элемент ИЛИ 20 - эЛемент И 18 (при двух логических l на первых двух входах схемы сравнения) или цепочка: элемент ИЛИ-НЕ 19 - элемент ИЛИ 20 элемент И 18 (при логических О), При совпадении всех разрядов активи зируется выход элемента И 14, т.е. выход селектора 8,. Этот, сигнал взво- дит триггер 22, что означает выбор . данного блока 3. При несовпадении адресов устройство остается в исходном состоянии. Дальнейшее функционирование устройства при совпадении адресов разбивается на два режима: записи (вывод данных из процессора 1 в блок 3) и чтения (ввод данных в процессор 1 из блока 3).

В режиме записи процессор 1 устанавливает в линии 44 сигнал ДЗП, ко

торый через узел 7 активизирует элемент И 24. Последний вырабатывает сигнал записи, который запускает . узел 34; Согласно протоколу интерфейса сигнал ДЗП сопровождает установленные на шинах 5 записываемые дан- . ные. Таким образом, через магистральный приемник 33 записываемая информация поступает на узел 34 и мультиплексор 35. Сигнал записи, задержанный элементом задержки 38 на время, необходимое для работы узла 34,. переключает мультиплексор 35 и через элемент ИЛИ 39 открывает для записи буферньш регистр 36. Таким образом, в буферный регистр 36 будет записано с ШИН 5 слово данных с контрольными битами, сформированными узлом 34.

Ю

том 27 задержки на время, необходимое для работы блока I1. При отсутствии ошибки в запрошенных процессором I данных на выходе элемента И 25 возникает активный сигнал, который через элемент ИЛИ 29, магистральный передатчик 10 и линию 45 сигнала ОТВ поступает в процессор 1. Кроме того, сигнал с выхода элемента ОТВ поступает в процессор I. Кроме того, сигнал с выхода элемента И 25 поступает на вход магистрального передатчика 12, открывая его тем самым для выдачи запрошенных данных на шины 5. Таким образ ом, процессор I получает сигнал ОТВ как квитанцию вводимых данных, установленных на шинах 5 общей магистрали. Считав данные, процессор 1 завершает режим аналогично режиму записи.

В случае несравнения контрольных разрядов выход блока 11 остается в пассивном состоянии, вследствие чего не открывается элемент И 25, т.е.

датчик 10 выдается на линию 45 сигна- 25 процессор 1 не получает сигнала ОТВ

15

Сигнал ДЗП с выхода элемента И - 24, задержанный элементом задержки 28 на время, необходимое блоку 3 для записи в буферный регистр 36, через элемент ИЛИ 29 и магистральный пере20

40

ла ОТВ и поступает в процессор 1, ин- формируя его об окончании операции. Процессор 1 снимает сигнал ОБМ, элемент НЕ 21 вырабатьгоает сигнал, сбрасывающий триггер 22, чем обеспечива- 30 ется приведение устройства в исходное состояние.

В режиме чтения процессор 1 уста- ; навливает в линию 43 сигнал ДЧТ, ко- торьй через узел 7 активизирует элемент И 23. Последний вырабатьшает сигнал чтения, который переключает коммутатор 37 и через элемент ИЛИ 40 открывает буферный регистр 36 по чтению. Данные из буферного регистра 36 через коммутатор 37 поступают на входы узла 11 и магистрального передатчика 12. .

Сигнал с выхода элемента И 23, задержанный элементом 26 задержки на время, необходимое блоку 3 для выдачи данных из буферного регистра 36, запускает узел 30 для обработки запрошенных процессором 1 данных. Сформированные узлом 30 контрольные раз- 50 ряды сравниваются на схеме 31 срав- , нения с контрольными кодами, считанными совместно со словом данных из буферного регистра 36. В случае совпадения на элементе И 32 формирует- 55 ся сигнал, поступающий на вход элемента И 25. На другой вход элемента И 25 подается сигнал с вьпсода элемента 26 задержки, задержанный элеменполучает

от блока 3. По истечении заданного временного интервала, например 10 мкс, центральный процессор 1 снимает сигнал ОБМ и переходит на стандартную процедуру обработки внутреннего пре- рьшания, соответствующего состоянию ошибки в процедуре чтения данных.

Буферный регистр 36 блока 3 досту- 35 пен для периферийного устройства 4 записи и считыванию в моменты отсутствия обращения к нему со стороны центрального процессора I. Сигнал чтения , формируемьй на выходе периферийного устройства 4, через элемент ИЛИ 40 открывает буферньш регистр 36 по . чтению, кроме того, этот сигнал открывает узел 41, так что данные из буферного регистра 36 через коммутатор 37 и узел 41 поступают в периферийное устройство 4. Сигнал записи, формируемый на выходе периферийного устройства 4, через элемент ИЛИ 39 открывает буферный регистр 36 по записи, данные из периферийного устройства 4 через мультиплексор 35 поступают в буферный регистр 36.

45

Формула изобретения

Устройство для обмена информацией, содержащее блок магистральных усилителей, первый и вто рой информационные входы и первый информационный

5 процессор 1 не получает сигнала ОТВ

0

30

0 5

получает

от блока 3. По истечении заданного временного интервала, например 10 мкс, центральный процессор 1 снимает сигнал ОБМ и переходит на стандартную процедуру обработки внутреннего пре- рьшания, соответствующего состоянию ошибки в процедуре чтения данных.

Буферный регистр 36 блока 3 досту- 35 пен для периферийного устройства 4 записи и считыванию в моменты отсутствия обращения к нему со стороны центрального процессора I. Сигнал чтения , формируемьй на выходе периферийного устройства 4, через элемент ИЛИ 40 открывает буферньш регистр 36 по . чтению, кроме того, этот сигнал открывает узел 41, так что данные из буферного регистра 36 через коммутатор 37 и узел 41 поступают в периферийное устройство 4. Сигнал записи, формируемый на выходе периферийного устройства 4, через элемент ИЛИ 39 открывает буферный регистр 36 по записи, данные из периферийного устройства 4 через мультиплексор 35 поступают в буферный регистр 36.

5

Формула изобретения

Устройство для обмена информацией, содержащее блок магистральных усилителей, первый и вто рой информационные входы и первый информационный

выход, группа управляющих входов и выход сигнала квитанции которого являются соответственно адресным и информационным входами и информационным выходом, группой управляющих вхо дов и выходим сигнала квитанции устройства, блок дешифрации управляющих сигналов, коммутатор данных и селектор адреса, информационный вход котоционному выходу и третьему входу ка дешифрации управляющих сигнало четвертый выход которого соединен управляющим входом коммутатора да ных и первым входом первого элем та ИЛИ, а пятый выход - с разреш щим входом узла формирования кон ных разрядов и через элемент зад ,ки - с управляющим входом мульти

1 Оу с1Дрсис1, iimijJUpMcliJ.iaunnioui I рого подключен к второму информацион- |плексора и первым входом второго

ному выходу блока магистральных усилителей, а управляющий вход - к группе управляющих выходов блока магистральных усилителей н к группе инфор- мадионных входов блока дешифрации управляющих сигналов, разрешающий . вход которого соединен с выходом селектора адреса, а первый и второй выходы - соответственно с входом сигнала квитанции и входом разрешения выдачи данных блока магистральных усилителей, третьим информационным входом подключенного к первому выходу коммутатора данных, отличающееся тем, что, с целью повьшения достоверности обмена данных, в него введень мультиплексор.

узел элементов И, буферный регистр узел формирования контрольных разрядов, блок контроля по паритету, два элемента ИЛИ и элемент задержки, причем первый выход коммутатора данных соединен с информационным входом блока контроля по паритету, синхронизирующий вход и выход которого подключены соответственно к информаэлемента ИЛИ информационный вхо ла формирования контрольных разр соединен с третьим информационны выходом блока магистральных усип 5 телей, первый информационньш вхо мультиплексора подключен к треть информационному выходу блока маг ральных усилителей и выходу узла формирования контрольньтх разрядо 20 второй информационный вход мульт плексора и выход узла элементов ,разуют информационный вход-выход ройства, выход мультиплексора со нен с информационным входом буфе го регистра, выход и входы разре ния записи и чтения которого под чены соответственно к информацио му входу коммутатора данных и вы дам второго и первого элементов 30 вторые входы которых являются с ветственно входами сигнала запи и чтения устройства, информацио и управляющий входы узла элемен соединены соответственно с втор 35 ходом коммутатора данных и вход сигнала чтения устройства.

25

ционному выходу и третьему входу блока дешифрации управляющих сигналов, четвертый выход которого соединен с управляющим входом коммутатора данных и первым входом первого элемента ИЛИ, а пятый выход - с разрешающим входом узла формирования контролных разрядов и через элемент задерж- ,ки - с управляющим входом мульти |плексора и первым входом второго

элемента ИЛИ информационный вход узла формирования контрольных разрядов соединен с третьим информационным выходом блока магистральных усипи- 5 телей, первый информационньш вход мультиплексора подключен к третьему информационному выходу блока магистральных усилителей и выходу узла формирования контрольньтх разрядов, 20 второй информационный вход мультиплексора и выход узла элементов И об- ,разуют информационный вход-выход устройства, выход мультиплексора соеди-, нен с информационным входом буферного регистра, выход и входы разрешения записи и чтения которого подключены соответственно к информационному входу коммутатора данных и выхо- дам второго и первого элементов ИЛИ, 30 вторые входы которых являются соответственно входами сигнала записи и чтения устройства, информационный и управляющий входы узла элементов И соединены соответственно с вторым вы 35 ходом коммутатора данных и входом сигнала чтения устройства.

25

51 58 46

.2

Фиг,. 5

sasas ss

Составитель В.Вертлиб Редактор В.Иванова Техред л.Олейник . Корректор М.Пожо

Заказ 6840/48 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

6J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией | 1988 |

|

SU1536395A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1985 |

|

SU1288709A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Сетевой контроллер | 1988 |

|

SU1564641A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Многоканальное микропрограммное устройство ввода-вывода | 1983 |

|

SU1104500A1 |

| Устройство для сопряжения внешних устройств с электронной вычислительной машиной | 1983 |

|

SU1100615A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1987 |

|

SU1587521A1 |

Изобретение относится к области вычислительной техники и предназначено для обмена информацией между ЭВМ, имеющей общую магистраль с совмещенными шинами Ад- :рес / Данные, и периферийным устройством. Цепью изобретения является повышение достоверности обмена информацией. Цель достигается тем, что в устройство, содержащее блок магистральных усилителей, блок дешифрации управляющих сигналов, селектор адреса и коммутатор данных, введены блок контроля по паритету, узел формирования контрольных разрядов, мультиплексор, узел элементов - И, буферный регистр, два элемента ШШ и элемент задержки. 6 ил. tsD 00 00 ю

| Устройство для сопряжения периферийной системы с электронной вычислительной машиной | 1975 |

|

SU554534A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения ЭВМ с магистралью ввода-вывода периферийных устройств | 1983 |

|

SU1160426A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-23—Публикация

1985-05-29—Подача