Изобретение относится к вычислительной технике и может быть использовано в постоянных запоминающих устройствах с перезаписью информации (ППЗУ).

Цель изобретения - уменьшение потребляемой мощности ППЗУ.

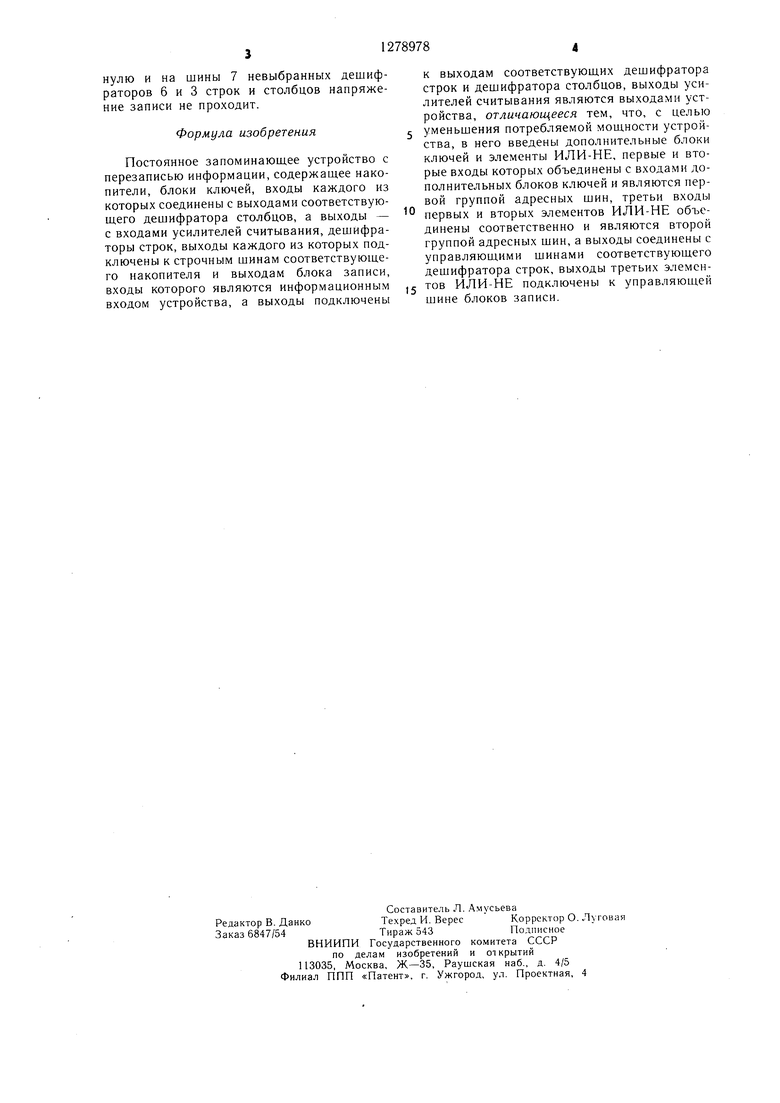

На чертеже изображена функциональная схема ППЗУ.

ППЗУ содержит накопители 1, блоки 2 столбцовых ключей, дешифраторы 3 столбцов и разрядные п;ины 4 и 5, дешифраторы 6 строк, строчные шины 7, входные шины 8 и 9 деишфратора строк и дешифратора столбцов, усилители записи/считывания 10, выходные шины 11 устройства, блоки 12 записи, шину 13 записи, дополнительные блоки 14 ключей, выходы 15 которых соединены с входами блоков 2, первую группу адресных шин 16, элементы ИЛИ-НЬг 17- - 19, управляющую шину 20 блоков 12 записи.

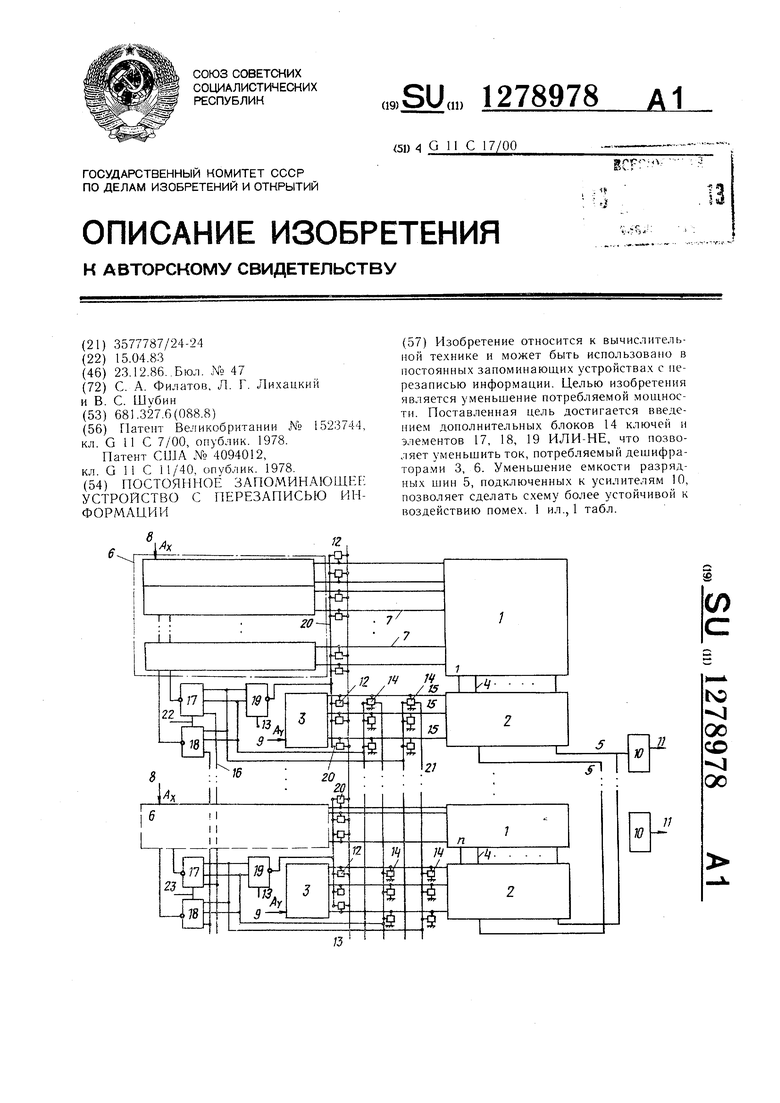

0- Дешифратор отключен

Выбирается одна из строчных шнн 7 в зависимости от кода адреса на входных шинах 8

1- выходы в третьем состоярии

В режиме считывания на адресные шины 16 поступает высокий и низкий уровень напряжения в соответствии с кодом адреса. Блок 14 отключается, если на его входных шинах 16 потенциал низкого уровня, и дешифратор 3 столбцом разряжает все 15, кроме одной, в соответствии с адресами 8. Разрядные 5 подключены через блоки 2 к разрядным типам 4 выбранного накопителя 1. Остальные блоки 14 ключей поддерживают потенциал низкого уровня на шинах 15, и блоки 2 ключей закрыты.

На одну из шин 21 поступает логическая единица, а на другую - логический нуль. С выходов элементов ИЛИ-НЕ 17 и 18, юдеоединенных к шинам 16 с потенциалом низкого уровня,поступает инвертированный сигнал по отноп ению к логическим уровня на шинах 21.

Таким образом, па управляющие шины 22 и 23 дешифратора 6 строк, относящегося к выбранному накопителю, поступает логическая единица (например, по шине 22) и логический нуль (щина 23). Ден-Шфратором 6 строк, в соответствии с кодом на шипах 8, заряжается одна выбранная строка 7.

вторую группу адресных шин 21 (прямых и инверсных), управляющие шины 22 и 23.

Устройство работает следующи.м образо.м.

В невыбранном )ежиме (режиме хранения) на шины 16 поступает потенциал логической единицы, на прямую и дополнительную к пей П1ИНЫ 21 кода младшего разряда адреса 21, образующие первую группу адресных шин, подают потенциал логического нуля (или логической единицы), на шину 13 записи в режиме считывания и хранения поступает потенциал, уровень которого ниже напряжения, необходимого для записи информации, и по крайней мере равный напряжению питания устройства.

На шинах 15, 20, 22 и 23 устанавливается низкий уровень напряжения, в результате блоки 12 отключены от шины 13. Состояния выходов дешифратора 6 в зависимости от уровня потенциала на управляюших шинах 22 и 23 приведены Е; таблице.

5

0

5

Так как входы остальных элементов ИЛИ-НЕ 4 и 15 соединены хотя бы с одной из 1ПИН 16, па которой уровень логической единицы, на выходах этих элементов логические нули, и на строчных пжнах 7 соот- ветствуюплих дешифраторов остается потенциал, близкий по уровню к потенциалу строк в режиме хранения.

Таким образом, происходит считывание информации, хранимой элементами памяти, находящимися на нересечепии выбранной шины 7 выбранного накопите.мя 1 и разрядных тин 4, соединенных через блоки 2 ключей с разрядными шипами 5 и подключенных к усилителям 10.

В режиме записи устройство работает аналогичным образом, отличие только в том, что на шину 13 записи поступает высокое 11рограммирую1цее напряжение. При этом на выход 20 третьего элемента ИЛИ-НЕ 19 выбранного накопителя 1 от шины 13 записи поступает программирующее напряжение, и через блоки 12 записи на выбранную шину 7 поступает напряжение записи. На шинах 20 всех остальных элементов ИЛИ-НЕ 19 уровень потенциала соответствует логическому

нулю и на шины 7 невыбранных дешифраторов 6 и 3 строк и столбцов напряжение записи не проходит.

Формула изобретения

Постоянное запоминающее устройство с перезаписью информации, содержащее накопители, блоки ключей, входы каждого из которых соединены с выходами соответствующего дешифратора столбцов, а выходы - с входами усилителей считывания, дешифраторы строк, выходы каждого из которых подключены к строчным шинам соответствующего накопителя и выходам блока записи, входы которого являются информационным входом устройства, а выходы подключены

к выходам соответствующих дешифратора строк и дешифратора столбцов, выходы усилителей считывания являются выходами устройства, отличающееся тем, что, с целью

уменьшения потребляемой мощности устройства, в него введены дополнительные блоки ключей и элементы ИЛИ-НЕ, первые и вторые входы которых объединены с входами дополнительных блоков ключей и являются первой группой адресных шин, третьи входы

первых и вторых элементов ИЛИ-НЕ объединены соответственно и являются второй группой адресных шин, а выходы соединены с управляющими шинами соответствуюшего дешифратора строк, выходы третьих элементов ИЛИ-НЕ подключены к управляющей шине блоков записи.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1986 |

|

SU1483493A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Полупроводниковое запоминающее устройство | 1988 |

|

SU1674261A1 |

| Постоянное запоминающее устройство на элементах памяти с 2 @ логическими состояниями | 1983 |

|

SU1552228A1 |

| Накопитель для оперативного запоминающего устройства | 1986 |

|

SU1376118A1 |

| Резервированное запоминающее устройство с самоконтролем | 1982 |

|

SU1070609A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1978 |

|

SU769628A1 |

| Устройство записи и считывания информации для динамического накопителя на однотранзисторных запоминающих элементах | 1976 |

|

SU727023A1 |

| ПОЛУПРОВОДНИКОВАЯ ПАМЯТЬ | 1993 |

|

RU2156506C2 |

| Оперативное запоминающее устройство | 1982 |

|

SU1111204A1 |

Изобретение относится к вычислительной технике и может быть использовано в постоянных запоминающих устройства.ч с перезаписью информации. Целью изобретения является уменьшение потребляемой мощности. Поставленная цель достигается введением дополнительных блоков 14 ключей и элементов 17, 18, 19 ИЛИ-НЕ, что позволяет уменьшить ток, потребляемый дешифраторами 3, 6. Уменьшение емкости разрядных шин 5, подключенных к усилителям 10, позволяет сделать схему более устойчивой к воздействию помех. 1 ил., 1 табл. ГС 00 со 00

| Волновой обменник давления | 1987 |

|

SU1523744A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Патент США № 4094012, кл G 11 С 11/40, опублик | |||

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

Авторы

Даты

1986-12-23—Публикация

1983-04-15—Подача