1280390

памяти коэффициентов, сумматора 251 J4-I6, сумматора 13, регистра J

по модулю два, элемента 24 НЕ, четы-результата, блока 8 синхронизации,

рех элементов 17-20 И, двух мульти-блока 23 предварительного округлеплексоров 10,11, четырех регистровния, 1 з.п, ф-лы, 3 ил.

.1

Изобретение относится к цифровой обработке сигналов и может быть использовано для вычисления сумм произведений, дискретного преобразования- Фурье, обработки речи и изобра- жений в реальном времени.

Цель изобретения - повышение быстродействия устройства.

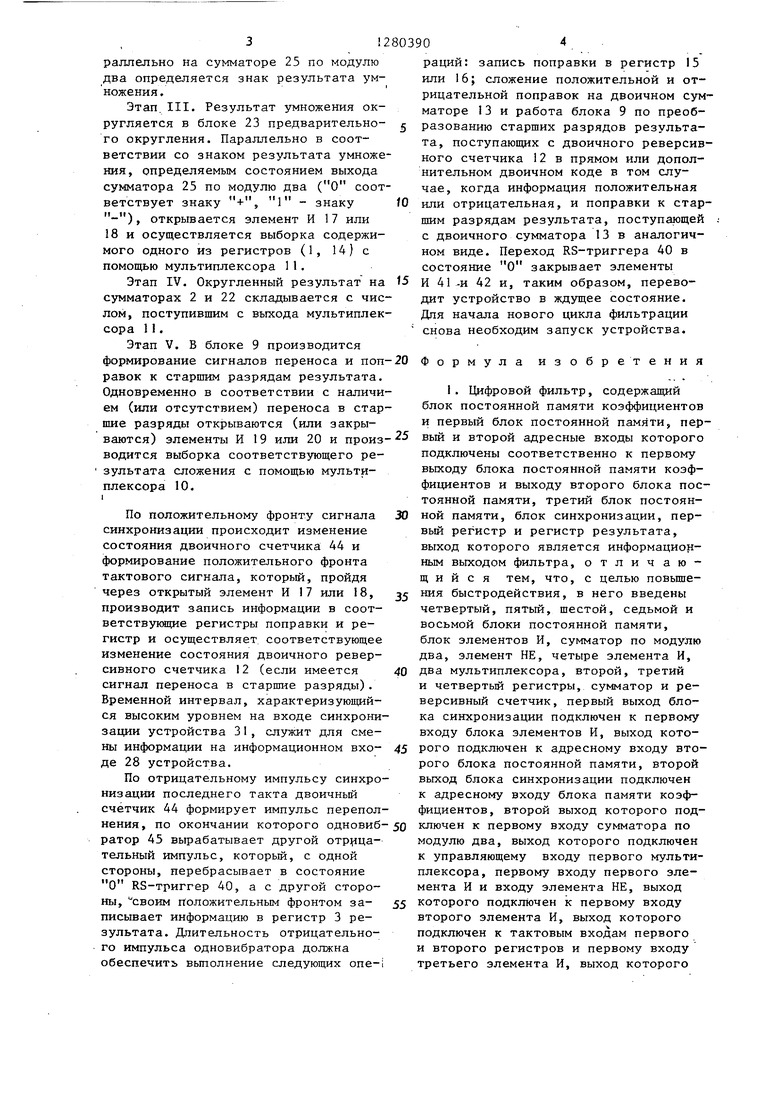

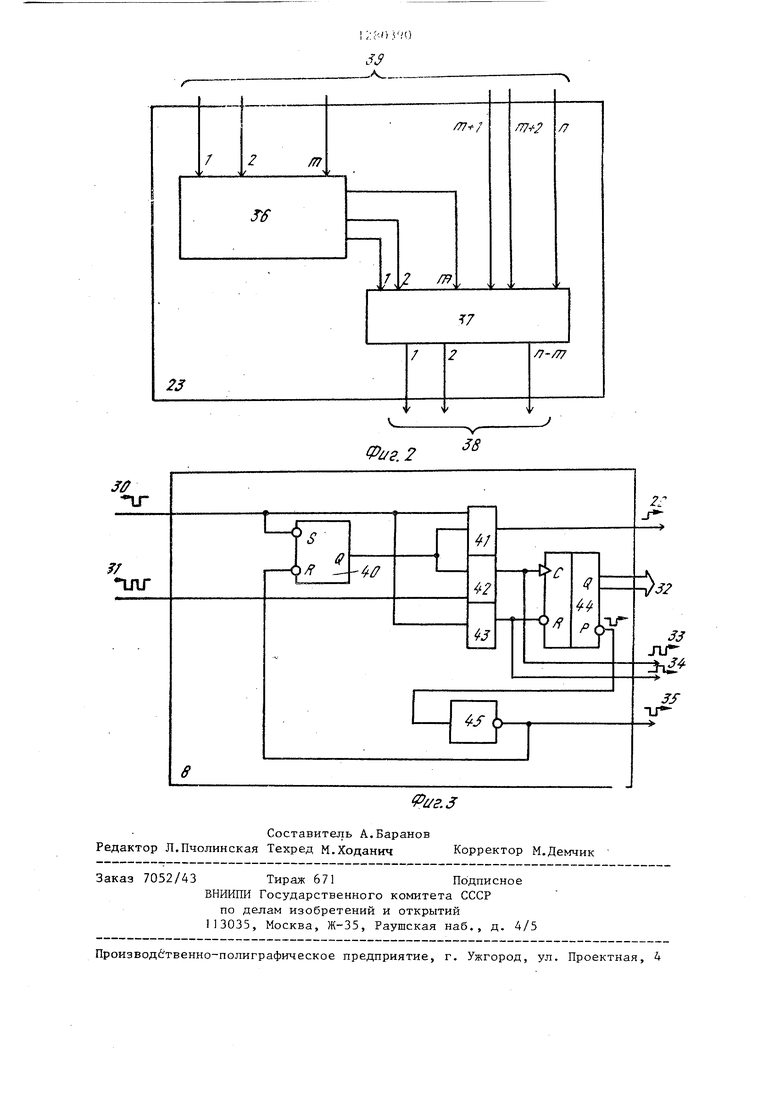

На фиг.1 представлена структурная схема цифрового фильтра; на фиг.2 - блок-схема блока предварительного округления; на фиг.3 - блок управления.

Цифровой фильтр содержит регистр 1, блок 2 постоянной памяти, ре- гистр 3 результата, информационный выход 4 устройства, блок 5 постоянной памяти, блок 6 постоянной памяти коэффициентов, блок 7 постоянной памяти, блок 8 синхронизации, блок 9 постоянной памяти, мультиплексоры 10 и 1, двоичный реверсивный счетчик 12, двоичный сумматор 13, регистры 14-16, элементы И 17-20, блоки 21 и

22постоянной памяти, блок 23 предварительного округления, элемент

НЕ 24, сумматор 25 по модулю два, вход 26 знака информации устройства, блок элементов И 27, информационный вход 28 устройства, первый выход 29 блока управления устройства, вход 30 запуска устройства, вход 31 синхронизации устройства, второй 32, третий 33, четвертый 34 и пятый 35 выходы блока управления устройством, Блок предварительного округления

23образуют блоки 36 и 37 постоянной памяти, выход 38 и грулпа входов 39.

Блок управления устройством содержит RS-триггер 40, элементы И 41 и 42, элемент НЕ 43, двоичный счетчик 44 и одновибратор 45.

Устройство работает следующим образом.

В основу работы цифрового фильтра положена следующая формула:

у-г

-Ни с i-r,

где Y - результат фильтрации; и. - входная информация; Н - фильтровые коэффициенты,

В исходном состоянии блок элементов И 27 закрыт дпя прохода информации низким уровнем на первом выходе 29 блока управления устройством В. По отрицательному импульсу, цришедше му на вход 30 запуска устройства, RS-триггер 40 переходит в состояние I, а на выходе элемента НЕ 43 и, соответственно, на четвертом выходе 34 блока управления устройством 8 формируется положительный импульс, который обнуляет все регистры 1, 3, 14 - 16 и счетчики 12 и 44 устройства. Б результате этого на втором выходе 32 блока управления устройством 8 устанавливается начальный (нулевой) код. По окончании импульса запуска на первом выходе 29 блока управления устройством 8 появляется положительный уровень, открывающий группу элементов И 27 для прохода информации.

Отрицательные импульсы синхронизации являются стробами информации. Длительность этих импульсов определяется продолжительностью тракта обработки информации, состоящего из следующих этапов.

Этап I. Информация, прошедшая через блок элементов И 27, перекодируется в блоке 7 в код СОК. Параллельно осуществляет я выборка коэффициентов из блока 6 в соответствии с адресом, установленным на втором выходе 32 бло§а управления устройством 8.

Этап II. В блоке 5 производится умножение информации на числовое значение фильтрового коэффициента. Па5

10

раллельно на сумматоре 25 по модулю два определяется знак результата умножения .

Этап.III. Результат умножения округляется в блоке 23 предварительного округления. Параллельно в соответствии со знаком результата умножения, определяемым состоянием выхода сумматора 25 по модулю два (О соответствует знаку +, 1 - знаку -), открывается элемент И 17 или 18 и осуществляется выборка содержимого одного из регистров (1, 14) с помощью мультиплексора 11.

Этап IV. Округленный результат на сумматорах 2 и 22 складывается с числом, поступившим с выхода мультиплексора 1 1.

Этап V. В блоке 9 производится формирование сигналов переноса и поп-20 равок к старшим разрядам результата. Одновременно в соответствии с наличием (или отсутствием) переноса в старшие разряды открываются (или закры15

раций: запись поправки в регистр 15 или 16; сложение положительной и отрицательной поправок на двоичном сумматоре 13 и работа блока 9 по преобразованию старших разрядов результата, поступающих с двоичного реверсивного счетчика 12 в прямом или дополнительном двоичном коде в том случае, когда информация положительная или отрицательная, и поправки к старшим разрядам результата, поступающей с двоичного сумматора 13 в аналогичном виде. Переход RS-триггера 40 в состояние О закрывает элементы И 41 -и 42 и, таким образом, переводит устройство в ждущее состояние. Для начала нового цикла фильтрации снова необходим запуск устройства.

Формула изобретения

1. Цифровой фильтр, содержащий блок постоянной памяти коэффициентов и первый блок постоянной памяти, перваются) элементы И 19 или 20 и произ- вьй и второй адресные входы которого

водится выборка соответствующего результата сложения с помощью мультиплексора 10.

1

По положительному фронту сигнала синхронизации происходит изменение состояния двоичного счетчика 44 и формирование положительного фронта тактового сигнала, который, пройдя через открытый элемент И 17 или 18, производит запись информации в соот- ветствукяцие регистры поправки и регистр и осуществляет соответствующее изменение состояния двоичного реверсивного счетчика 12 (если имеется сигнал переноса в старшие разряды). Временной интервал, xapaктepизyюшJ й- ся высоким уровнем на входе синхронизации устройства 31, служит для смены информации на информационном вхо- де 28 устройства.

По отрицательному импульсу синхронизации последнего такта двоичный счётчик 44 формирует импульс переполнения, по окончании которого одновиб-50 ключен к первому входу сумматора по

ратор 45 вырабатывает другой тельный импульс, который, с одной стороны, перебрасывает в состояние О RS-триггер 40, а с другой стороны, своим положительным фронтом за- писывает информацию в регистр 3 результата. Длительность отрицательного импульса одновибратора должна обеспечить вьтолнение следующих one

раций: запись поправки в регистр 15 или 16; сложение положительной и отрицательной поправок на двоичном сумматоре 13 и работа блока 9 по преобразованию старших разрядов результата, поступающих с двоичного реверсивного счетчика 12 в прямом или дополнительном двоичном коде в том случае, когда информация положительная или отрицательная, и поправки к старшим разрядам результата, поступающей . с двоичного сумматора 13 в аналогичном виде. Переход RS-триггера 40 в состояние О закрывает элементы И 41 -и 42 и, таким образом, переводит устройство в ждущее состояние. Для начала нового цикла фильтрации снова необходим запуск устройства.

Формула изобретения

1. Цифровой фильтр, содержащий блок постоянной памяти коэффициентов и первый блок постоянной памяти, перподключены соответственно к первому выходу блока постоянной памяти коэффициентов и выходу второго блока постоянной памяти, третий блок постоянной памяти, блок синхронизации, первый регистр и регистр результата, выход которого является информационным выходом фильтра, отличающийся тем, что, с целью повьште- ния быстродействия, в него введены четвертый, пятый, шестой, седьмой и восьмой блоки постоянной памяти, блок элементов И, сумматор по модулю два, элемент НЕ, четыре элемента И, два мультиплексора, второй, третий и четвертый регистры, сумматор и реверсивный счетчик, первый выход блока синхронизации подключен к первому входу блока элементов И, выход которого подключен к адресному входу второго блока постоянной памяти, второй выход блока синхронизации подключен к адресному входу блока памяти коэффициентов, второй выход которого подмодулю два, выход которого подключен к управляющему входу первого мультиплексора, первому входу первого элемента И и входу элемента НЕ, выход которого подклк)чен к первому входу второго элемента И, выход которого подключен к тактовым входам первого и второго регистров и первому входу третьего элемента И, выход которого

подключен к суммирующему входу реверсивного счетчика, информационный выход которого подключен к первому адресному входу четвертого блока постоянной памяти, выход которого подключен к информационному входу регистра результата, третий выход блока синхронизации подключен к вторым входам первого и второго элементов И, выход первого элемента И подключен к тактовым входам третьего и четвертого регистров и первому ,входу четвертого элемента И, выход которого подключен к вычитающему входу реверсивного счетчика, вход об- купения которого объединен с входами обнуления регистра результата, первого, второго, третьего и четвертого регистров и подключен к четвертому выходу блока синхронизации, пятый вы ход которого подключен к тактовому входу регистра результата, выход первого блока постоянной памяти подключен к первому адресному входу пятого блока постоянной памяти и адресному входу шестого блока постоянной памяти, выход которого подключен к второму адресному входу пятого блока постоянной памяти, выход, которого подключен к первым адресным входам третьего и седьмого блоков постоянной памяти, выход третьего блока постоянной памяти подключен к первому информационному входу второго мульти

плексора и адресному входу седьмого блока постоянной памяти, первый и второй выходы которого подключены к информационным входам соответственно второго и третьего регистров, выходы которых подключены соответственно к первому и второму входам сумматора, выход которого подключен к второму адресному входу четвертого блока пос

5

0

5

0

5 0

тоянной памяти, выход седьмого блока постоянной памяти подключен к второму информационному входу второго мультиплексора, выход которого подключен к информационным входам первого и четвертого регистров, выходы которых подключены соответственно к первому и второму информационным входам первого коммутатора, выход которого подключен к вторым адресным входам третьего и седьмого блоков постоянной памяти, вход запуска и тактовый вход блока синхронизации являются соответственно входом запуска и входом синхронизации фильтра, входом знака информации, информационным входом которого являются соответственно второй вход сумматора по модулю два и второй вход блока элементов И,

2. Фильтр попЛ,отличаю- щ и. и с я тем, что блок синхронизации содержит RS-триггер, два элемента И, элемент НЕ, счетчик и одновибра- тор, выход которого является пятым выходом блока и подключен к R-входу RS-триггера, выход которого подключен к первым входам первого и второго элементов И, выход второго элемента И является третьим выходом блока и подключен к счетному входу счетчика, прямой выход которого является вторым выходом блока, а инверсный подключен к входу одновибратора, выход элемента НЕ подключен к входу обнуления счетчика и является четвертым выходом блока, первым выходом которого йвляется выход первого элемента И, первый вход которого объединен с входом элемента НЕ, S-входом RS-триггера и является входом запуска блока, тактовым входом которого является второй вход второго элемента И.

S.3

CocTaBHTejib А.Баранов Редактор Л.Пчолинская Техред М.ХоданичКорректор М.Демчик

- - - - - --. - -. --. - -- - . - - .-

Заказ 7052/43 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДВУМЕРНЫХ РАСПРЕДЕЛЕНИЙ СЛУЧАЙНЫХ ПРОЦЕССОВ | 2003 |

|

RU2253892C1 |

| Генератор случайных чисел | 1988 |

|

SU1599856A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1315999A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| СПЕЦПРОЦЕССОР ДЛЯ ЗАДАЧИ ВЫПОЛНИМОСТИ БУЛЕВЫХ ФОРМУЛ | 2017 |

|

RU2644505C1 |

| Программно-управляемый цифровой фильтр | 1987 |

|

SU1513475A1 |

| Устройство для обработки видеоинформации | 1990 |

|

SU1732354A1 |

| Адаптивный кодирующий преобразователь стационарных случайных процессов | 1980 |

|

SU960846A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

Изобретение относится к области цифровой обработки сигналов и может быть использовано для. вычисления .сумм произведений, дискретного преобразования Фурье, обработки речи и изображений в реальном масштабе времени. Цель изобретения - повьшение быстродействия. Поставленная цель достигается за счет того, что цифро- . вой фильтр состоит из блоков 2,5,6, 7,9,21,22 постоянной памяти, блока 27 элементов И, блока 6 постоянной

| IEEE Trans, on circuits and Systems, Vol | |||

| cas | |||

| Видоизменение прибора с двумя приемами для рассматривания проекционные увеличенных и удаленных от зрителя стереограмм | 1919 |

|

SU28A1 |

| Способ образования коричневых окрасок на волокне из кашу кубической и подобных производных кашевого ряда | 1922 |

|

SU32A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| IEEE Trans, on circuits and Systems ,Vol.- cas | |||

| Пишущая машина для тюркско-арабского шрифта | 1922 |

|

SU24A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-12-30—Публикация

1985-04-15—Подача